8XC196K*x*, 8XC196J*x*, 87C196CA Microcontroller Family User's Manual

Includes 8XC196KQ, 8XC196KR, 8XC196KS, 8XC196KT, 8XC196JQ, 8XC196JR, 8XC196JT, 8XC196JV, 87C196CA

intel

### 8XC196Kx, 8XC196Jx, 87C196CA Microcontroller Family User's Manual

Includes 8XC196KQ, 8XC196KR, 8XC196KS, 8XC196KT, 8XC196JQ, 8XC196JR, 8XC196JT, 8XC196JV, 87C196CA

June 1995 Order Number 272258-002

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

© INTEL CORPORATION, 1996

### CONTENTS

#### **CHAPTER 1**

| IDE TO THIS MANUAL                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MANUAL CONTENTS                                                       | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NOTATIONAL CONVENTIONS AND TERMINOLOGY                                | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RELATED DOCUMENTS                                                     | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ELECTRONIC SUPPORT SYSTEMS                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FaxBack Service                                                       | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Bulletin Board System (BBS)                                           | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1 How to Find MCS <sup>®</sup> 96 Microcontroller Files on the BBS  | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.2 How to Find ApBUILDER Software and Hypertext Documents on the BBS |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| World Wide Web                                                        | 1-10                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TECHNICAL SUPPORT                                                     | 1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PRODUCT LITERATURE                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TRAINING CLASSES                                                      | 1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                       | MANUAL CONTENTS<br>NOTATIONAL CONVENTIONS AND TERMINOLOGY<br>RELATED DOCUMENTS<br>ELECTRONIC SUPPORT SYSTEMS<br>FaxBack Service<br>Bulletin Board System (BBS)<br>2.1 How to Find MCS <sup>®</sup> 96 Microcontroller Files on the BBS<br>2.2 How to Find MCS <sup>®</sup> 96 Microcontroller Files on the BBS<br>2.2 How to Find ApBUILDER Software and Hypertext Documents on the BBS<br>CompuServe Forums<br>World Wide Web<br>TECHNICAL SUPPORT |

#### CHAPTER 2

#### ARCHITECTURAL OVERVIEW

| 2.1   | TYPICAL APPLICATIONS                                 | 2-1  |

|-------|------------------------------------------------------|------|

| 2.2   | DEVICE FEATURES                                      | 2-2  |

| 2.3   | BLOCK DIAGRAM                                        | 2-2  |

| 2.3.1 | CPU Control                                          | 2-4  |

| 2.3.2 | Register File                                        | 2-4  |

| 2.3.3 | ······································               |      |

| 2.3.  |                                                      |      |

| 2.3.  |                                                      | -    |

| 2.3.4 |                                                      |      |

| 2.3.5 |                                                      |      |

| 2.4   | INTERNAL TIMING                                      | 2-7  |

| 2.5   | INTERNAL PERIPHERALS                                 | 2-8  |

| 2.5.1 | I/O Ports                                            | 2-9  |

| 2.5.2 | Serial I/O (SIO) Port                                | 2-9  |

| 2.5.3 | Synchronous Serial I/O (SSIO) Port                   | 2-9  |

| 2.5.4 | Slave Port (8XC196Kx Only)                           | 2-10 |

| 2.5.5 | Event Processor Array (EPA) and Timer/Counters       | 2-10 |

| 2.5.6 | Analog-to-digital Converter                          | 2-11 |

| 2.5.7 | Watchdog Timer                                       | 2-11 |

| 2.5.8 | CAN Serial Communications Controller (87C196CA Only) | 2-11 |

| 2.6   | SPECIAL OPERATING MODES                              | 2-11 |

| 2.6.1 | Reducing Power Consumption                           | 2-12 |

|       |                                                      |      |

# intel

| 2.6.2 | 2 Testing the Printed Circuit Board                          | 2-12 |

|-------|--------------------------------------------------------------|------|

| 2.6.3 | Programming the Nonvolatile Memory                           | 2-12 |

| 2.7   | DESIGN CONSIDERATIONS FOR 87C196CA DEVICES                   | 2-13 |

| 2.8   | DESIGN CONSIDERATIONS FOR 8XC196JQ, JR, JT, AND JV DEVICES   | 2-14 |

|       |                                                              |      |

| CHAP  | TER 3<br>OGRAMMING CONSIDERATIONS                            |      |

| 3.1   | OVERVIEW OF THE INSTRUCTION SET                              | 2.1  |

| 3.1.1 |                                                              |      |

| 3.1.1 | •                                                            |      |

| 3.1.2 | -                                                            |      |

| 3.1.4 |                                                              |      |

| 3.1.5 | •                                                            |      |

| 3.1.6 |                                                              |      |

| 3.1.7 |                                                              |      |

| 3.1.8 |                                                              |      |

| 3.1.9 |                                                              |      |

| 3.1.1 |                                                              |      |

| 3.2   | ADDRESSING MODES                                             |      |

| 3.2.1 | Direct Addressing                                            | 3-6  |

| 3.2.2 | Immediate Addressing                                         | 3-6  |

| 3.2.3 | Indirect Addressing                                          | 3-6  |

| 3.2.  |                                                              |      |

| 3.2.  |                                                              |      |

| 3.2.4 | ····· 5                                                      |      |

| 3.2.  |                                                              |      |

|       | .4.2 Long-indexed Addressing<br>.4.3 Zero-indexed Addressing |      |

| 3.3   | ASSEMBLY LANGUAGE ADDRESSING MODE SELECTIONS                 |      |

| 3.3.1 |                                                              |      |

| 3.3.2 | 5                                                            |      |

| 3.4   | SOFTWARE STANDARDS AND CONVENTIONS                           |      |

| 3.4.1 |                                                              |      |

| 3.4.2 |                                                              |      |

| 3.4.3 |                                                              |      |

| 3.5   | SOFTWARE PROTECTION FEATURES AND GUIDELINES                  |      |

| 0.0   |                                                              |      |

|       |                                                              |      |

#### CHAPTER 4 MEMORY PARTITIONS

| 4.1   | MEMORY PARTITIONS                  | 4-1 |

|-------|------------------------------------|-----|

|       | External Devices (Memory or I/O)   |     |

| 4.1.2 | Program and Special-purpose Memory | 4-1 |

| 4.1.3 | Program Memory                     | 4-3 |

| 4.1.4 | Special-purpose Memory             | 4-3 |

# intel

| 4.1.4.1 | Reserved Memory Locations                   | 4-4  |

|---------|---------------------------------------------|------|

| 4.1.4.2 |                                             |      |

| 4.1.4.3 |                                             |      |

| 4.1.4.4 |                                             |      |

| 4.1.5   | Special-function Registers (SFRs)           | 4-5  |

| 4.1.5.1 | Memory-mapped SFRs                          | 4-5  |

| 4.1.5.2 |                                             |      |

| 4.1.6   | Internal RAM (Code RAM)                     | 4-10 |

| 4.1.7   | Register File                               | 4-10 |

| 4.1.7.1 | General-purpose Register RAM                | 4-12 |

| 4.1.7.2 | Stack Pointer (SP)                          | 4-12 |

| 4.1.7.3 |                                             |      |

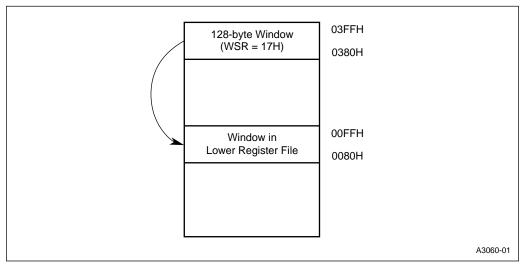

| 4.2 W   | INDOWING                                    | 4-13 |

| 4.2.1   | Selecting a Window                          | 4-14 |

| 4.2.2   | Addressing a Location Through a Window      | 4-17 |

| 4.2.2.1 | 32-byte Windowing Example                   | 4-20 |

| 4.2.2.2 | 64-byte Windowing Example                   | 4-20 |

| 4.2.2.3 | 128-byte Windowing Example                  | 4-20 |

| 4.2.2.4 |                                             |      |

| 4.2.2.5 | Using the Linker Locator to Set Up a Window | 4-21 |

| 4.2.3   | Windowing and Addressing Modes              |      |

|         |                                             |      |

#### **CHAPTER 5**

### STANDARD AND PTS INTERRUPTS

| 5.1   | OVERVIEW                                              | 5-1         |

|-------|-------------------------------------------------------|-------------|

| 5.2   | INTERRUPT SIGNALS AND REGISTERS                       | 5-3         |

| 5.3   | INTERRUPT SOURCES AND PRIORITIES                      | 5-4         |

| 5.3.1 | Special Interrupts                                    | .5-6        |

| 5.3.  | 1.1 Unimplemented Opcode                              | .5-6        |

| 5.3.  | 1.2 Software Trap                                     | .5-6        |

| 5.3.  | 1.3 NMI                                               | .5-6        |

| 5.3.2 | External Interrupt Pins                               | .5-6        |

| 5.3.3 | Multiplexed Interrupt Sources                         | .5-7        |

| 5.3.4 | End-of-PTS Interrupts                                 | .5-7        |

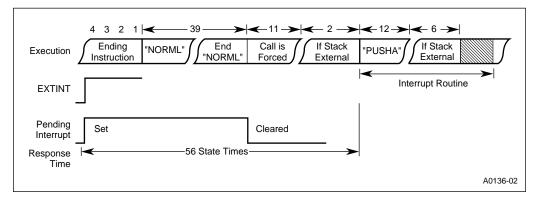

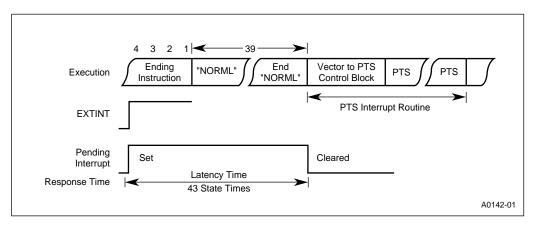

| 5.4   | INTERRUPT LATENCY                                     | 5-7         |

| 5.4.1 | Situations that Increase Interrupt Latency            | .5-8        |

| 5.4.2 | Calculating Latency                                   | .5-9        |

| 5.4.  |                                                       |             |

| 5.4.  | 2.2 PTS Interrupt Latency5                            | 5-10        |

| 5.5   | PROGRAMMING THE INTERRUPTS 5                          | 5-11        |

| 5.5.1 | Programming the Multiplexed Interrupts5               |             |

| 5.5.2 | Modifying Interrupt Priorities5                       | 5-14        |

| 5.5.3 | Determining the Source of an Interrupt5               | 5-16        |

| 5.5.  | 3.1 Determining the Source of Multiplexed Interrupts5 | <u>5-16</u> |

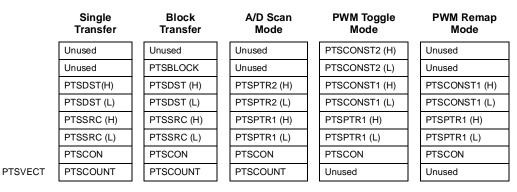

| 5.6   | INITIALIZING THE PTS CONTROL BLOCKS 5                 | 5-18        |

# intel

| 5.6.1 Specifying the PTS Count    | 5-19 |

|-----------------------------------|------|

| 5.6.2 Selecting the PTS Mode      | 5-21 |

| 5.6.3 Single Transfer Mode        | 5-21 |

| 5.6.4 Block Transfer Mode         |      |

| 5.6.5 A/D Scan Mode               |      |

| 5.6.5.1 A/D Scan Mode Cycles      | 5-29 |

| 5.6.5.2 A/D Scan Mode Example 1   |      |

| 5.6.5.3 A/D Scan Mode Example 2   |      |

| 5.6.6 PWM Modes                   | 5-31 |

| 5.6.6.1 PWM Toggle Mode Example . | 5-32 |

| 5.6.6.2 PWM Remap Mode Example .  |      |

#### **CHAPTER 6**

#### I/O PORTS

| 6.1   | I/O PORTS OVERVIEW                                       |      |

|-------|----------------------------------------------------------|------|

| 6.2   | INPUT-ONLY PORT 0                                        | 6-1  |

| 6.2.1 | Standard Input-only Port Operation                       | 6-2  |

| 6.2.2 | Standard Input-only Port Considerations                  | 6-3  |

| 6.3   | BIDIRECTIONAL PORTS 1, 2, 5, AND 6                       |      |

| 6.3.1 | Bidirectional Port Operation                             | 6-6  |

| 6.3.2 | Bidirectional Port Pin Configurations                    | 6-10 |

| 6.3.3 | Bidirectional Port Pin Configuration Example             |      |

| 6.3.4 | Bidirectional Port Considerations                        | 6-12 |

| 6.3.5 | Design Considerations for External Interrupt Inputs      | 6-15 |

| 6.4   | BIDIRECTIONAL PORTS 3 AND 4 (ADDRESS/DATA BUS)           |      |

| 6.4.1 | Bidirectional Ports 3 and 4 (Address/Data Bus) Operation | 6-16 |

| 6.4.2 | Using Ports 3 and 4 as I/O                               | 6-18 |

| 6.4.3 | Design Considerations for Ports 3 and 4                  | 6-19 |

#### CHAPTER 7

### SERIAL I/O (SIO) PORT

| 7.1   | SERIAL I/O (SIO) PORT FUNCTIONAL OVERVIEW | 7-1 |

|-------|-------------------------------------------|-----|

| 7.2   | SERIAL I/O PORT SIGNALS AND REGISTERS     | 7-2 |

| 7.3   | SERIAL PORT MODES                         | 7-4 |

| 7.3.1 | Synchronous Mode (Mode 0)                 | 7-4 |

| 7.3.2 | Asynchronous Modes (Modes 1, 2, and 3)    | 7-6 |

| 7.3.  | 2.1 Mode 1                                | 7-6 |

| 7.3.  | 2.2 Mode 2                                | 7-7 |

| 7.3.  | 2.3 Mode 3                                | 7-7 |

| 7.3.  |                                           | 7-7 |

| 7.3.  | 2.5 Multiprocessor Communications         | 7-8 |

| 7.4   | PROGRAMMING THE SERIAL PORT               | 7-8 |

| 7.4.1 | Configuring the Serial Port Pins          | 7-8 |

| 7.4.2 | Programming the Control Register          | 7-8 |

#### CONTENTS

| 7.4.3 | Programming the Baud Rate and Clock Source            | 7-10 |

|-------|-------------------------------------------------------|------|

| 7.4.4 | Enabling the Serial Port Interrupts                   | 7-12 |

| 7.4.5 | Determining Serial Port Status                        | 7-13 |

| 7.5   | PROGRAMMING EXAMPLE USING AN INTERRUPT-DRIVEN ROUTINE |      |

#### **CHAPTER 8**

#### SYNCHRONOUS SERIAL I/O (SSIO) PORT

| 8.1   | SYNCHRONOUS SERIAL I/O (SSIO) PORT FUNCTIONAL OVERVIEW         | . 8-1 |

|-------|----------------------------------------------------------------|-------|

| 8.2   | SSIO PORT SIGNALS AND REGISTERS                                | . 8-2 |

| 8.3   | SSIO OPERATION                                                 | . 8-3 |

| 8.4   | SSIO HANDSHAKING                                               | . 8-6 |

| 8.4.1 | SSIO Handshaking Configuration                                 |       |

| 8.4.2 | SSIO Handshaking Operation                                     | 8-7   |

| 8.5   | PROGRAMMING THE SSIO PORT                                      | . 8-9 |

| 8.5.1 | Configuring the SSIO Port Pins                                 | 8-9   |

| 8.5.2 | Programming the Baud Rate and Enabling the Baud-rate Generator | 8-9   |

| 8.5.3 | Controlling the Communications Mode and Handshaking            | 8-10  |

| 8.5.4 | Enabling the SSIO Interrupts                                   |       |

| 8.5.5 | Determining SSIO Port Status                                   | 8-13  |

| 8.6   | PROGRAMMING CONSIDERATIONS                                     | 8-13  |

| 8.7   | PROGRAMMING EXAMPLE                                            | 8-15  |

|       |                                                                |       |

#### CHAPTER 9 SLAVE PORT

| -     |                                                       |      |

|-------|-------------------------------------------------------|------|

| 9.1   | SLAVE PORT FUNCTIONAL OVERVIEW                        |      |

| 9.2   | SLAVE PORT SIGNALS AND REGISTERS                      |      |

| 9.3   | HARDWARE CONNECTIONS                                  |      |

| 9.4   | SLAVE PORT MODES                                      |      |

| 9.4.1 | Standard Slave Mode Example                           | 9-8  |

| 9.4.  |                                                       |      |

| 9.4.  | 1.2 Slave Device Program                              | 9-9  |

| 9.4.  | -                                                     |      |

| 9.4.2 | Shared Memory Mode Example (8XC196KS and KT only)     | 9-11 |

| 9.4.  |                                                       |      |

| 9.4.  | -                                                     |      |

| 9.4.  |                                                       |      |

| 9.5   | CONFIGURING THE SLAVE PORT                            | 9-14 |

| 9.5.1 | Programming the Slave Port Control Register (SLP_CON) | 9-14 |

| 9.5.2 | Enabling the Slave Port Interrupts                    | 9-16 |

| 9.6   | DETERMINING SLAVE PORT STATUS                         | 9-16 |

| 9.7   | USING STATUS BITS TO SYNCHRONIZE MASTER AND SLAVE     | 9-16 |

|       |                                                       |      |

#### **CHAPTER 10**

| EVENT PROCESSOR ARRAY (EPA) |  |

|-----------------------------|--|

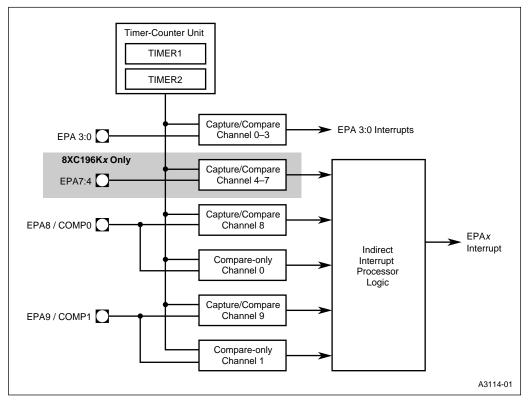

| 10.1 EPA FUNCTIONAL OVERVIEW                                       | 10-1         |

|--------------------------------------------------------------------|--------------|

| 10.2 EPA AND TIMER/COUNTER SIGNALS AND REGISTERS                   | 10-2         |

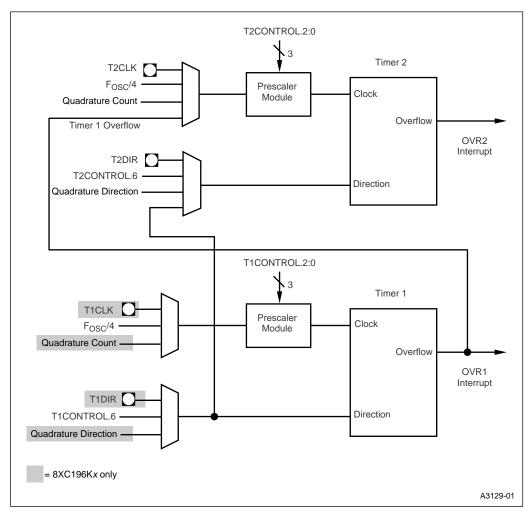

| 10.3 TIMER/COUNTER FUNCTIONAL OVERVIEW                             | 10-6         |

| 10.3.1 Cascade Mode (Timer 2 Only)                                 |              |

| 10.3.2 Quadrature Clocking Mode                                    | 10-7         |

| 10.4 EPA CHANNEL FUNCTIONAL OVERVIEW                               |              |

| 10.4.1 Operating in Capture Mode                                   |              |

| 10.4.1.1 Handling EPA Overruns                                     |              |

| 10.4.2 Operating in Compare Mode                                   |              |

| 10.4.2.1 Generating a Low-speed PWM Output                         |              |

| 10.4.2.2 Generating a Medium-speed PWM Output                      |              |

| 10.4.2.3 Generating a High-speed PWM Output                        |              |

| 10.4.2.4 Generating the Highest-speed PWM Output                   |              |

| 10.5 PROGRAMMING THE EPA AND TIMER/COUNTERS                        | 10-17        |

| 10.5.1 Configuring the EPA and Timer/Counter Port Pins             |              |

| 10.5.2 Programming the Timers                                      | 10-17        |

| 10.5.3 Programming the Capture/Compare Channels                    |              |

| 10.5.4 Programming the Compare-only Channels                       |              |

| 10.6 ENABLING THE EPA INTERRUPTS                                   | 10-26        |

| 10.7 DETERMINING EVENT STATUS                                      | 10-28        |

| 10.8 SERVICING THE MULTIPLEXED EPA INTERRUPT WITH SO               | FTWARE 10-29 |

| 10.8.1 Using the TIJMP Instruction to Reduce Interrupt Service Ove | erhead10-31  |

| 10.9 PROGRAMMING EXAMPLES FOR EPA CHANNELS                         | 10-33        |

| 10.9.1 EPA Compare Event Program                                   |              |

| 10.9.2 EPA Capture Event Program                                   |              |

| 10.9.3 EPA PWM Output Program                                      |              |

| · -                                                                |              |

#### CHAPTER 11

#### ANALOG-TO-DIGITAL CONVERTER

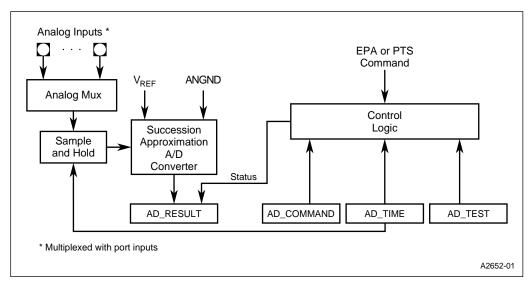

| 11.1  | A/D CONVERTER FUNCTIONAL OVERVIEW                                    | 11-1  |

|-------|----------------------------------------------------------------------|-------|

| 11.2  | A/D CONVERTER SIGNALS AND REGISTERS                                  | 11-2  |

| 11.3  | A/D CONVERTER OPERATION                                              | 11-3  |

| 11.4  | PROGRAMMING THE A/D CONVERTER                                        | 11-4  |

| 11.4. | 1 Programming the A/D Test Register                                  | 11-5  |

| 11.4. | 2 Programming the A/D Result Register (for Threshold Detection Only) | 11-6  |

| 11.4. | 3 Programming the A/D Time Register                                  | 11-6  |

| 11.4. | 4 Programming the A/D Command Register                               | 11-8  |

| 11.4. | 5 Enabling the A/D Interrupt                                         | 11-9  |

| 11.5  | DETERMINING A/D STATUS AND CONVERSION RESULTS                        | 11-9  |

| 11.6  | DESIGN CONSIDERATIONS                                                | 11-10 |

| 11.6. | 1 Designing External Interface Circuitry                             | 11-11 |

|       |                                                                      |       |

#### CONTENTS

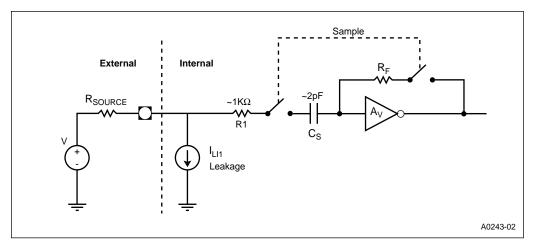

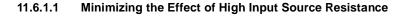

| 11.6.1.1  | Minimizing the Effect of High Input Source Resistance | 11-12 |

|-----------|-------------------------------------------------------|-------|

| 11.6.1.2  | Suggested A/D Input Circuit                           | 11-13 |

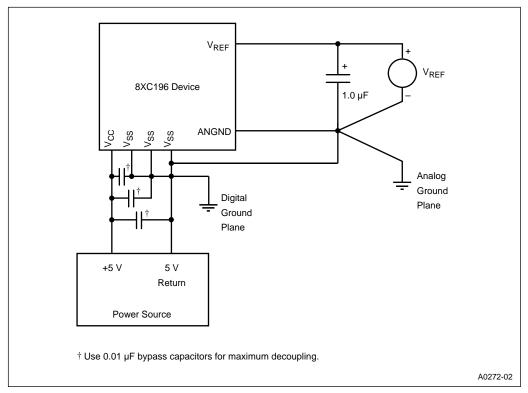

| 11.6.1.3  | Analog Ground and Reference Voltages                  | 11-13 |

|           | Using Mixed Analog and Digital Inputs                 |       |

| 11.6.2 Ui | nderstanding A/D Conversion Errors                    | 11-14 |

#### CHAPTER 12

#### CAN SERIAL COMMUNICATIONS CONTROLLER

| 12.1 CAN FUNCTIONAL OVERVIEW                              | 12-1  |

|-----------------------------------------------------------|-------|

| 12.2 CAN CONTROLLER SIGNALS AND REGISTERS                 | 12-3  |

| 12.3 CAN CONTROLLER OPERATION                             | 12-4  |

| 12.3.1 Address Map                                        | 12-5  |

| 12.3.2 Message Objects                                    |       |

| 12.3.2.1 Receive and Transmit Priorities                  | 12-6  |

| 12.3.2.2 Message Acceptance Filtering                     |       |

| 12.3.3 Message Frames                                     | 12-7  |

| 12.3.4 Error Detection and Management Logic               |       |

| 12.3.5 Bit Timing                                         |       |

| 12.3.5.1 Bit Timing Equations                             |       |

| 12.4 CONFIGURING THE CAN CONTROLLER                       |       |

| 12.4.1 Programming the CAN Control (CAN_CON) Register     | 12-13 |

| 12.4.2 Programming the Bit Timing 0 (CAN_BTIME0) Register | 12-15 |

| 12.4.3 Programming the Bit Timing 1 (CAN_BTIME1) Register | 12-16 |

| 12.4.4 Programming a Message Acceptance Filter            | 12-18 |

| 12.5 CONFIGURING MESSAGE OBJECTS                          | 12-20 |

| 12.5.1 Specifying a Message Object's Configuration        | 12-21 |

| 12.5.2 Programming the Message Object Identifier          | 12-22 |

| 12.5.3 Programming the Message Object Control Registers   | 12-23 |

| 12.5.3.1 Message Object Control Register 0                | 12-23 |

| 12.5.3.2 Message Object Control Register 1                | 12-23 |

| 12.5.4 Programming the Message Object Data                | 12-23 |

| 12.6 ENABLING THE CAN INTERRUPTS                          | 12-29 |

| 12.7 DETERMINING THE CAN CONTROLLER'S INTERRUPT STATUS    | 12-32 |

| 12.8 FLOW DIAGRAMS                                        | 12-35 |

| 12.9 DESIGN CONSIDERATIONS                                | 12-41 |

| 12.9.1 Hardware Reset                                     | 12-41 |

| 12.9.2 Software Initialization                            | 12-41 |

| 12.9.3 Bus-off State                                      | 12-41 |

#### **CHAPTER 13**

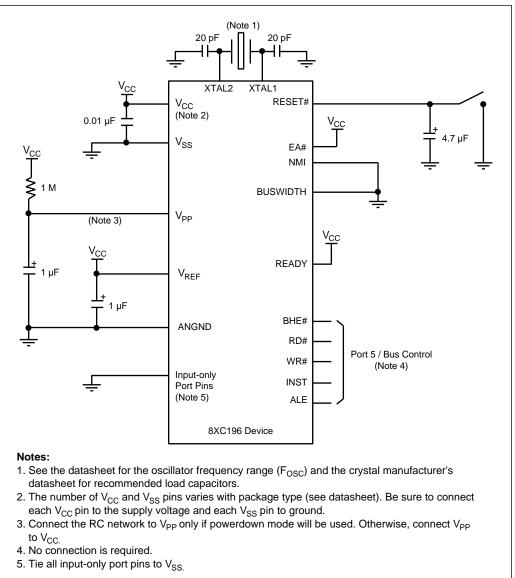

#### MINIMUM HARDWARE CONSIDERATIONS

| 13.1   | MINIMUM CONNEC      | CTIONS   |    | -1 |

|--------|---------------------|----------|----|----|

| 13.1.1 | Unused Inputs       |          | 13 | -2 |

| 13.1.2 | 2 I/O Port Pin Conr | nections | 13 | -2 |

# intel

| 13.2 A | PPLYING AND REMOVING POWER                                | 13-4  |

|--------|-----------------------------------------------------------|-------|

| 13.3 N | IOISE PROTECTION TIPS                                     | 13-4  |

| 13.4 P | ROVIDING THE CLOCK                                        | 13-5  |

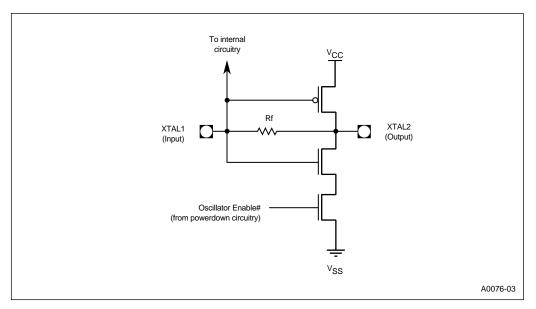

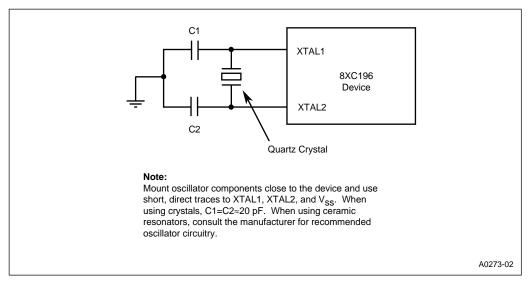

| 13.4.1 | Using the On-chip Oscillator                              | 13-5  |

| 13.4.2 | Using a Ceramic Resonator Instead of a Crystal Oscillator | 13-7  |

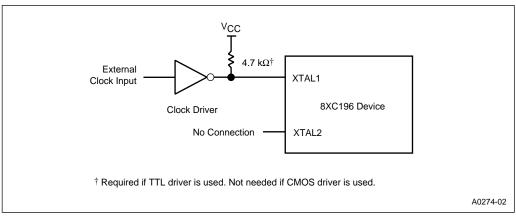

| 13.4.3 | Providing an External Clock Source                        | 13-7  |

|        | ESETTING THE DEVICE                                       |       |

|        | Generating an External Reset                              |       |

|        | Issuing the Reset (RST) Instruction                       |       |

| 13.5.3 | Issuing an Illegal IDLPD Key Operand                      |       |

| 13.5.4 |                                                           |       |

| 13.5.5 | Detecting Oscillator Failure                              | 13-12 |

#### **CHAPTER 14**

| 14.1 SPECIAL OPERATING MODE SIGNALS AND REGISTERS                              | 14-1 |

|--------------------------------------------------------------------------------|------|

| 14.2 REDUCING POWER CONSUMPTION                                                | 14-3 |

| 14.3 IDLE MODE                                                                 | 14-3 |

| 14.4 POWERDOWN MODE                                                            | 14-4 |

| 14.4.1 Enabling and Disabling Powerdown Mode                                   | 14-4 |

| 14.4.2 Entering Powerdown Mode                                                 | 14-5 |

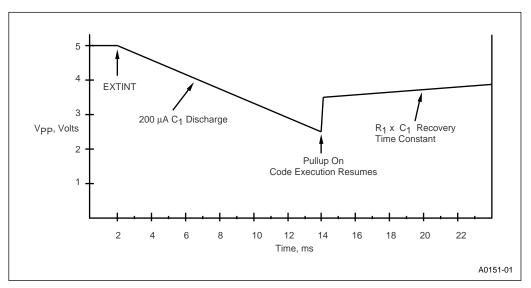

| 14.4.3 Exiting Powerdown Mode                                                  | 14-5 |

| 14.4.3.1Driving the V <sub>pp</sub> Pin Low14.4.3.2Generating a Hardware Reset | 14-5 |

| 14.4.3.2 Generating a Hardware Reset                                           | 14-6 |

| 14.4.3.3 Asserting the External Interrupt Signal                               | 14-6 |

| 14.4.3.4 Selecting R <sub>1</sub> and C <sub>1</sub>                           | 14-7 |

| 14.5 ONCE MODE                                                                 | 14-9 |

| 14.5.1 Entering and Exiting ONCE Mode                                          | 14-9 |

| 14.6 RESERVED TEST MODES 14                                                    | 4-10 |

#### **CHAPTER 15**

#### INTERFACING WITH EXTERNAL MEMORY

| EXTERNAL MEMORY INTERFACE SIGNALS                   | 15-1                                                                                               |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|

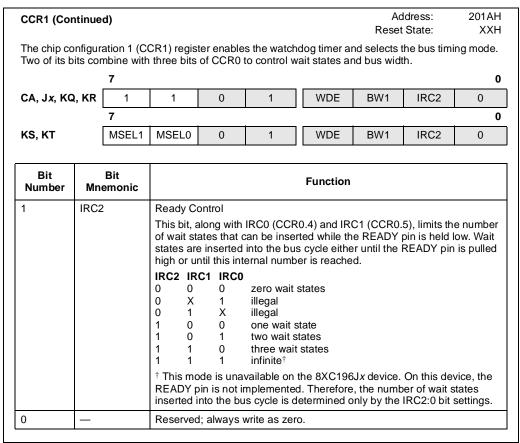

| CHIP CONFIGURATION REGISTERS AND CHIP CONFIGURAT    | ION BYTES 15-4                                                                                     |

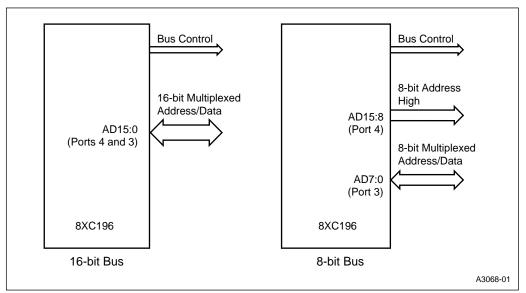

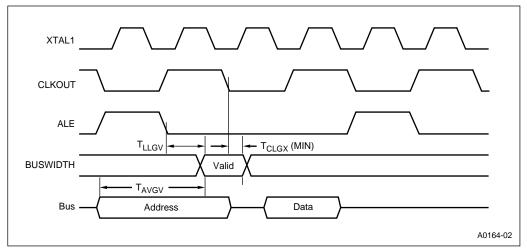

| BUS WIDTH AND MULTIPLEXING                          | 15-8                                                                                               |

| 3.1 Timing Requirements for BUSWIDTH                | 15-10                                                                                              |

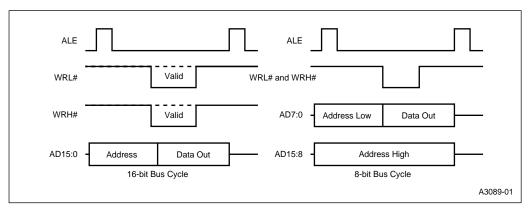

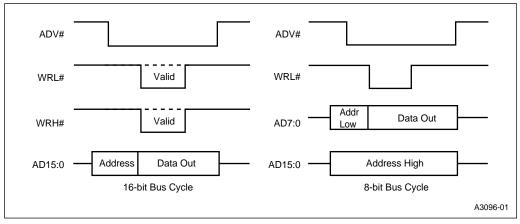

| 3.2 16-bit Bus Timings                              | 15-11                                                                                              |

| 3.3 8-bit Bus Timings                               |                                                                                                    |

| WAIT STATES (READY CONTROL)                         | 15-14                                                                                              |

| BUS-HOLD PROTOCOL (8XC196KQ, KR, KS, KT ONLY)       | 15-17                                                                                              |

| 5.1 Enabling the Bus-hold Protocol (8XC196Kx Only)  | 15-18                                                                                              |

| 5.2 Disabling the Bus-hold Protocol (8XC196Kx Only) | 15-19                                                                                              |

| 5.3 Hold Latency (8XC196Kx Only)                    |                                                                                                    |

| 3.<br>3.<br>5.                                      | <ul> <li>CHIP CONFIGURATION REGISTERS AND CHIP CONFIGURAT<br/>BUS WIDTH AND MULTIPLEXING</li></ul> |

#### CONTENTS

| 15.5.4  | Regaining Bus Control (8XC196Kx Only)                   | 15-20 |

|---------|---------------------------------------------------------|-------|

| 15.6 Bl | US-CONTROL MODES                                        | 15-20 |

| 15.6.1  | Standard Bus-control Mode                               |       |

| 15.6.2  | Write Strobe Mode                                       |       |

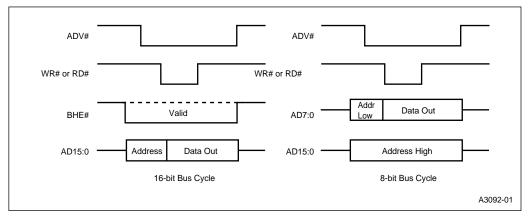

| 15.6.3  | Address Valid Strobe Mode                               |       |

| 15.6.4  | Address Valid with Write Strobe Mode                    |       |

| 15.7 Bl | US TIMING MODES (8XC196KS, KT ONLY)                     | 15-30 |

| 15.7.1  | Mode 3, Standard Mode                                   |       |

| 15.7.2  | Mode 0, Standard Timing with One Automatic Wait State . |       |

| 15.7.3  | Mode 1, Long Read/Write Mode                            |       |

| 15.7.4  | Mode 2, Long Read/Write with Early Address              |       |

| 15.7.5  | Design Considerations                                   |       |

| 15.8 S  | YSTEM BUS AC TIMING SPECIFICATIONS                      | 15-36 |

|         |                                                         |       |

#### CHAPTER 16

#### PROGRAMMING THE NONVOLATILE MEMORY

| 16.1 PR  | OGRAMMING METHODS                                           | 16-2  |

|----------|-------------------------------------------------------------|-------|

| 16.2 OT  | PROM MEMORY MAP                                             | 16-2  |

| 16.3 SE  | CURITY FEATURES                                             | 16-3  |

| 16.3.1   | Controlling Access to Internal Memory                       |       |

| 16.3.1.  |                                                             |       |

| 16.3.1.2 | 2 Controlling Access to the OTPROM During Programming Modes | 16-5  |

|          | Controlling Fetches from External Memory                    |       |

| 16.3.3   | Enabling the Oscillator Failure Detection Circuitry         | 16-8  |

| 16.4 PR  | OGRAMMING PULSE WIDTH                                       | 16-8  |

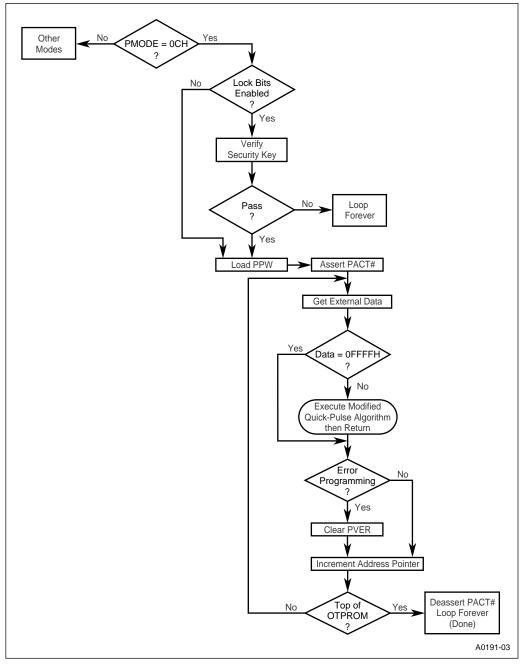

| 16.5 MC  | DDIFIED QUICK-PULSE ALGORITHM                               | 16-10 |

| 16.6 PR  | OGRAMMING MODE PINS                                         | 16-11 |

| 16.7 EN  | ITERING PROGRAMMING MODES                                   | 16-14 |

| 16.7.1   | Selecting the Programming Mode                              | 16-14 |

| 16.7.2   | Power-up and Power-down Sequences                           | 16-14 |

| 16.7.2.  |                                                             |       |

| 16.7.2.  | 2 Power-down Sequence                                       | 16-15 |

| 16.8 SL  | AVE PROGRAMMING MODE                                        | 16-15 |

| 16.8.1   | Reading the Signature Word and Programming Voltages         | 16-16 |

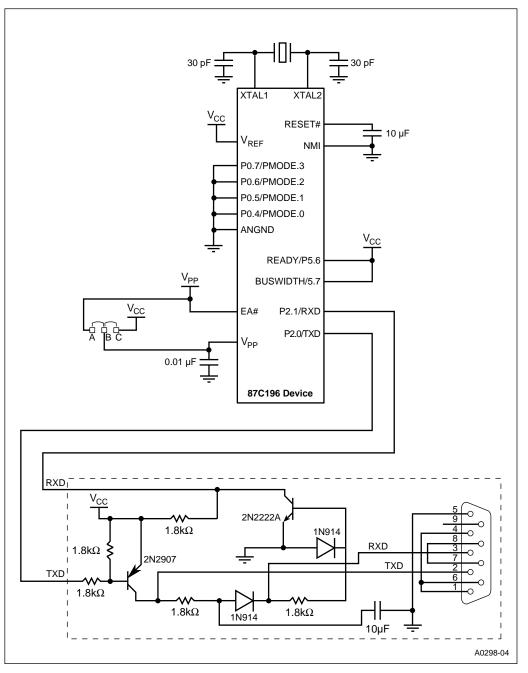

| 16.8.2   | Slave Programming Circuit and Memory Map                    | 16-16 |

| 16.8.3   | Operating Environment                                       | 16-18 |

| 16.8.4   | Slave Programming Routines                                  | 16-20 |

| 16.8.5   | Timing Mnemonics                                            | 16-25 |

| 16.9 AL  | ITO PROGRAMMING MODE                                        | 16-26 |

| 16.9.1   | Auto Programming Circuit and Memory Map                     | 16-26 |

|          | Operating Environment                                       |       |

| 16.9.3   | Auto Programming Routine                                    | 16-28 |

| 16.9.4   | Auto Programming Procedure                                  | 16-30 |

|          |                                                             |       |

# intel

| 16.9.5   | ROM-dump Mode                                            | 16-31 |

|----------|----------------------------------------------------------|-------|

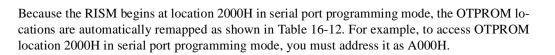

| 16.10 SI | ERIAL PORT PROGRAMMING MODE                              | 16-32 |

| 16.10.1  | Serial Port Programming Circuit and Memory Map           |       |

| 16.10.2  | Changing Serial Port Programming Defaults                | 16-34 |

| 16.10.3  | Executing Programs from Internal RAM                     | 16-35 |

| 16.10.4  | Reduced Instruction Set Monitor (RISM)                   | 16-35 |

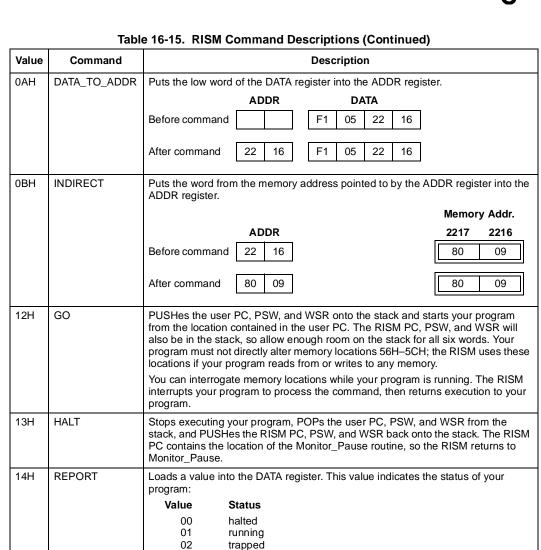

| 16.10.5  | RISM Command Descriptions                                | 16-36 |

|          | RISM Command Examples                                    |       |

| 16.10.   | 6.1 Example 1 — Programming the PPW                      |       |

| 16.10.   | 6.2 Example 2 — Reading OTPROM Contents                  |       |

| 16.10.   | 6.3 Example 3 — Loading a Program into Internal RAM      |       |

| 16.10.   | 6.4 Example 4 — Setting the PC and Executing the Program |       |

| 16.10.   | 6.5 Writing to OTPROM with Examples 3 and 4              |       |

| 16.11 R  | UN-TIME PROGRAMMING                                      | 16-44 |

#### APPENDIX A INSTRUCTION SET REFERENCE

#### APPENDIX B

| SIG | NAL DESCRIPTIONS                |      |

|-----|---------------------------------|------|

| B.1 | SIGNAL NAME CHANGES             | B-1  |

| B.2 | FUNCTIONAL GROUPINGS OF SIGNALS | B-1  |

| B.3 | SIGNAL DESCRIPTIONS             | B-8  |

| B.4 | DEFAULT CONDITIONS E            | 3-19 |

|     |                                 |      |

#### APPENDIX C REGISTERS

GLOSSARY

INDEX

| Figure |                                                        | Page |

|--------|--------------------------------------------------------|------|

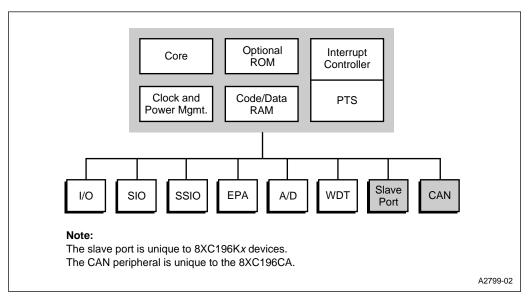

| 2-1    | 8XC196Kx Block Diagram                                 | 2-3  |

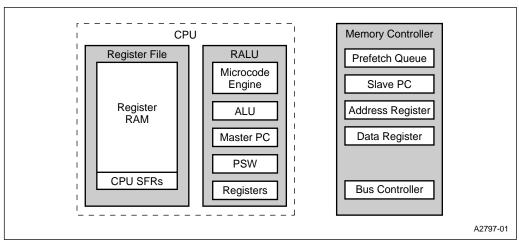

| 2-2    | Block Diagram of the Core                              |      |

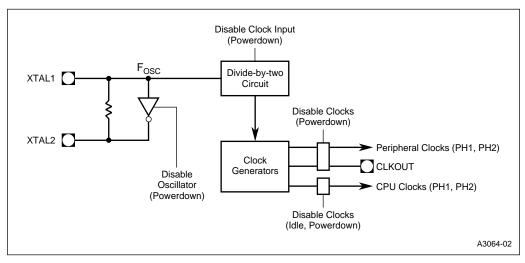

| 2-3    | Clock Circuitry                                        | 2-7  |

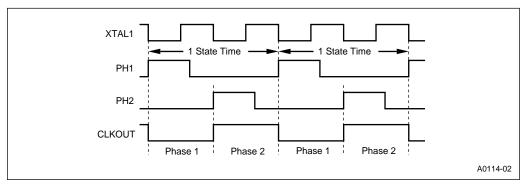

| 2-4    | Internal Clock Phases                                  | 2-8  |

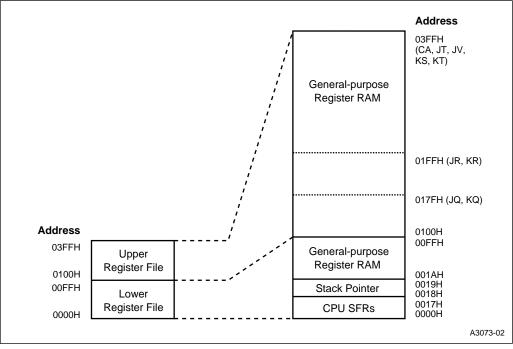

| 4-1    | Register File Memory Map                               | 4-11 |

| 4-2    | Windowing                                              | 4-14 |

| 4-3    | Window Selection Register (WSR)                        | 4-15 |

| 5-1    | Flow Diagram for PTS and Standard Interrupts           | 5-2  |

| 5-2    | Standard Interrupt Response Time                       | 5-9  |

| 5-3    | PTS Interrupt Response Time                            | 5-10 |

| 5-4    | PTS Select (PTSSEL) Register                           | 5-12 |

| 5-5    | Interrupt Mask (INT_MASK) Register                     |      |

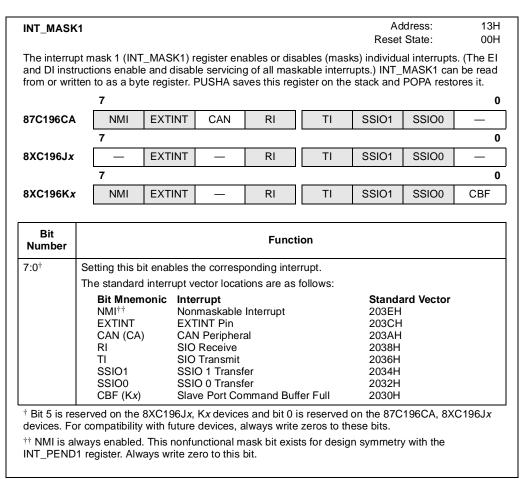

| 5-6    | Interrupt Mask 1 (INT_MASK1) Register                  | 5-14 |

| 5-7    | Interrupt Pending (INT_PEND) Register                  |      |

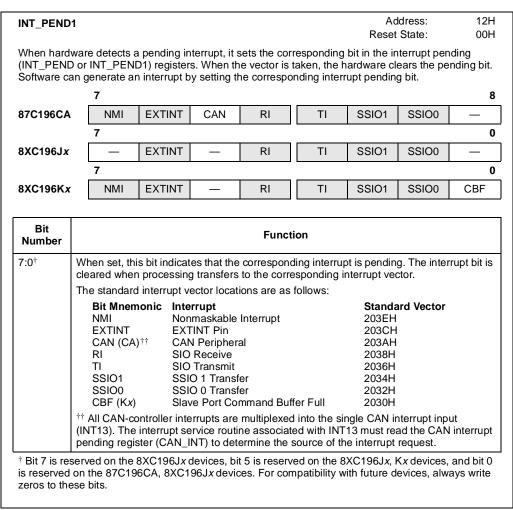

| 5-8    | Interrupt Pending 1 (INT_PEND1) Register               |      |

| 5-9    | PTS Control Blocks                                     |      |

| 5-10   | PTS Service (PTSSRV) Register                          |      |

| 5-11   | PTS Mode Selection Bits (PTSCON Bits 7:5)              |      |

| 5-12   | PTS Control Block – Single Transfer Mode               | 5-22 |

| 5-13   | PTS Control Block – Block Transfer Mode                |      |

| 5-14   | PTS Control Block – A/D Scan Mode                      |      |

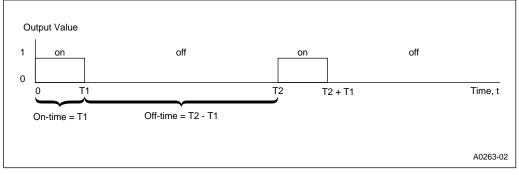

| 5-15   | A Generic PWM Waveform                                 |      |

| 5-16   | PTS Control Block – PWM Toggle Mode                    |      |

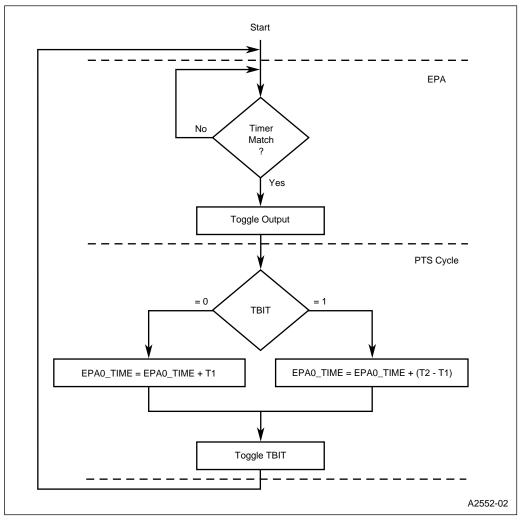

| 5-17   | EPA and PTS Operations for the PWM Toggle Mode Example |      |

| 5-18   | PTS Control Block – PWM Remap Mode                     |      |

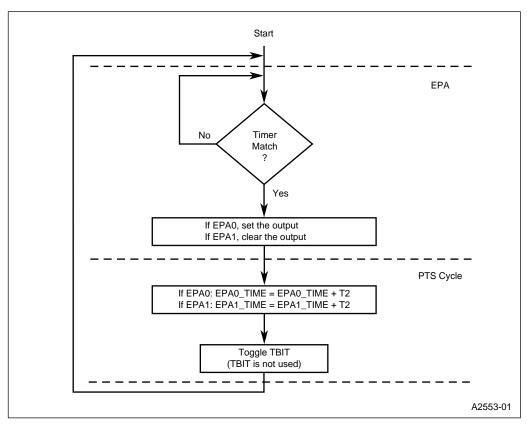

| 5-19   | EPA and PTS Operations for the PWM Remap Mode Example  |      |

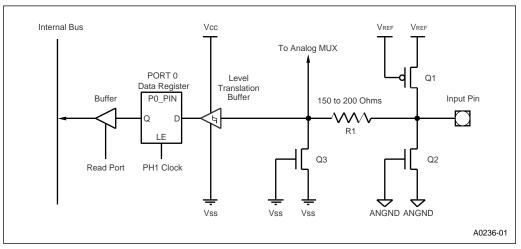

| 6-1    | Standard Input-only Port Structure                     |      |

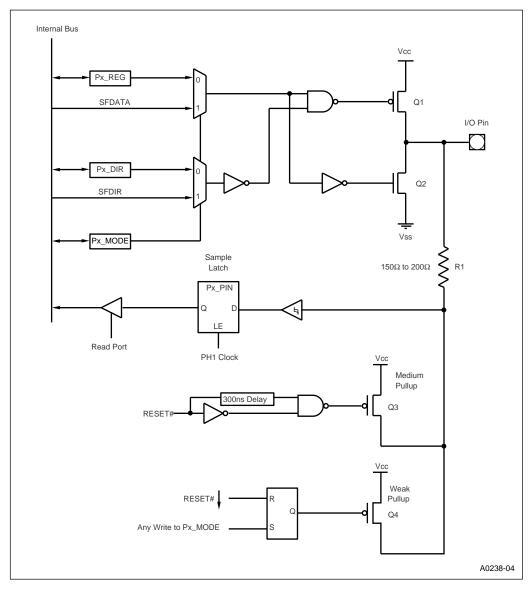

| 6-2    | Bidirectional Port Structure                           |      |

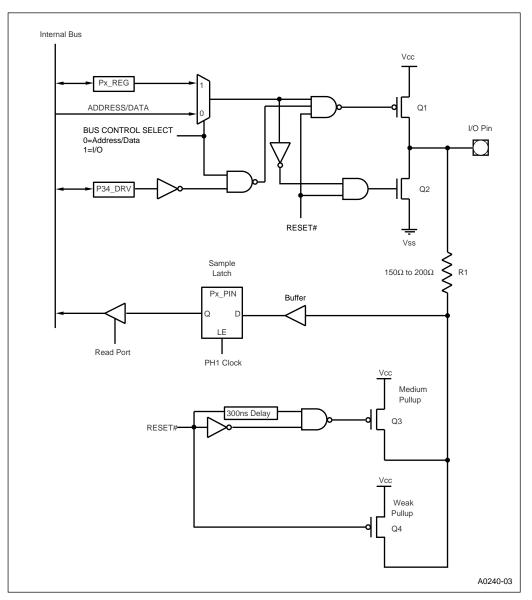

| 6-3    | Address/Data Bus (Ports 3 and 4) Structure             |      |

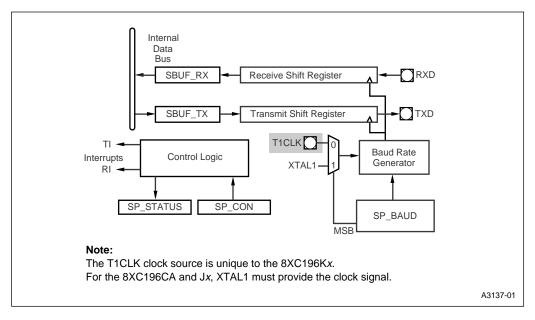

| 7-1    | SIO Block Diagram                                      |      |

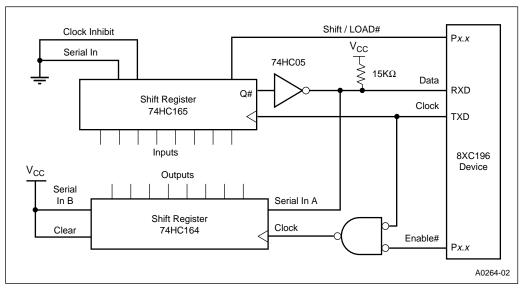

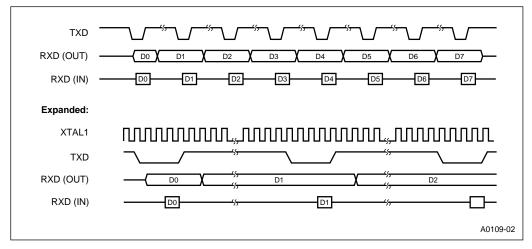

| 7-2    | Typical Shift Register Circuit for Mode 0              |      |

| 7-3    | Mode 0 Timing                                          |      |

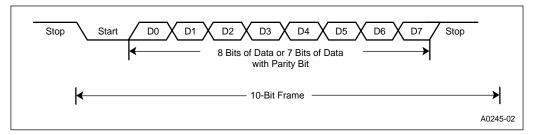

| 7-4    | Serial Port Frames for Mode 1                          |      |

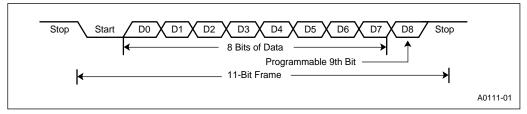

| 7-5    | Serial Port Frames in Mode 2 and 3                     |      |

| 7-6    | Serial Port Control (SP_CON) Register                  |      |

| 7-7    | Serial Port Baud Rate (SP_BAUD) Register               |      |

| 7-8    | Serial Port Status (SP_STATUS) Register                |      |

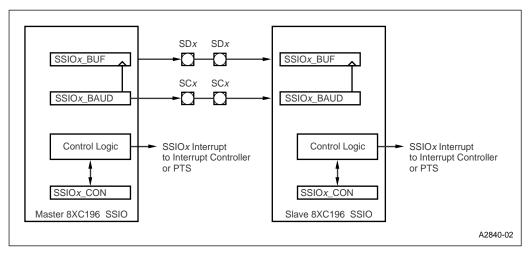

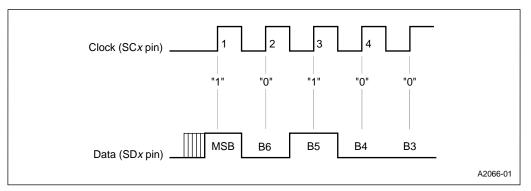

| 8-1    | SSIO Block Diagram                                     |      |

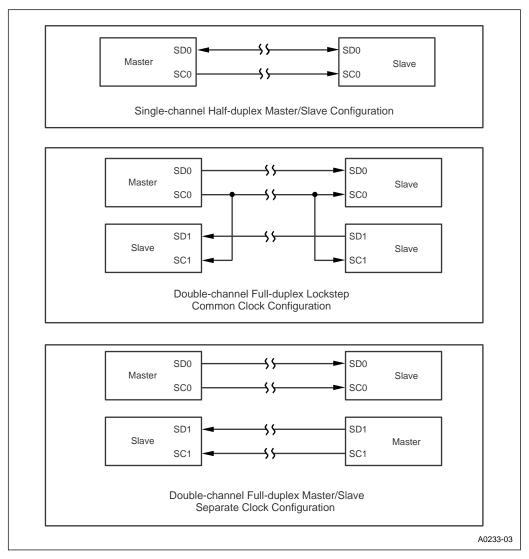

| 8-2    | SSIO Operating Modes                                   |      |

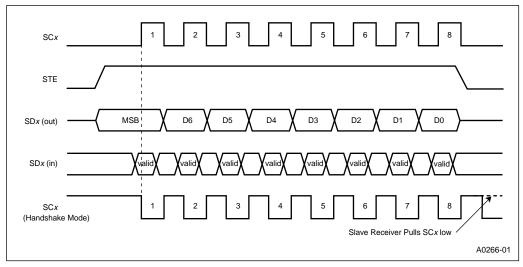

| 8-3    | SSIO Transmit/Receive Timings                          |      |

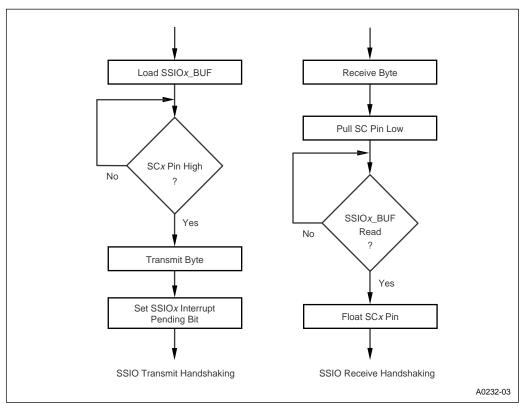

| 8-4    | SSIO Handshaking Flow Diagram                          |      |

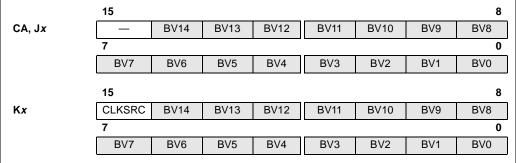

| 8-5    | Synchronous Serial Port Baud (SSIO_BAUD) Register      |      |

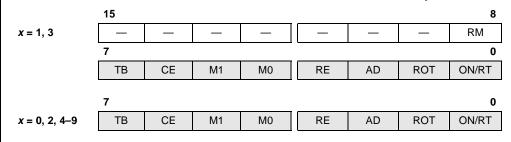

| 8-6    | Synchronous Serial Control x (SSIOx_CON) Registers     |      |

| 8-7    | Variable-width MSB in SSIO Transmissions               | 8-14 |

| Figure |                                                          | Page  |

|--------|----------------------------------------------------------|-------|

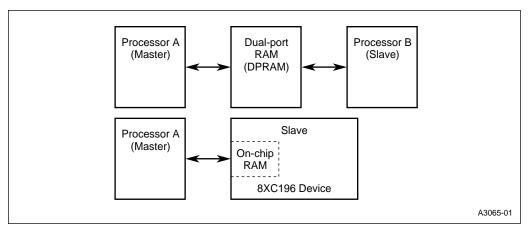

| 9-1    | DPRAM vs Slave-Port Solution                             | 9-2   |

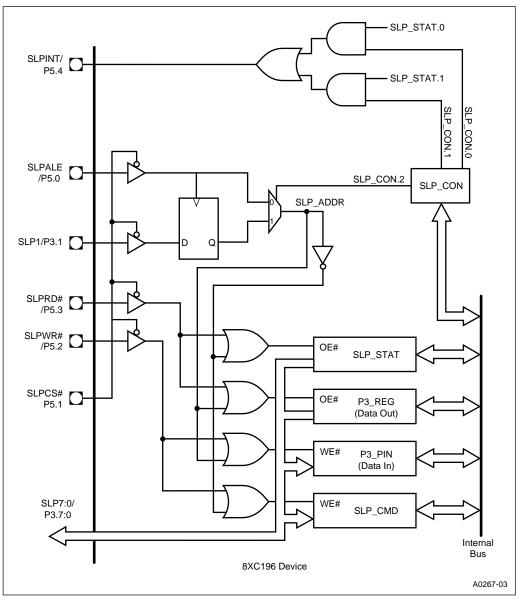

| 9-2    | Slave Port Block Diagram                                 | 9-3   |

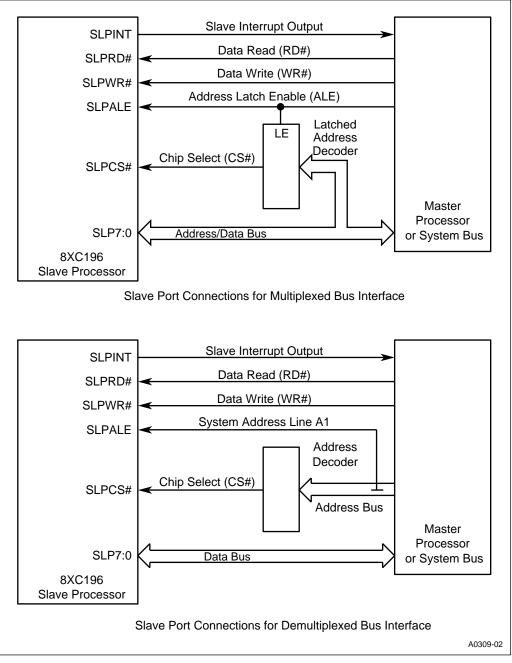

| 9-3    | Master/Slave Hardware Connections                        | 9-7   |

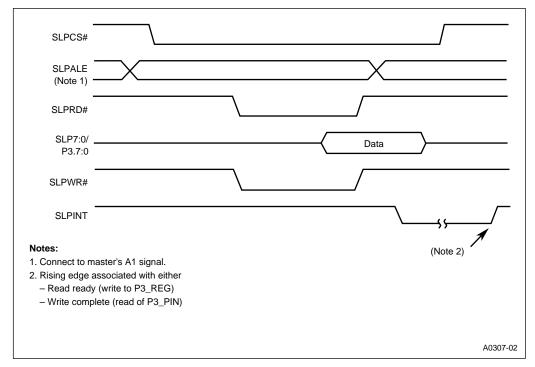

| 9-4    | Standard Slave Mode Timings (Demultiplexed Bus)          | 9-10  |

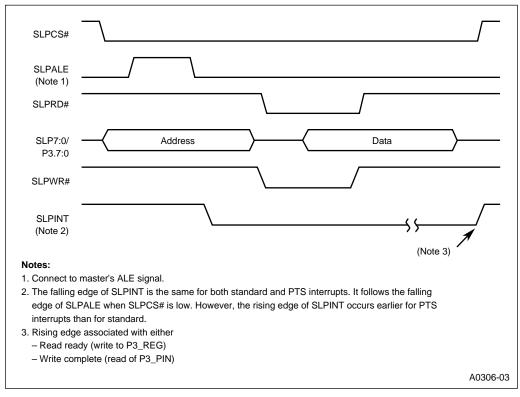

| 9-5    | Standard or Shared Memory Mode Timings (Multiplexed Bus) | 9-13  |

| 9-6    | Slave Port Control (SLP_CON) Register                    |       |

| 9-7    | Slave Port Status (SLP_STAT) Register                    |       |

| 10-1   | EPA Block Diagram                                        |       |

| 10-2   | EPA Timer/Counters                                       |       |

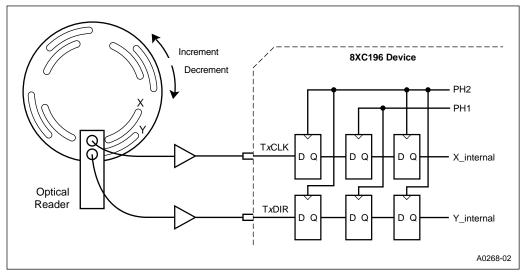

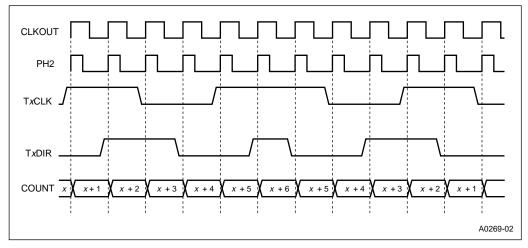

| 10-3   | Quadrature Mode Interface                                | 10-8  |

| 10-4   | Quadrature Mode Timing and Count                         | 10-9  |

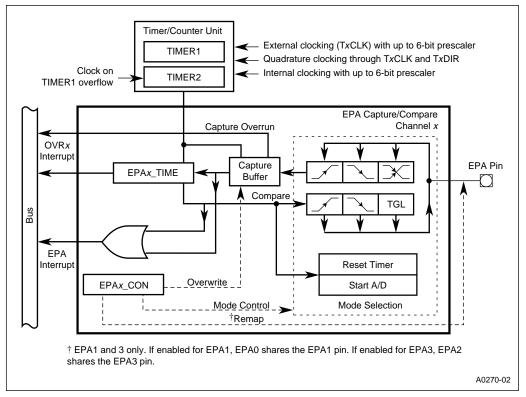

| 10-5   | A Single EPA Capture/Compare Channel                     | 10-10 |

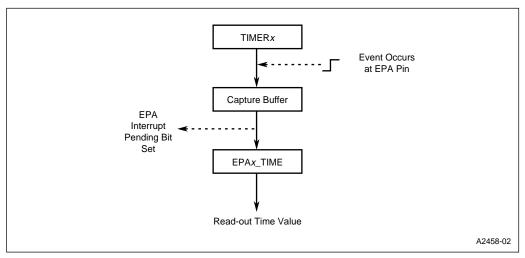

| 10-6   | EPA Simplified Input-Capture Structure                   | 10-11 |

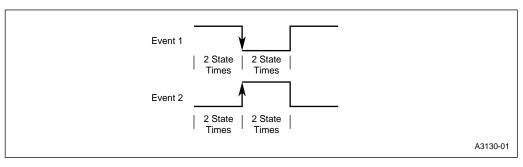

| 10-7   | Valid EPA Input Events                                   | 10-12 |

| 10-8   | Timer 1 Control (T1CONTROL) Register                     | 10-18 |

| 10-9   | Timer 2 Control (T2CONTROL) Register                     | 10-19 |

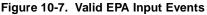

| 10-10  | EPA Control (EPAx_CON) Registers                         | 10-21 |

| 10-11  | EPA Compare Control (COMPx_CON) Registers                |       |

| 10-12  | EPA Interrupt Mask (EPA_MASK) Register                   | 10-27 |

| 10-13  | EPA Interrupt Mask 1 (EPA_MASK1) Register                | 10-27 |

| 10-14  | EPA Interrupt Pending (EPA_PEND) Register                |       |

| 10-15  | EPA Interrupt Pending 1 (EPA_PEND1) Registers            | 10-29 |

| 10-16  | EPA Interrupt Priority Vector Register (EPAIPV)          | 10-30 |

| 11-1   | A/D Converter Block Diagram                              | 11-1  |

| 11-2   | A/D Test (AD_TEST) Register                              | 11-5  |

| 11-3   | A/D Result (AD_RESULT) Register — Write Format           | 11-6  |

| 11-4   | A/D Time (AD_TIME) Register                              | 11-7  |

| 11-5   | A/D Command (AD_COMMAND) Register                        | 11-8  |

| 11-6   | A/D Result (AD_RESULT) Register — Read Format            | 11-10 |

| 11-7   | Idealized A/D Sampling Circuitry                         |       |

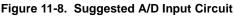

| 11-8   | Suggested A/D Input Circuit                              | 11-13 |

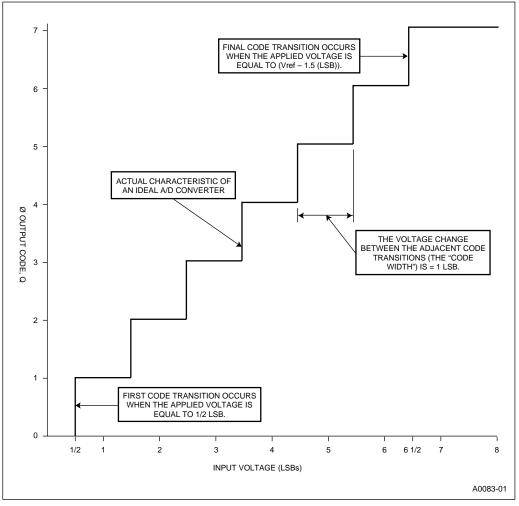

| 11-9   | Ideal A/D Conversion Characteristic                      |       |

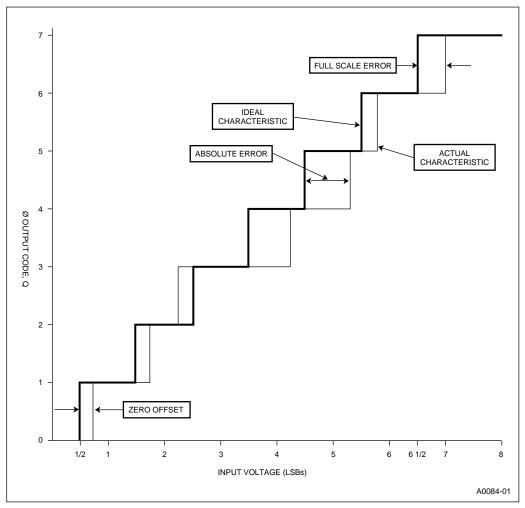

| 11-10  | Actual and Ideal A/D Conversion Characteristics          | 11-17 |

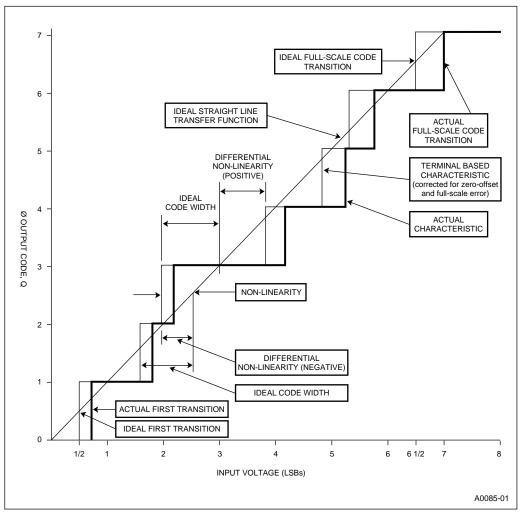

| 11-11  | Terminal-based A/D Conversion Characteristic             |       |

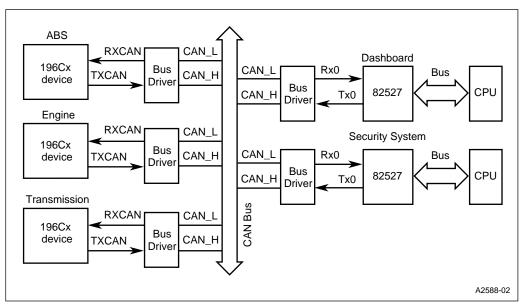

| 12-1   | A System Using CAN Controllers                           |       |

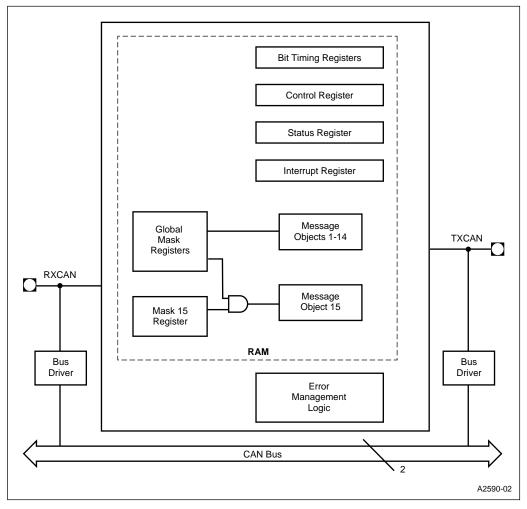

| 12-2   | CAN Controller Block Diagram                             |       |

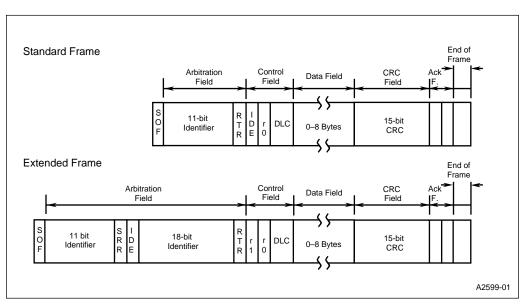

| 12-3   | CAN Message Frames                                       |       |

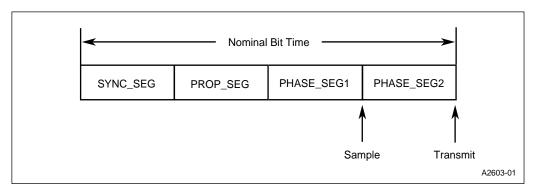

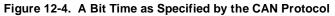

| 12-4   | A Bit Time as Specified by the CAN Protocol              |       |

| 12-5   | A Bit Time as Implemented in the CAN Controller          |       |

| 12-6   | CAN Control (CAN_CON) Register                           | 12-13 |

| 12-7   | CAN Bit Timing 0 (CAN_BTIME0) Register                   |       |

| 12-8   | CAN Bit Timing 1 (CAN_BTIME1) Register                   |       |

| 12-9   | CAN Standard Global Mask (CAN_SGMSK) Register            |       |

| 12-10  | CAN Extended Global Mask (CAN_EGMSK) Register            | 12-19 |

| Figure |                                                                                | Page  |

|--------|--------------------------------------------------------------------------------|-------|

| 12-11  | CAN Message 15 Mask (CAN_MSK15) Register                                       | 12-20 |

| 12-12  | CAN Message Object x Configuration (CAN_MSGxCFG) Register                      | 12-21 |

| 12-13  | CAN Message Object x Identifier (CAN_MSGxID0-3) Register                       |       |

| 12-14  | CAN Message Object x Control 0 (CAN_MSGxCON0) Register                         |       |

| 12-15  | CAN Message Object x Control 1 (CAN_MSGxCON1) Register                         |       |

| 12-16  | CAN Message Object Data (CAN_MSGxDATA0-7) Registers                            |       |

| 12-17  | CAN Control (CAN_CON) Register                                                 |       |

| 12-18  | CAN Message Object x Control 0 (CAN_MSGxCON0) Register                         |       |

| 12-19  | CAN Interrupt Pending (CAN_INT) Register                                       |       |

| 12-20  | CAN Status (CAN_STAT) Register                                                 |       |

| 12-21  | CAN Message Object x Control 0 (CAN_MSGxCON0) Register                         |       |

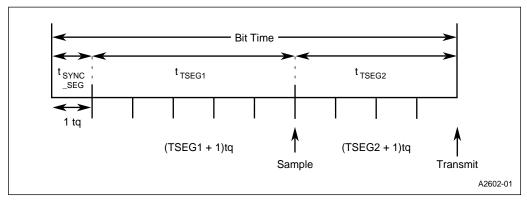

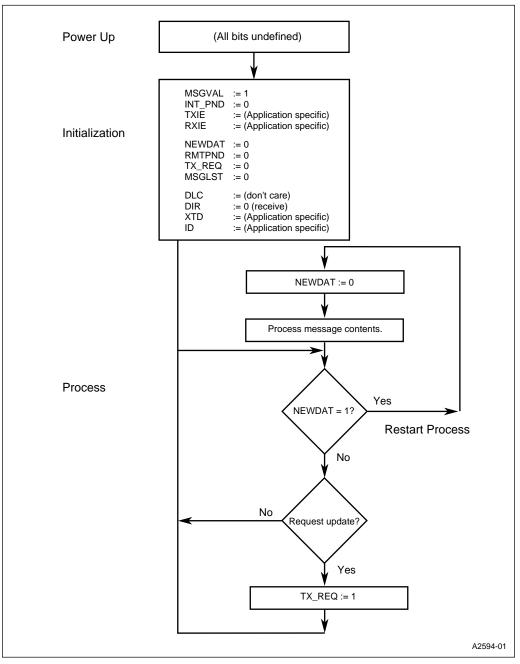

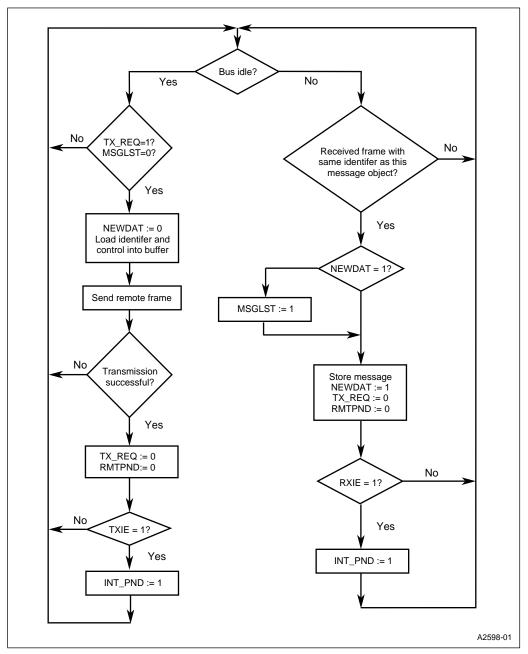

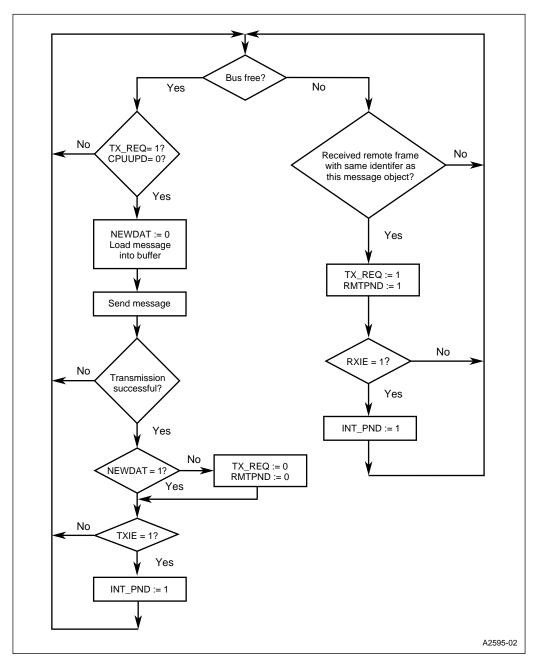

| 12-22  | Receiving a Message for Message Objects 1–14 — CPU Flow                        |       |

| 12-23  | Receiving a Message for Message Object 15 — CPU Flow                           | 12-37 |

| 12-24  | Receiving a Message — CAN Controller Flow                                      |       |

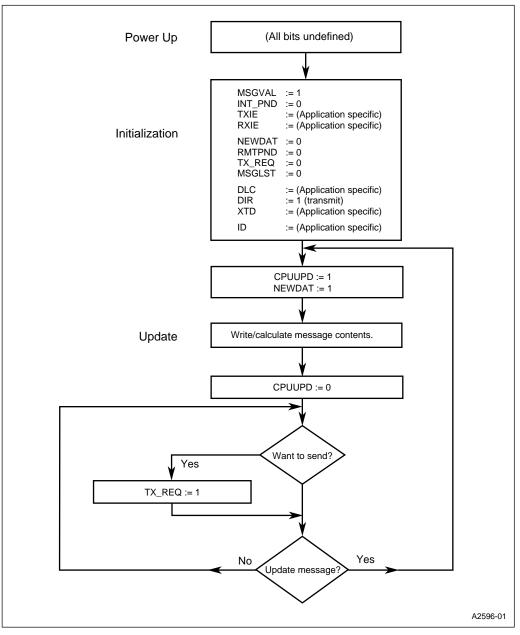

| 12-25  | Transmitting a Message — CPU Flow                                              |       |

| 12-26  | Transmitting a Message — CAN Controller Flow                                   |       |

| 13-1   | Minimum Hardware Connections                                                   |       |

| 13-2   | Power and Return Connections                                                   |       |

| 13-3   | On-chip Oscillator Circuit                                                     |       |

| 13-4   | External Crystal Connections                                                   |       |

| 13-5   | External Clock Connections                                                     |       |

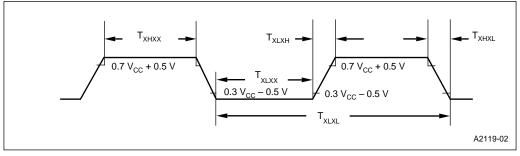

| 13-6   | External Clock Drive Waveforms                                                 |       |

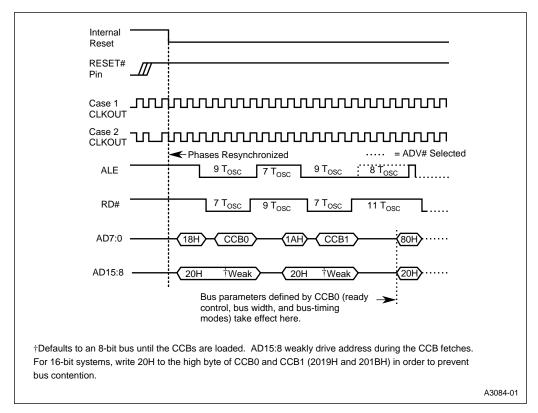

| 13-7   | Reset Timing Sequence                                                          |       |

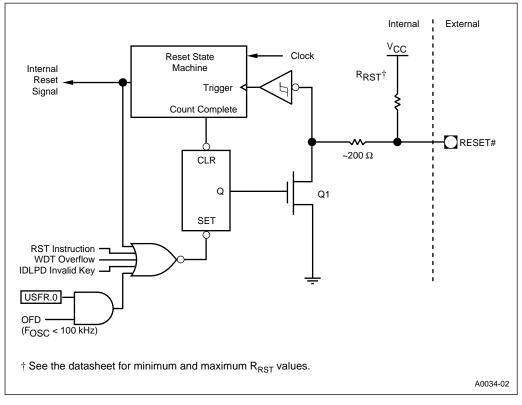

| 13-8   | Internal Reset Circuitry                                                       |       |

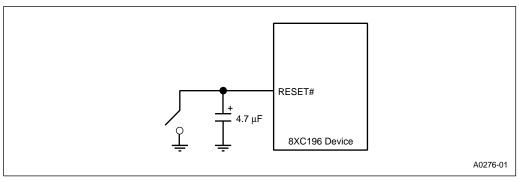

| 13-9   | Minimum Reset Circuit                                                          |       |

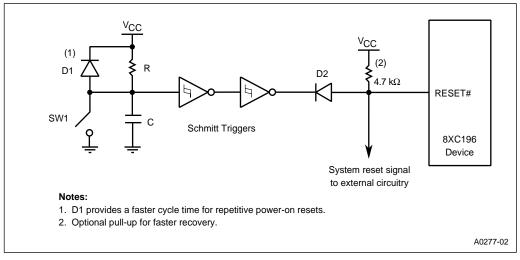

| 13-10  | Example System Reset Circuit                                                   |       |

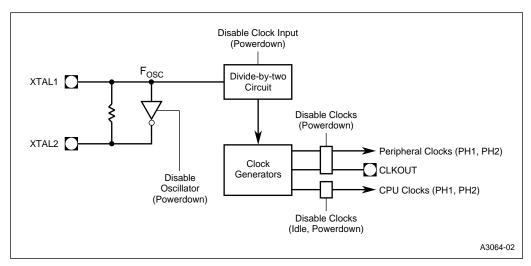

| 14-1   | Clock Control During Power-saving Modes                                        |       |

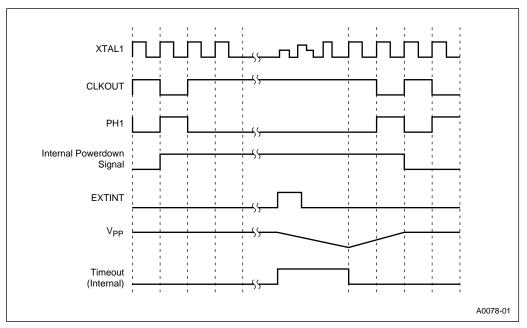

| 14-2   | Power-up and Powerdown Sequence When Using an External Interrupt               |       |

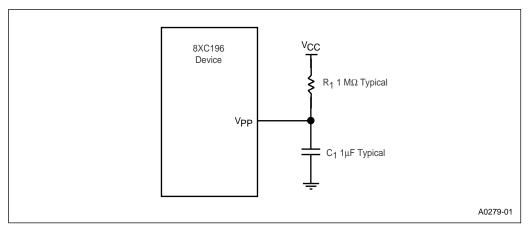

| 14-3   | External RC Circuit                                                            |       |

| 14-4   | Typical Voltage on the $V_{\mbox{\scriptsize PP}}$ Pin While Exiting Powerdown |       |

| 15-1   | Chip Configuration 0 (CCR0) Register                                           |       |

| 15-2   | Chip Configuration 1 (CCR1) Register                                           |       |

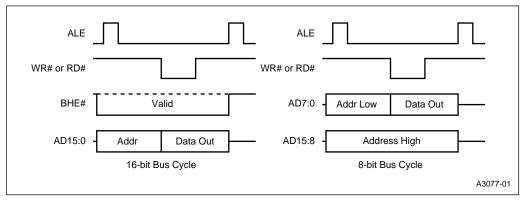

| 15-3   | Multiplexing and Bus Width Options                                             |       |

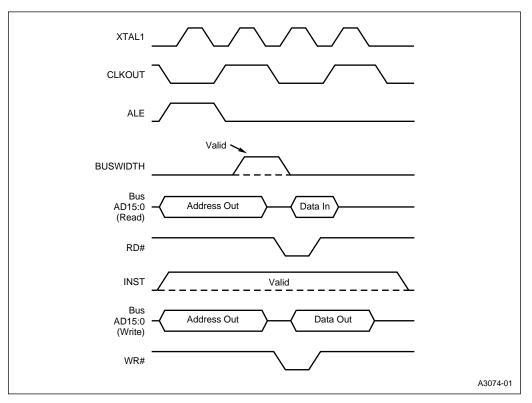

| 15-4   | BUSWIDTH Timing Diagram                                                        |       |

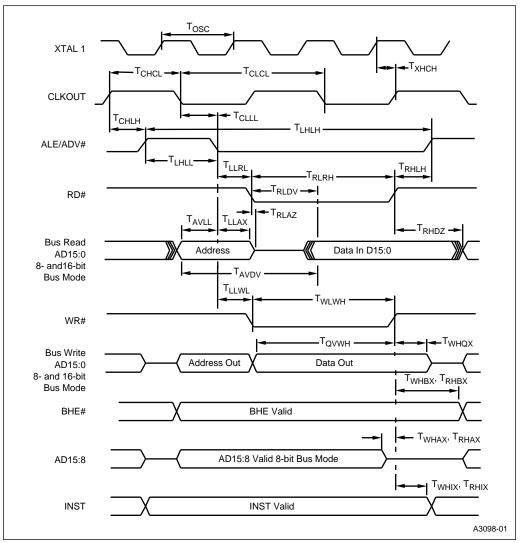

| 15-5   | Timings for 16-bit Buses                                                       |       |

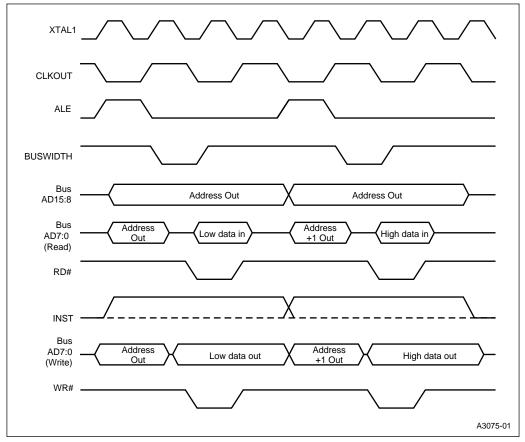

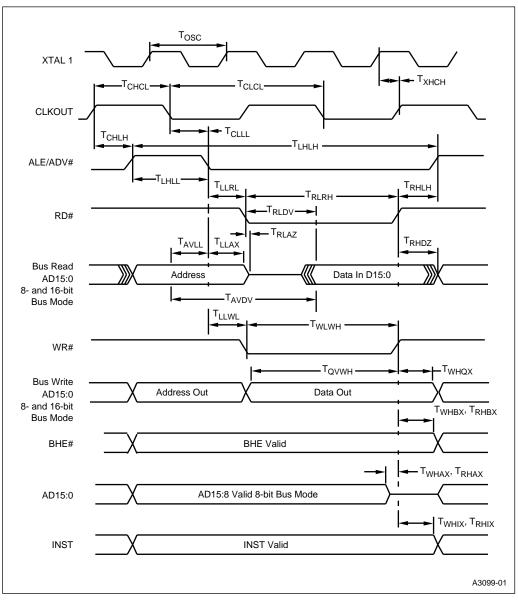

| 15-6   | Timings for 8-bit Buses                                                        |       |

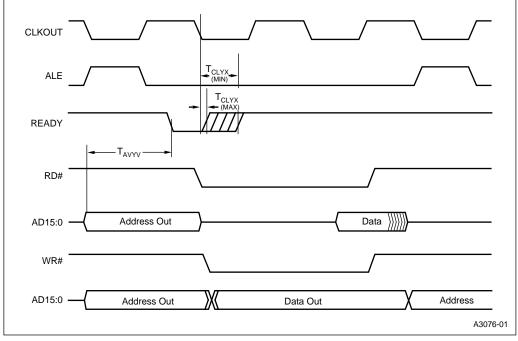

| 15-7   | READY Timing Diagram                                                           |       |

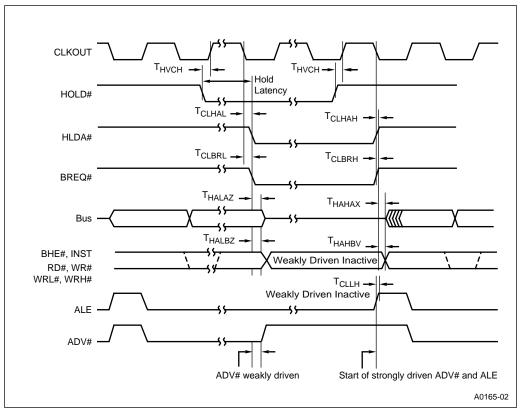

| 15-8   | HOLD#, HLDA# Timing                                                            |       |

| 15-9   | Standard Bus Control                                                           |       |

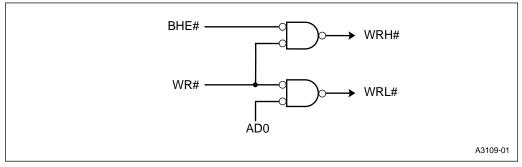

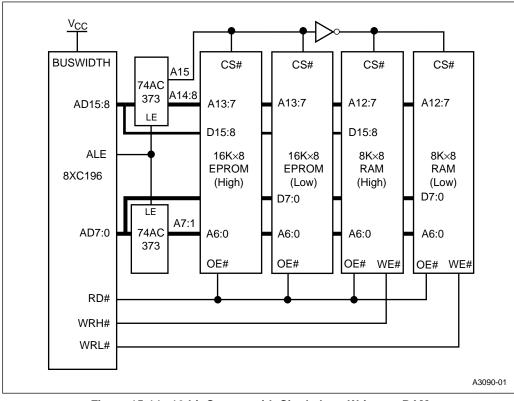

| 15-10  | Decoding WRL# and WRH#                                                         |       |

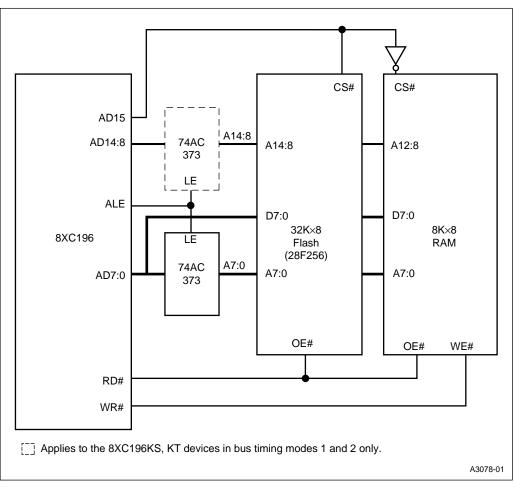

| 15-11  | 8-bit System with Flash and RAM                                                |       |

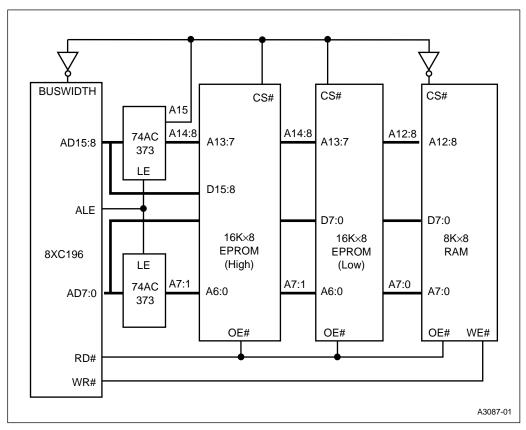

| 15-12  | 16-bit System with Dynamic Bus Width                                           |       |

| 15-13  | Write Strobe Mode                                                              |       |

| 15-14  | 16-bit System with Single-byte Writes to RAM                                   | 15-25 |

| Figure |                                                  | Page  |

|--------|--------------------------------------------------|-------|

| 15-15  | Address Valid Strobe Mode                        |       |

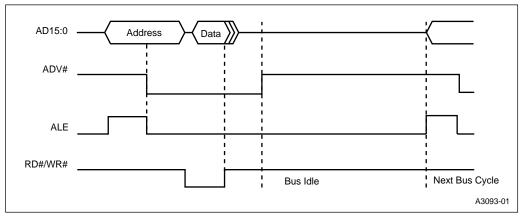

| 15-16  | Comparison of ALE and ADV# Bus Cycles            | 15-26 |

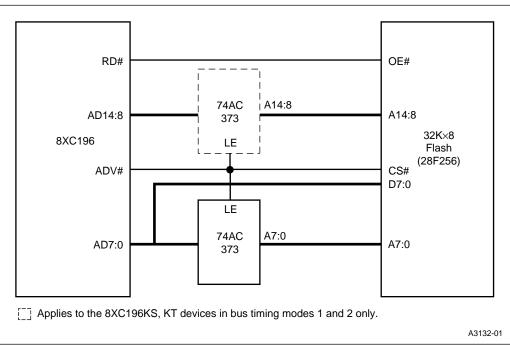

| 15-17  | 8-bit System with Flash                          | 15-27 |

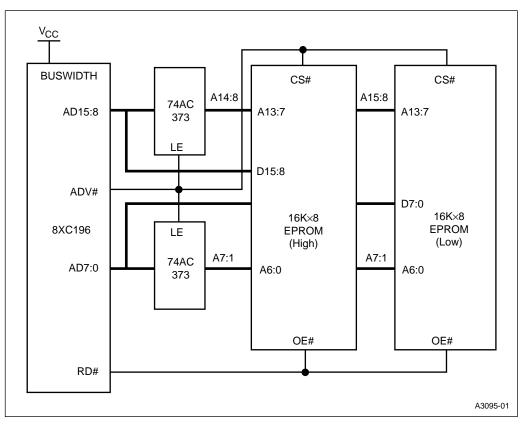

| 15-18  | 16-bit System with EPROM                         | 15-28 |

| 15-19  | Timings of Address Valid with Write Strobe Mode  | 15-29 |

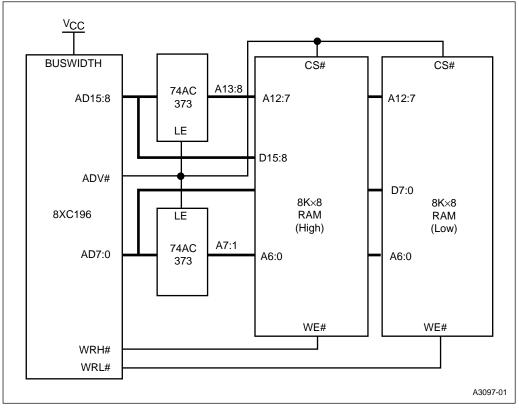

| 15-20  | 16-bit System with RAM                           | 15-30 |

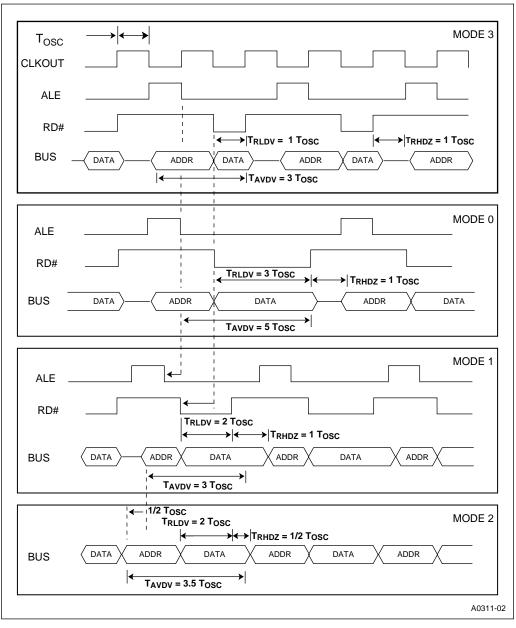

| 15-21  | Modes 0, 1, 2, and 3 Timings                     | 15-31 |

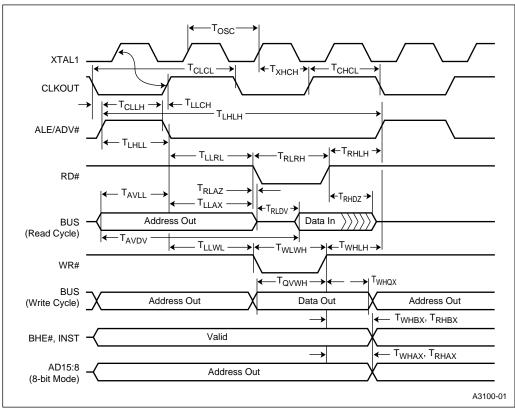

| 15-22  | Mode 1 System Bus Timing                         | 15-33 |

| 15-23  | Mode 2 System Bus Timing                         | 15-35 |

| 15-24  | System Bus Timing                                | 15-36 |

| 16-1   | Unerasable PROM (USFR) Register                  | 16-7  |

| 16-2   | Programming Pulse Width Register (PPW or SP_PPW) | 16-9  |

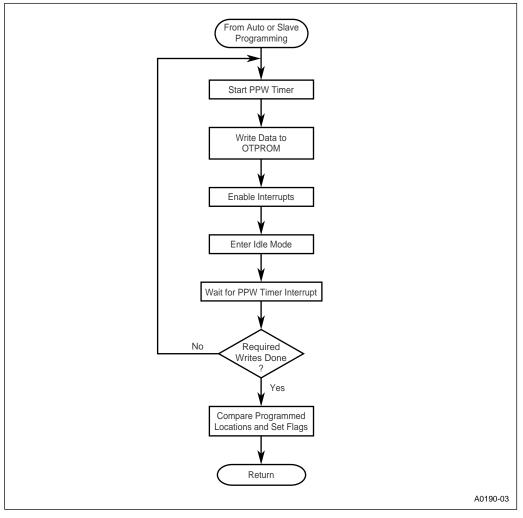

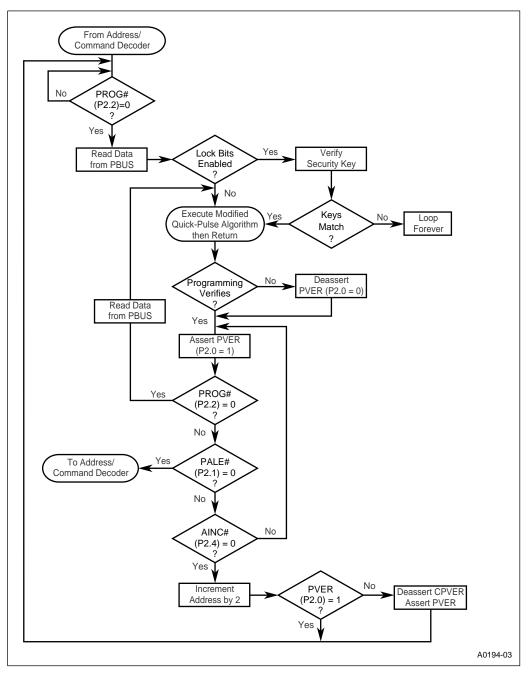

| 16-3   | Modified Quick-pulse Algorithm                   | 16-10 |

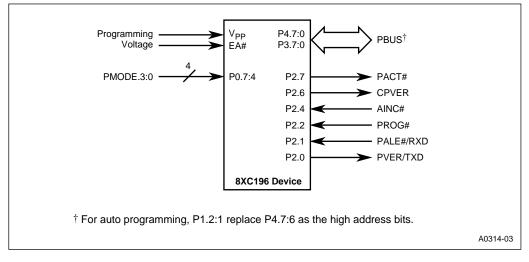

| 16-4   | Pin Functions in Programming Modes               | 16-11 |

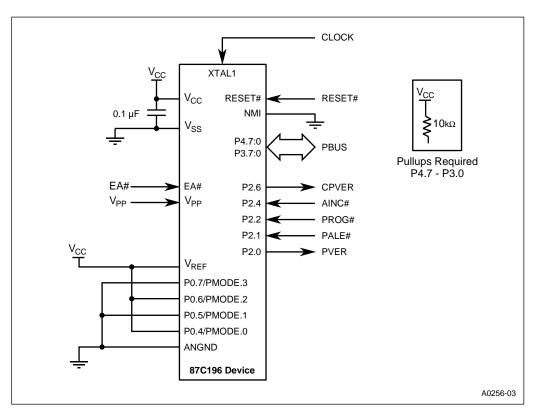

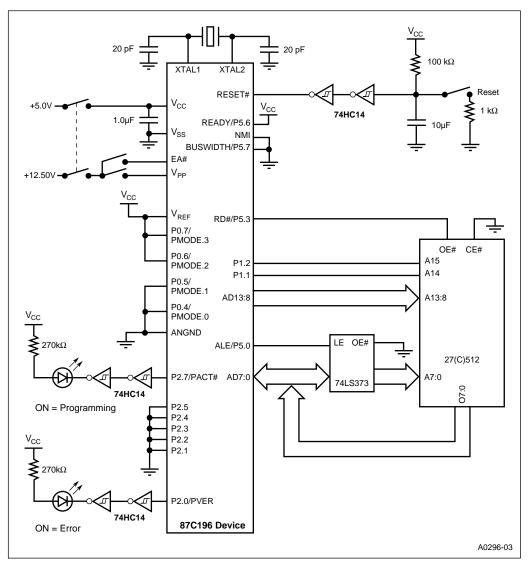

| 16-5   | Slave Programming Circuit                        | 16-17 |

| 16-6   | Chip Configuration Registers (CCRs)              | 16-19 |

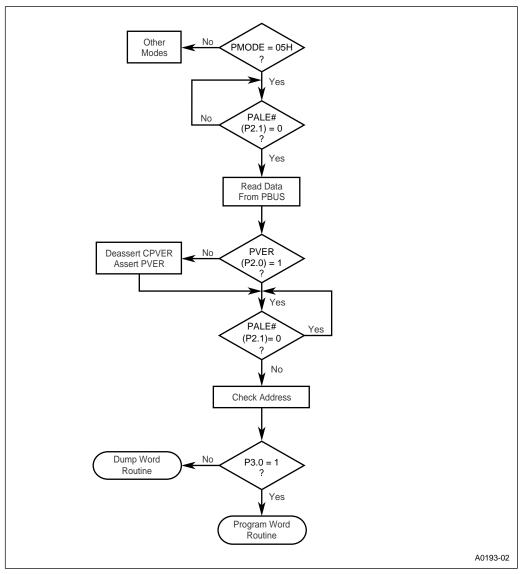

| 16-7   | Address/Command Decoding Routine                 | 16-21 |

| 16-8   | Program Word Routine                             |       |

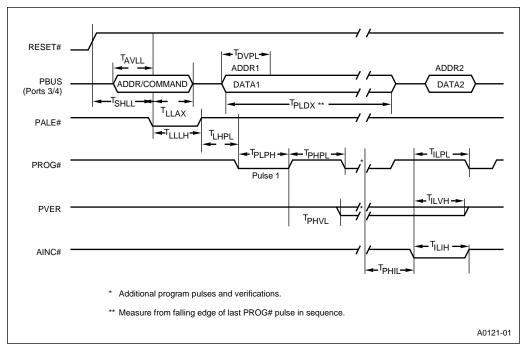

| 16-9   | Program Word Waveform                            |       |

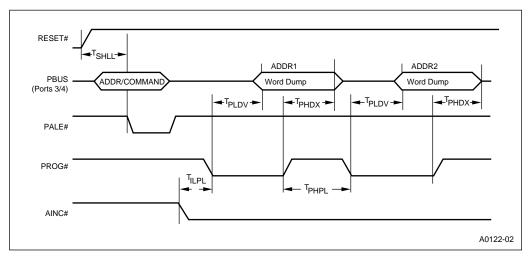

| 16-10  | Dump Word Routine                                | 16-24 |

| 16-11  | Dump Word Waveform                               | 16-25 |

| 16-12  | Auto Programming Circuit for 8XC196Kx Devices    |       |

| 16-13  | Auto Programming Routine                         |       |

| 16-14  | Serial Port Programming Mode Circuit             |       |

| 16-15  | Run-time Programming Code Example                |       |

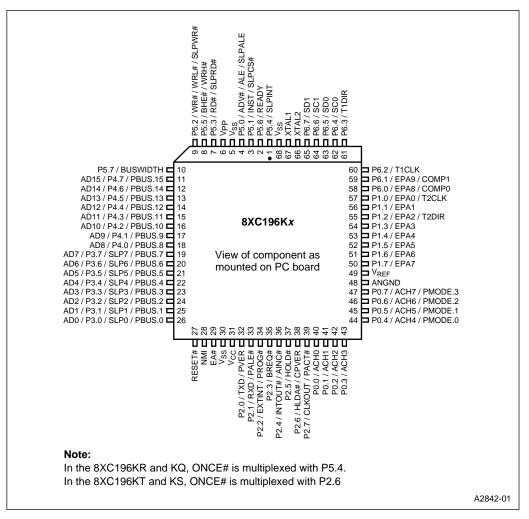

| B-1    | 8XC196Kx 68-lead PLCC Package                    | B-3   |

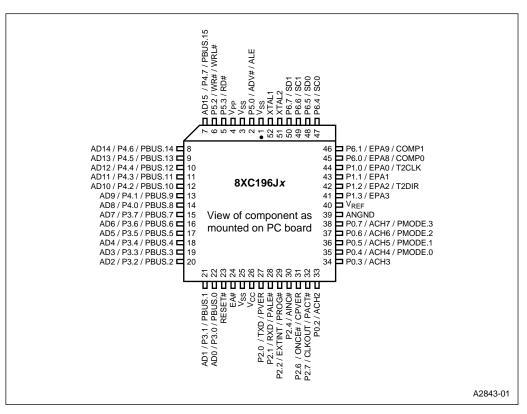

| B-2    | 8XC196Jx 52-lead PLCC Package                    | B-5   |

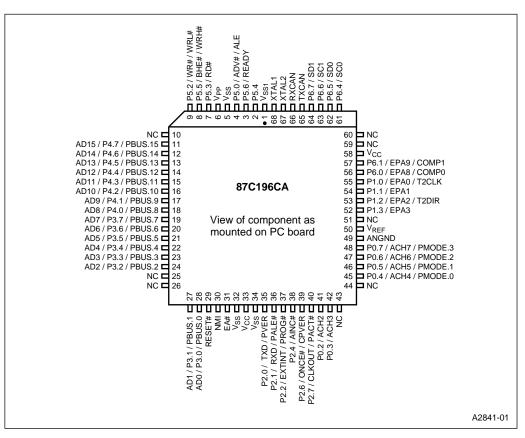

| B-3    | 87C196CA 68-lead PLCC Package                    |       |

| Table |                                                                     | Page |

|-------|---------------------------------------------------------------------|------|

| 1-1   | Handbooks and Product Information                                   | 1-6  |

| 1-2   | Application Notes, Application Briefs, and Article Reprints         |      |

| 1-3   | MCS <sup>®</sup> 96 Microcontroller Datasheets (Commercial/Express) | 1-7  |

| 1-4   | MCS <sup>®</sup> 96 Microcontroller Datasheets (Automotive)         | 1-7  |

| 1-5   | MCS <sup>®</sup> 96 Microcontroller Quick References                |      |

| 2-1   | Features of the 8XC196Kx, Jx, CA Product Family                     | 2-2  |

| 2-2   | State Times at Various Frequencies                                  | 2-8  |

| 2-3   | Unsupported Functions in 87C196CA Devices                           | 2-13 |

| 2-4   | Unsupported Functions in 8XC196Jx Devices                           | 2-14 |

| 3-1   | Operand Type Definitions                                            | 3-1  |

| 3-2   | Equivalent Operand Types for Assembly and C Programming Languages   | 3-2  |

| 3-3   | Definition of Temporary Registers                                   | 3-6  |

| 4-1   | Memory Map                                                          | 4-2  |

| 4-2   | Special-purpose Memory Addresses                                    | 4-3  |

| 4-3   | Memory-mapped SFRs                                                  | 4-5  |

| 4-4   | Peripheral SFRs                                                     | 4-7  |

| 4-5   | CAN Peripheral SFRs — 8XC196CA Only                                 | 4-8  |

| 4-6   | Register File Memory Addresses                                      | 4-11 |

| 4-7   | CPU SFRs                                                            |      |

| 4-8   | Selecting a Window of Peripheral SFRs                               |      |

| 4-9   | Selecting a Window of the Upper Register File                       | 4-16 |

| 4-10  | Selecting a Window of Upper Register RAM — 8XC196JV Only            | 4-17 |

| 4-11  | Windows                                                             | 4-18 |

| 4-12  | Windowed Base Addresses                                             | 4-20 |

| 5-1   | Interrupt Signals                                                   | 5-3  |

| 5-2   | Interrupt and PTS Control and Status Registers                      | 5-3  |

| 5-3   | Interrupt Sources, Vectors, and Priorities                          | 5-5  |

| 5-4   | Execution Times for PTS Cycles                                      | 5-10 |

| 5-5   | Single Transfer Mode PTSCB                                          | 5-24 |

| 5-6   | Block Transfer Mode PTSCB                                           | 5-24 |

| 5-7   | A/D Scan Mode Command/Data Table                                    | 5-28 |

| 5-8   | Command/Data Table (Example 1)                                      |      |

| 5-9   | A/D Scan Mode PTSCB (Example 1)                                     |      |

| 5-10  | Command/Data Table (Example 2)                                      |      |

| 5-11  | A/D Scan Mode PTSCB (Example 2)                                     | 5-31 |

| 5-12  | Comparison of PWM Modes                                             | 5-31 |

| 5-13  | PWM Toggle Mode PTSCB                                               |      |

| 5-14  | PWM Remap Mode PTSCB                                                |      |

| 6-1   | Device I/O Ports                                                    |      |

| 6-2   | Standard Input-only Port Pins                                       |      |

| 6-3   | Input-only Port Registers                                           | 6-2  |

| 6-4   | Bidirectional Port Pins                                             |      |

| 6-5   | Bidirectional Port Control and Status Registers                     |      |

| 6-6   | Logic Table for Bidirectional Ports in I/O Mode                     | 6-9  |

| Table |                                                              | Page |

|-------|--------------------------------------------------------------|------|

| 6-7   | Logic Table for Bidirectional Ports in Special-function Mode | 6-9  |

| 6-8   | Control Register Values for Each Configuration               |      |

| 6-9   | Port Configuration Example                                   | 6-11 |

| 6-10  | Port Pin States After Reset and After Example Code Execution | 6-12 |

| 6-11  | Ports 3 and 4 Pins                                           | 6-16 |

| 6-12  | Ports 3 and 4 Control and Status Registers                   |      |

| 6-13  | Logic Table for Ports 3 and 4 as I/O                         | 6-18 |

| 7-1   | Serial Port Signals                                          |      |

| 7-2   | Serial Port Control and Status Registers                     |      |

| 7-3   | SP_BAUD Values When Using XTAL1 at 16 MHz                    |      |

| 8-1   | SSIO Port Signals                                            |      |

| 8-2   | SSIO Port Control and Status Registers                       |      |

| 8-3   | Common SSIO_BAUD Values at 16 MHz                            |      |

| 9-1   | Slave Port Signals                                           |      |

| 9-2   | Slave Port Control and Status Registers                      | 9-4  |

| 9-3   | Master and Slave Interconnections                            |      |

| 10-1  | EPA Channels                                                 |      |

| 10-2  | EPA and Timer/Counter Signals                                |      |

| 10-3  | EPA Control and Status Registers                             |      |

| 10-4  | Quadrature Mode Truth Table                                  |      |

| 10-5  | Action Taken when a Valid Edge Occurs                        |      |

| 10-6  | Example Control Register Settings and EPA Operations         |      |

| 10-7  | EPAIPV Interrupt Priority Values                             |      |

| 11-1  | A/D Converter Pins                                           |      |

| 11-2  | A/D Control and Status Registers                             |      |

| 12-1  | CAN Controller Signals                                       |      |

| 12-2  | Control and Status Registers                                 |      |

| 12-3  | CAN Controller Address Map                                   |      |

| 12-4  | Message Object Structure                                     |      |

| 12-5  | Effect of Masking on Message Identifiers                     |      |

| 12-6  | Standard Message Frame                                       |      |

| 12-7  | Extended Message Frame                                       |      |

| 12-8  | CAN Protocol Bit Time Segments                               |      |

| 12-9  | CAN Controller Bit Time Segments                             |      |

| 12-10 | Bit Timing Relationships                                     |      |

| 12-11 | Bit Timing Requirements for Synchronization                  |      |

| 12-12 | Control Register Bit-pair Interpretation                     |      |

| 12-13 | Cross-reference for Register Bits Shown in Flowcharts        |      |

| 12-14 | Register Values Following Reset                              |      |

| 13-1  | Minimum Required Signals                                     |      |

| 13-2  | I/O Port Configuration Guide                                 |      |

| 14-1  | Operating Mode Control Signals                               |      |

| 14-2  | Operating Mode Control and Status Registers                  |      |

| 14-3  | ONCE# Pin Alternate Functions                                | 14-9 |

| Table |                                                                        | Page  |

|-------|------------------------------------------------------------------------|-------|

| 14-4  | Test-mode-entry Pins                                                   | 14-10 |

| 15-1  | External Memory Interface Signals                                      |       |

| 15-2  | READY Signal Timing Definitions                                        | 15-16 |

| 15-3  | HOLD#, HLDA# Timing Definitions                                        | 15-18 |

| 15-4  | Maximum Hold Latency                                                   | 15-19 |

| 15-5  | Bus-control Mode                                                       | 15-20 |

| 15-6  | Modes 0, 1, 2, and 3 Timing Comparisons                                |       |

| 15-7  | AC Timing Symbol Definitions                                           |       |

| 15-8  | AC Timing Definitions                                                  | 15-37 |

| 16-1  | OTPROM Sizes for 87C196Kx, Jx, CA Devices                              |       |

| 16-2  | 87C196Kx OTPROM Memory Map                                             |       |

| 16-3  | Memory Protection for Normal Operating Mode                            |       |

| 16-4  | Memory Protection Options for Programming Modes                        |       |

| 16-5  | UPROM Programming Values and Locations for Slave Mode                  |       |

| 16-6  | Pin Descriptions                                                       |       |

| 16-7  | PMODE Values                                                           |       |

| 16-8  | Device Signature Word and Programming Voltages                         |       |

| 16-9  | Slave Programming Mode Memory Map                                      |       |

| 16-10 | Timing Mnemonics                                                       |       |

| 16-11 | Auto Programming Memory Map                                            |       |

| 16-12 | Serial Port Programming Mode Memory Map                                |       |

| 16-13 | Serial Port Programming Default Values and Locations                   |       |

| 16-14 | User Program Register Values and Test ROM Locations                    |       |

| 16-15 | RISM Command Descriptions                                              |       |

| A-1   | Opcode Map (Left Half)                                                 |       |

| A-1   | Opcode Map (Right Half)                                                |       |

| A-2   | Processor Status Word (PSW) Flags                                      |       |

| A-3   | Effect of PSW Flags or Specified Bits on Conditional Jump Instructions |       |

| A-4   | PSW Flag Setting Symbols                                               |       |

| A-5   | Operand Variables                                                      |       |

| A-6   | Instruction Set                                                        |       |

| A-7   | Instruction Opcodes                                                    |       |

| A-8   | Instruction Lengths and Hexadecimal Opcodes                            |       |

| A-9   | Instruction Execution Times (in State Times)                           |       |

| B-1   | Signal Name Changes                                                    |       |

| B-2   | 8XC196Kx Signals Arranged by Functional Categories                     |       |

| B-3   | 8XC196Jx Signals Arranged by Functional Categories                     |       |

| B-4   | 87C196CA Signals Arranged by Functional Categories                     |       |

| B-5   | Description of Columns of Table B-6                                    |       |

| B-6   | Signal Descriptions                                                    |       |

| B-7   | Definition of Status Symbols                                           |       |

| B-8   | 8XC196Kx Pin Status                                                    |       |

| B-9   | 8XC196Jx Pin Status                                                    |       |

| B-10  | 87C196CA Pin Status                                                    |       |

| Table |                                                       | Page |

|-------|-------------------------------------------------------|------|

| C-1   | Modules and Related Registers                         | C-1  |

| C-2   | Register Name, Address, and Reset Status              |      |

| C-3   | CAN_EGMSK Addresses and Reset Values                  | C-15 |

| C-4   | CAN_MSGxCFG Addresses and Reset Values                | C-17 |

| C-5   | CAN_MSGxCON0 Addresses and Reset Values               | C-19 |

| C-6   | CAN_MSGxCON1 Addresses and Reset Values               | C-21 |

| C-7   | CAN_MSG <i>x</i> DATA0–7 Addresses                    | C-23 |

| C-8   | CAN_MSGxID0–3 Addresses                               |      |

| C-9   | CAN_MSK15 Addresses and Reset Values                  |      |

| C-10  | COMPx_CON Addresses and Reset Values                  |      |

| C-11  | COMPx_TIME Addresses and Reset Values                 |      |

| C-12  | EPAx_CON Addresses and Reset Values                   | C-43 |

| C-13  | EPAx_TIME Addresses and Reset Values                  | C-44 |

| C-14  | EPA Interrupt Priority Vectors                        |      |

| C-15  | Px_DIR Addresses and Reset Values                     |      |

| C-16  | Px_MODE Addresses and Reset Values                    |      |

| C-17  | Special-function Signals for Ports 1, 2, 5, 6         |      |

| C-18  | Px_PIN Addresses and Reset Values                     | C-54 |

| C-19  | Px_REG Addresses and Reset Values                     |      |

| C-20  | Common SSIO_BAUD Values at 16 MHz                     | C-71 |

| C-21  | SSIOx_BUF Addresses and Reset Values                  |      |

| C-22  | SSIOx_CON Addresses and Reset Values                  | C-74 |

| C-23  | TIMERx Addresses and Reset Values                     |      |

| C-24  | WSR Settings and Direct Addresses for Windowable SFRs | C-80 |

# **Guide to This Manual**

### CHAPTER 1 GUIDE TO THIS MANUAL

This manual describes the 8XC196K*x*, J*x*, CA family of embedded microcontrollers. It is intended for use by both software and hardware designers familiar with the principles of microcontrollers. This chapter describes what you'll find in this manual, lists other documents that may be useful, and explains how to access the support services we provide to help you complete your design.

#### 1.1 MANUAL CONTENTS

This manual contains several chapters and appendixes, a glossary, and an index. This chapter, Chapter 1, provides an overview of the manual. This section summarizes the contents of the remaining chapters and appendixes. The remainder of this chapter describes notational conventions and terminology used throughout the manual, provides references to related documentation, describes customer support services, and explains how to access information and assistance.

**Chapter 2** — **Architectural Overview** — provides an overview of the device hardware. It describes the core, internal timing, internal peripherals, and special operating modes.

**Chapter 3** — **Programming ConsiderAtions** — provides an overview of the instruction set, describes general standards and conventions, and defines the operand types and addressing modes supported by the MCS<sup>®</sup> 96 microcontroller family. (For additional information about the instruction set, see Appendix A.)

**Chapter 4** — **Memory Partitions** — describes the addressable memory space of the device. It describes the memory partitions, explains how to use windows to increase the amount of memory that can be accessed with register-direct (8-bit) instructions, and provides examples of memory configurations.

**Chapter 5** — **Standard and PTS Interrupts** — describes the interrupt control circuitry, priority scheme, and timing for standard and peripheral transaction server (PTS) interrupts. It also explains interrupt programming and control.

**Chapter 6** — **I/O Ports** — describes the input/output ports and explains how to configure the ports for input, output, or special functions.

**Chapter 7** — **Serial I/O (SIO) Port** — describes the asynchronous/synchronous serial I/O (SIO) port and explains how to program it.

**Chapter 8** — **Synchronous Serial I/O (SSIO) Port** — describes the synchronous serial I/O (SSIO) port and explains how to program it.

#### 8XC196Kx, Jx, CA USER'S MANUAL

**Chapter 9**—**Slave Port**— describes the slave port of the 8XC196K*x* and explains how to program it. Chapter 6, "I/O Ports," explains how to configure port 3 to serve as the slave port. This chapter discusses additional configurations specific to the slave port function and describes how to use the slave port for interprocessor communication.

**Chapter 10** — **Event Processor Array (EPA)** — describes the event processor array, a timer/counter-based, high-speed input/output unit. It describes the timer/counters and explains how to program the EPA and how to use the EPA to produce pulse-width modulated (PWM) outputs.

**Chapter 11** — **Analog-to-digital Converter** — provides an overview of the analog-to-digital (A/D) converter and describes how to program the converter, read the conversion results, and interface with external circuitry.

**Chapter 12** — **CAN Serial Communications Controller** — describes the 8XC196CA's integrated CAN controller and explains how to configure it. This integrated peripheral is similar to Intel's standalone 82527 CAN serial communications controller, supporting both the standard and extended message frames specified by the CAN 2.0 protocol parts A and B.

**Chapter 13** — **Minimum Hardware Considerations** — describes options for providing the basic requirements for device operation within a system, discusses other hardware considerations, and describes device reset options.

**Chapter 14** — **Special Operating Modes** — provides an overview of the idle, powerdown, and on-circuit emulation (ONCE) modes and describes how to enter and exit each mode.

**Chapter 15** — **Interfacing with External Memory** — lists the external memory signals and describes the registers that control the external memory interface. It discusses the bus width and memory configurations, the bus-hold protocol, write-control modes, and internal wait states and ready control. Finally, it provides timing information for the system bus.

**Chapter 16** — **Programming the Nonvolatile Memory** — provides recommended circuits, the corresponding memory maps, and flow diagrams. It also provides procedures for auto programming, and describes the commands used for serial port programming.

**Appendix A** — **Instruction Set Reference** — provides reference information for the instruction set. It describes each instruction; defines the program status word (PSW) flags; shows the relationships between instructions and PSW flags; and lists hexadecimal opcodes, instruction lengths, and execution times. (For additional information about the instruction set, see Chapter 3, "Programming ConsiderAtions.")

**Appendix B** — **Signal Descriptions** — provides reference information for the device pins, including descriptions of the pin functions, reset status of the I/O and control pins, and package pin assignments.

Appendix C — Registers — provides a compilation of all device registers arranged alphabetically by register mnemonic. It also includes tables that list the windowed direct addresses for all SFRs in each possible window.

Glossary — defines terms with special meaning used throughout this manual.

Index — lists key topics with page number references.

#### 1.2 NOTATIONAL CONVENTIONS AND TERMINOLOGY

The following notations and terminology are used throughout this manual. The Glossary defines other terms with special meanings.

| #                   | The pound symbol (#) has either of two meanings, depending on the context. When used with a signal name, the symbol means that the signal is active low. When used in an instruction, the symbol prefixes an immediate value in immediate addressing mode.                                                                                                                                                                                              |

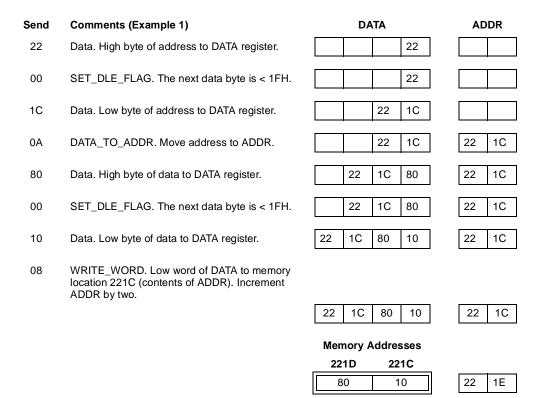

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|