# Demonstrating TMS320C2xx Pipeline Operation During an Interrupt

APPLICATION BRIEF: SPRA357

James Doublesin

Digital Signal Processing Solutions January 1998

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain application using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1997, Texas Instruments Incorporated

#### TRADEMARKS

TI is a trademark of Texas Instruments Incorporated.

Other brands and names are the property of their respective owners.

#### **CONTACT INFORMATION**

| US TMS320 HOTLINE | (281) 274-2320 |

|-------------------|----------------|

| US TMS320 FAX     | (281) 274-2324 |

| US TMS320 BBS     | (281) 274-2323 |

| US TMS320 email   | dsph@ti.com    |

#### Contents

| Abstract                                                   | 7  |

|------------------------------------------------------------|----|

| Product Support on the World Wide Web                      | 8  |

| TMS320C2xx Pipeline Scenarios                              | 9  |

| Interrupt Occurring Around SETC and CLRC                   | 10 |

| Changing IMR Register Bit to Protect Code without Globally |    |

| Disabling Interrupts                                       | 19 |

# Examples

| . 10 |

|------|

| . 11 |

| . 12 |

| . 13 |

| . 14 |

| . 15 |

| . 16 |

| . 17 |

| . 18 |

| . 19 |

| . 20 |

|      |

# Demonstrating TMS320C2xx Pipeline Operation During an Interrupt

#### Abstract

This application brief describes the behavior of the Texas Instruments (TI<sup>™</sup>) TMS320C2xx pipeline during an interrupt occurring around the SETC and CLRC instructions. This brief also explains how to change the appropriate bit in the IMR register to protect a block of code without globally disabling interrupts.

Each scenario was tested using the TMS320C209SE ('C209SE) DSP and its internal timer as the interrupt source. Pipeline operation was verified using actual code traces on the XDS511/522 emulator.

# Product Support on the World Wide Web

**L**ij

Our World Wide Web site at www.ti.com contains the most up to date product information, revisions, and additions. Users registering with TI&ME can build custom information pages and receive new product updates automatically via email.

### TMS320C2xx Pipeline Scenarios

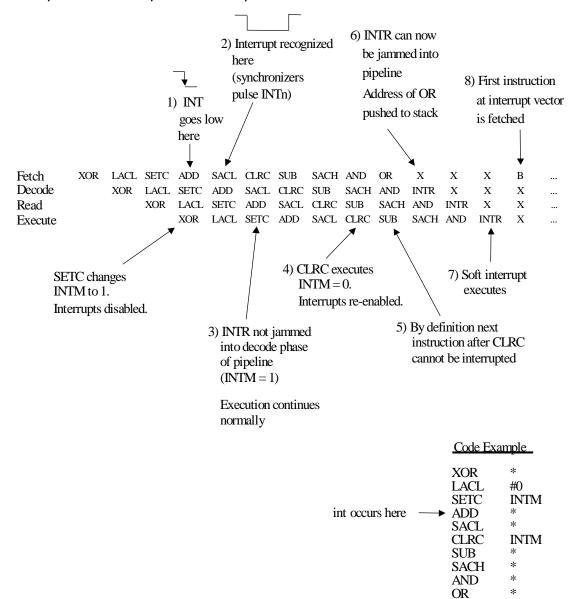

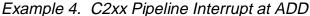

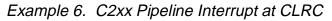

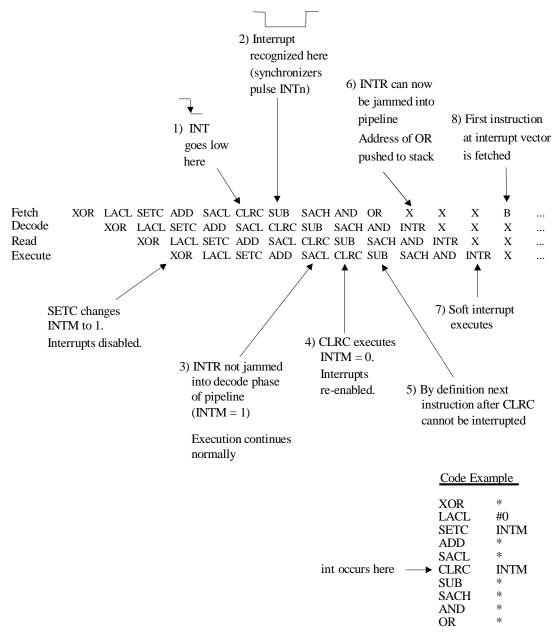

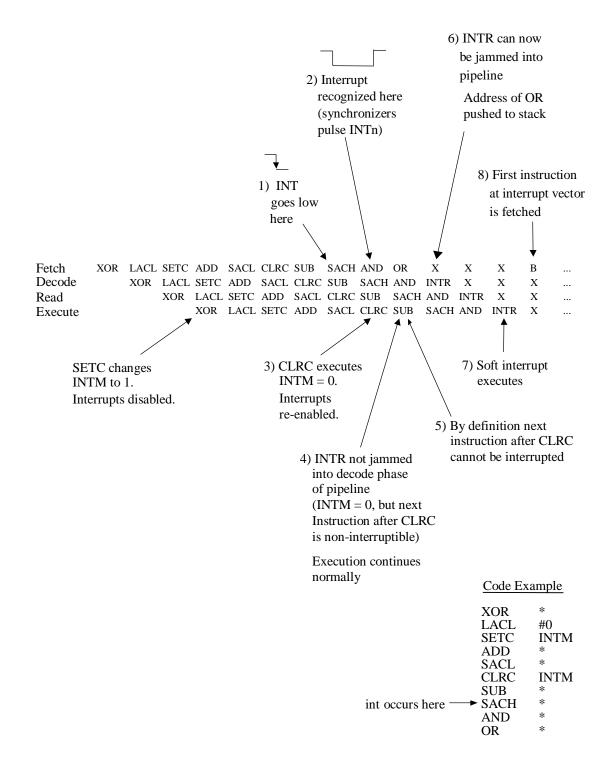

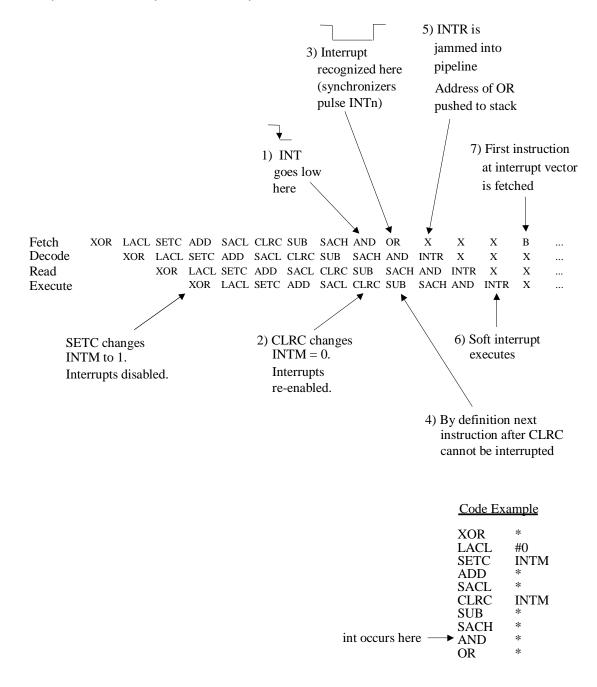

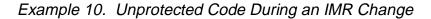

Example 1 through Example 9 show an analysis of the TMS320C2xx DSP pipeline behavior during an interrupt occurring around the SETC and CLRC instructions. Example 10 and Example 11 focus on changing the appropriate bit in the IMR register to protect a block of code without globally disabling interrupts.

For each example:

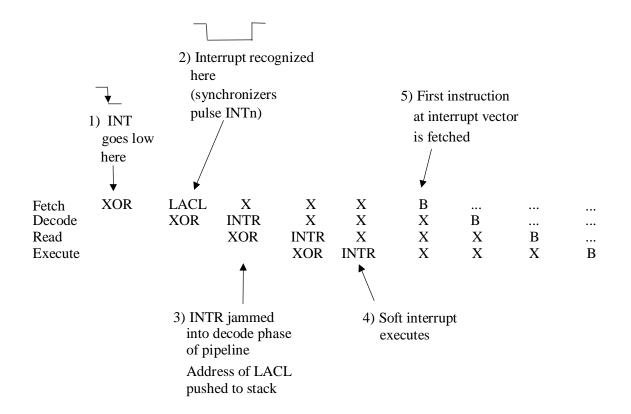

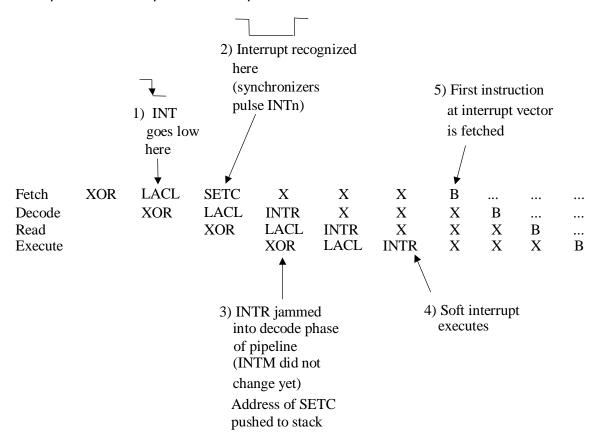

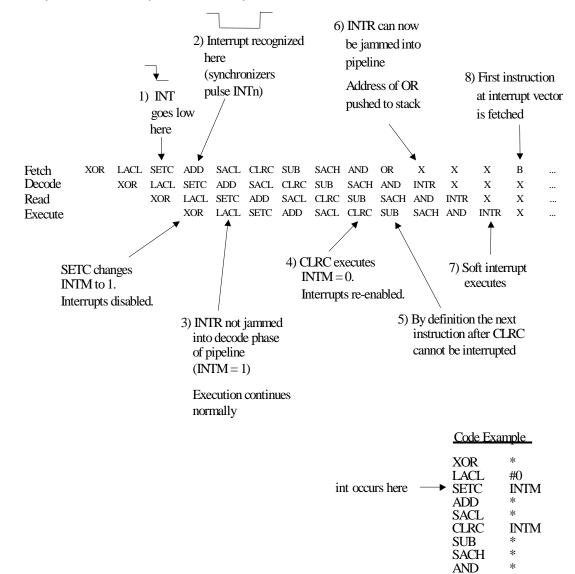

- The interrupts have a one-cycle synchronization to the CPU core. When an interrupt occurs, the synchronization circuitry actually recognizes it on the rising edge of the clock (between each cycle). If the interrupt is valid on the clock edge, the synchronization circuitry sends a low pulse to the core (interrupt recognized). There is no interrupt synchronization on the 'C2xlp core, but the diagrams can be adjusted depending on the type of synchronization you have.

- During a CLRC INTM instruction, the CPU automatically holds off any interrupt through the execution phase for it and the following instruction.

- An interrupt occurs in the CPU by jamming an INTR instruction into the decode phase of the pipeline. The address of the most recently fetched instruction is pushed to the stack so that normal operation can continue on return from the interrupt.

- When an interrupt occurs, all instructions in the pipeline will complete through the execute phase.

- □ CLRC INTM changes INTM in the execution phase. SETC INTM changes INTM in the decode phase.

- □ SACL IMR changes the IMR in the execution phase, and the change in the IMR is not realized until the next cycle.

- □ The pipeline is represented with zero wait state operation.

# Interrupt Occurring Around SETC and CLRC

Example 1. C2xx Pipeline Interrupt at XOR

|                                   | Code Example |      |  |

|-----------------------------------|--------------|------|--|

| int occurs here $\longrightarrow$ | XOR          | *    |  |

|                                   | LACL         | #0   |  |

|                                   | SETC         | INTM |  |

|                                   | ADD          | *    |  |

|                                   | SACL         | *    |  |

|                                   | CLRC         | INTM |  |

|                                   | SUB          | *    |  |

|                                   | SACH         | *    |  |

|                                   | AND          | *    |  |

|                                   | OR           | *    |  |

| Example 2. | C2xx Pipeline | Interrupt at LACL |

|------------|---------------|-------------------|

|------------|---------------|-------------------|

|                                   | Code Example                             |                          |

|-----------------------------------|------------------------------------------|--------------------------|

| int occurs here $\longrightarrow$ | XOR<br>LACL<br>SETC<br>ADD               | *<br>#0<br>INTM<br>*     |

|                                   | SACL<br>CLRC<br>SUB<br>SACH<br>AND<br>OR | *<br>INTM<br>*<br>*<br>* |

OR

\*

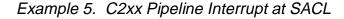

#### Example 8. C2xx Pipeline Interrupt at SACH

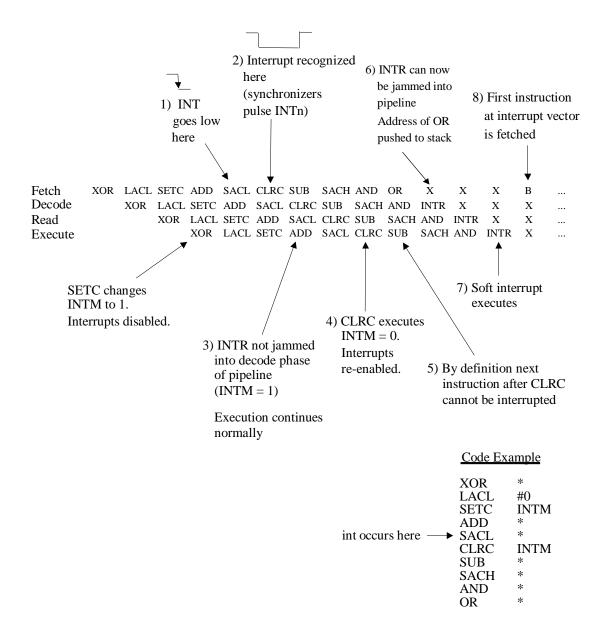

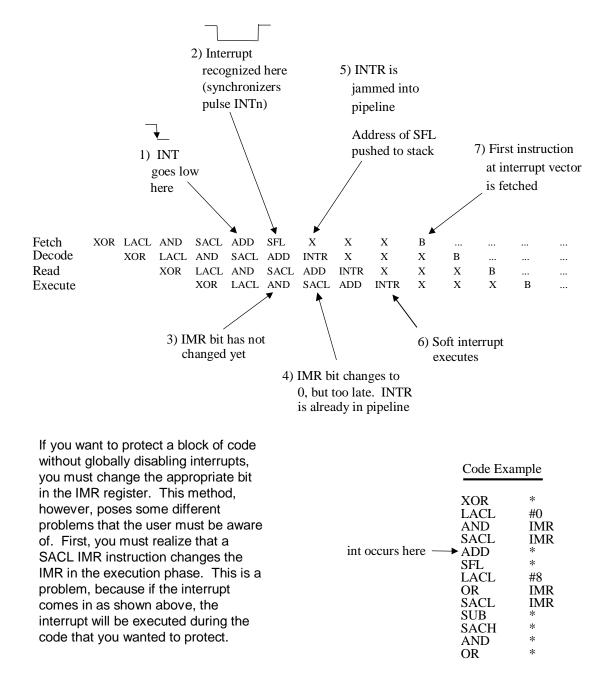

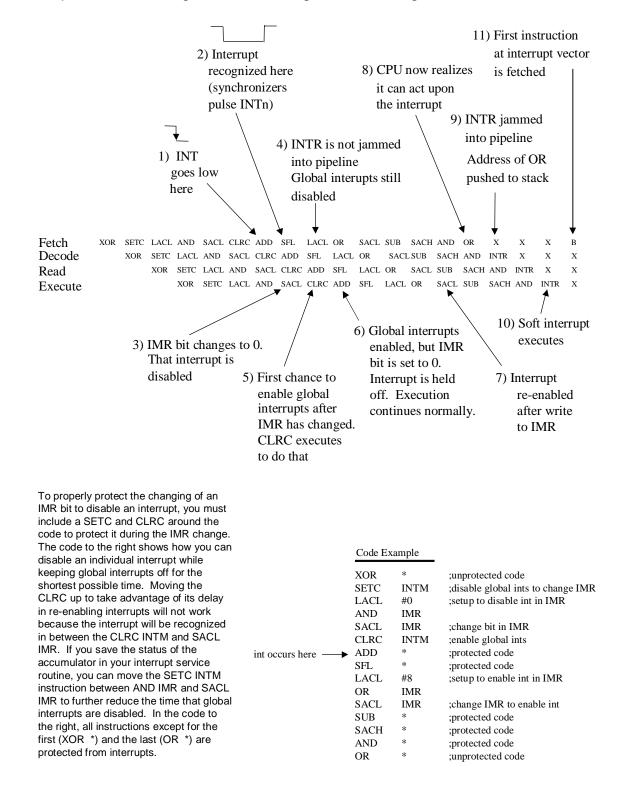

## Changing IMR Register Bit to Protect Code without Globally Disabling Interrupts

Demonstrating TMS320C2xx Pipeline Operation During an Interrupt

7

#### Example 11. Protecting the Code During an IMR Change

Demonstrating TMS320C2xx Pipeline Operation During an Interrupt