#### Logic and Computer Design Fundamentals

## Chapter 3 – Combinational Logic Design

Part 1 – Implementation Technology and Logic Design

#### **Charles Kime & Thomas Kaminski**

© 2008 Pearson Education, Inc. (Hyperlinks are active in View Show mode)

## **Overview**

- Part 1 Design Procedure

- Steps

- Specification

- Formulation

- Optimization

- Technology Mapping

- Beginning Hierarchical Design

- Technology Mapping AND, OR, and NOT to NAND or NOR

- Verification

- Manual

- Simulation

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Sildes © 2008 Pearson Education, Inc.

## **Overview** (continued)

#### Part 2 – Combinational Logic

- Functions and functional blocks

- Rudimentary logic functions

- Decoding using Decoders

- Implementing Combinational Functions with Decoders

- Encoding using Encoders

- Selecting using Multiplexers

- Implementing Combinational Functions with Multiplexers

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 3

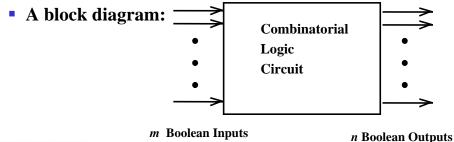

#### **Combinational Circuits**

- A combinational logic circuit has:

- A set of *m* Boolean inputs,

- A set of *n* Boolean outputs, and

- *n* switching functions, each mapping the 2<sup>m</sup> input combinations to an output such that the current output depends only on the current input values

### **Design Procedure**

- 1. Specification

- Write a specification for the circuit if one is not already available

- 2. Formulation

- Derive a truth table or initial Boolean equations that define the required relationships between the inputs and outputs, if not in the specification

- Apply hierarchical design if appropriate

- 3. Optimization

- Apply 2-level and multiple-level optimization

- Draw a logic diagram or provide a netlist for the resulting circuit using ANDs, ORs, and inverters

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 5

## **Design Procedure**

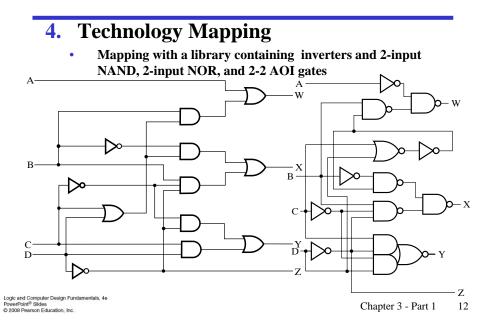

- 4. Technology Mapping

- Map the logic diagram or netlist to the implementation technology selected

- 5. Verification

- Verify the correctness of the final design manually or using simulation

#### **Design Example**

- **1.** Specification

- BCD to Excess-3 code converter

- Transforms BCD code for the decimal digits to Excess-3 code for the decimal digits

- BCD code words for digits 0 through 9: 4-bit patterns 0000 to 1001, respectively

- Excess-3 code words for digits 0 through 9: 4bit patterns consisting of 3 (binary 0011) added to each BCD code word

- Implementation:

- multiple-level circuit

- NAND gates (including inverters)

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 7

## Design Example (continued)

#### 2. Formulation

• Conversion of 4-bit codes can be most easily formulated by a truth table

| •           | Variables       | Input BCD                                                     | Output Excess-3 |

|-------------|-----------------|---------------------------------------------------------------|-----------------|

|             | - <u>BCD</u> :  | <b>ABCD</b>                                                   | WXYZ            |

|             | A,B,C,D         | 0000                                                          | 0011            |

| •           | Variables       | 0001                                                          | 0100            |

|             | - Excess-3      | 0010                                                          | 0101            |

|             |                 | 0011                                                          | 0110            |

| •           | W,X,Y,Z         | 0100                                                          | 0111            |

|             | Don't Cares     | 0101                                                          | 1000            |

|             | - BCD 1010      | $\begin{array}{c} 0 \ 1 \ 1 \ 0 \\ 0 \ 1 \ 1 \ 1 \end{array}$ | 1001<br>1010    |

|             | to 1111         |                                                               |                 |

|             |                 | 1000                                                          | 1011            |

| r Design Fu | undamentals, 4e | 1001                                                          | 1911            |

Logic and Computer Design Fundamentals, PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

### **Design Example** (continued)

### **Design Example** (continued)

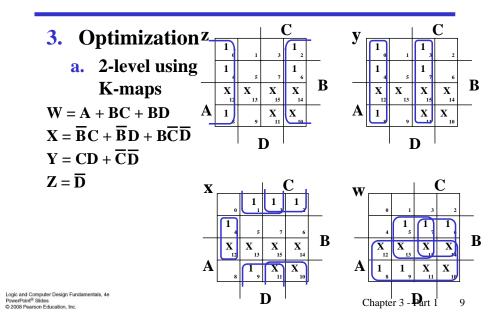

- **3.** Optimization (continued)

- b. Multiple-level using transformations W = A + BC + BD  $X = \overline{B}C + \overline{B}D + B\overline{C}\overline{D}$   $Y = CD + \overline{C}\overline{D}$   $Z = \overline{D}$  G = 7 + 10 + 6 + 0 = 23

- Perform extraction, finding factor:

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

### **Design Example** (continued)

#### **3.** Optimization (continued)

b. Multiple-level using transformations  $\mathbf{T}_1 = \mathbf{C} + \mathbf{D}$  $W = A + BT_1$  $\mathbf{X} = \overline{\mathbf{B}}\mathbf{T}_1 + \mathbf{B}\overline{\mathbf{C}}\overline{\mathbf{D}}$  $\mathbf{Y} = \mathbf{C}\mathbf{D} + \overline{\mathbf{C}}\overline{\mathbf{D}}$  $\mathbf{Z} = \overline{\mathbf{D}}$ G = 19 An additional extraction not shown in the text since it • uses a <u>Boolean transformation</u>:  $(\overline{C}\overline{D} = \overline{C} + \overline{D} = \overline{T}_1)$ :  $W = A + BT_1$  $\mathbf{X} = \overline{\mathbf{B}} \mathbf{T}_1 + \mathbf{B} \overline{\mathbf{T}}_1$  $\mathbf{Y} = \mathbf{C}\mathbf{D} + \overline{\mathbf{T}}_1$  $\mathbf{Z} = \overline{\mathbf{D}}$ G = 2 + 1 + 4 + 6 + 4 + 0 = 16!Logic and Computer Design Funda PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc. Chapter 3 - Part 1 11

### **Design Example** (continued)

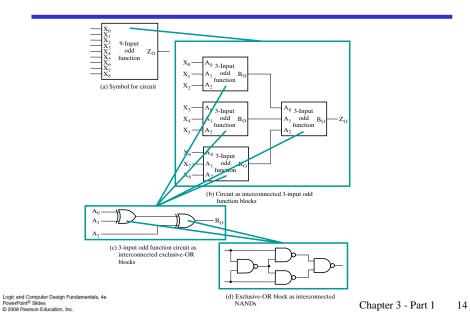

## **Beginning Hierarchical Design**

- To control the complexity of the function mapping inputs to outputs:

- Decompose the function into smaller pieces called *blocks*

- Decompose each block's function into smaller blocks, repeating as necessary until all blocks are small enough

- Any block not decomposed is called a primitive block

- The collection of all blocks including the decomposed ones is a *hierarchy*

- Example: 9-input parity tree (see next slide)

- Top Level: 9 inputs, one output

- 2nd Level: Four 3-bit odd parity trees in two levels

- 3rd Level: Two 2-bit exclusive-OR functions

- Primitives: Four 2-input NAND gates

- Design requires 4 X 2 X 4 = 32 2-input NAND gates

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 13

### **Hierarchy for Parity Tree Example**

### **Reusable Functions**

- Whenever possible, we try to decompose a complex design into common, *reusable* function blocks

- These blocks are

- verified and well-documented

- placed in libraries for future use

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 15

## **Top-Down versus Bottom-Up**

- A *top-down design* proceeds from an abstract, highlevel specification to a more and more detailed design by decomposition and successive refinement

- A *bottom-up design* starts with detailed primitive blocks and combines them into larger and more complex functional blocks

- Design usually proceeds top-down to known building blocks ranging from complete CPUs to primitive logic gates or electronic components.

- Much of the material in this chapter is devoted to learning about combinational blocks used in top-down design.

## **Technology Mapping**

- Mapping Procedures

- To NAND gates

- To NOR gates

- Mapping to multiple types of logic blocks in covered in the reading supplement: Advanced Technology Mapping.

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Sildes © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 17

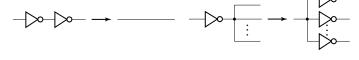

## Mapping to NAND gates

- Assumptions:

- · Gate loading and delay are ignored

- Cell library contains an inverter and *n*-input NAND gates, *n* = 2, 3, ...

- An AND, OR, inverter schematic for the circuit is available

- The mapping is accomplished by:

- Replacing AND and OR symbols,

- Pushing inverters through circuit fan-out points, and

- Canceling inverter pairs

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Sildes © 2008 Pearson Education, Inc.

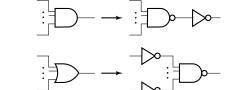

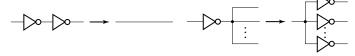

### **NAND Mapping Algorithm**

**1.** Replace ANDs and ORs:

- 2. Repeat the following pair of actions until there is at most one inverter between :

- a. A circuit input or driving NAND gate output, and

- **b.** The attached NAND gate inputs.

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 19

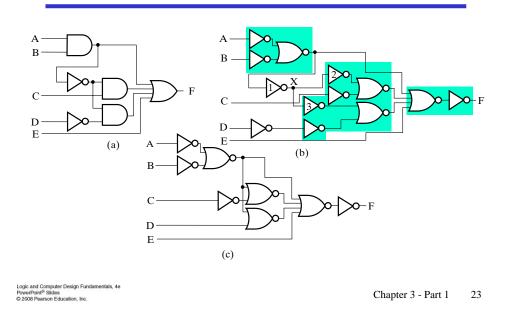

## **NAND Mapping Example**

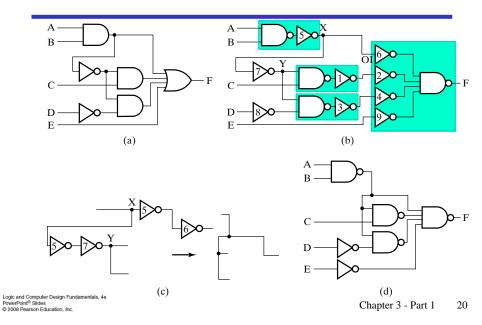

## Mapping to NOR gates

#### • Assumptions:

- · Gate loading and delay are ignored

- Cell library contains an inverter and *n*-input NOR gates, *n* = 2, 3, ...

- An AND, OR, inverter schematic for the circuit is available

#### The mapping is accomplished by:

- Replacing AND and OR symbols,

- Pushing inverters through circuit fan-out points, and

- Canceling inverter pairs

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 21

## **NOR Mapping Algorithm**

**1.** Replace ANDs and ORs:

- 2. Repeat the following pair of actions until there is at most one inverter between :

- a. A circuit input or driving NAND gate output, and

- **b.** The attached NAND gate inputs.

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

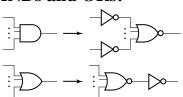

## **NOR Mapping Example**

## Verification

- Verification show that the final circuit designed implements the original specification

- Simple specifications are:

- truth tables

- Boolean equations

- HDL code

- If the above result from <u>formulation</u> and are not the <u>original specification</u>, it is critical that the formulation process be flawless for the verification to be valid!

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

### **Basic Verification Methods**

- Manual Logic Analysis

- Find the truth table or Boolean equations for the final circuit

- Compare the final circuit truth table with the specified truth table, or

- Show that the Boolean equations for the final circuit are equal to the specified Boolean equations

- Simulation

- Simulate the final circuit (or its netlist, possibly written as an HDL) and the specified truth table, equations, or HDL description using test input values that fully validate correctness.

- The obvious test for a combinational circuit is application of all possible "care" input combinations from the specification

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

Chapter 3 - Part 1 25

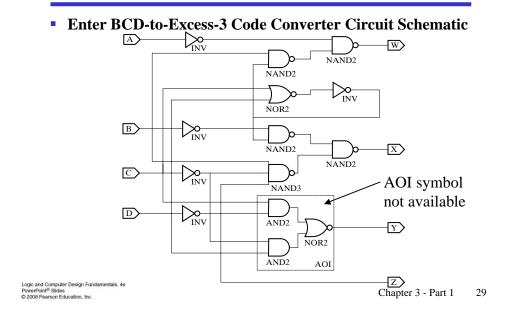

#### **Verification Example: Manual Analysis**

- BCD-to-Excess 3 Code Converter

- Find the SOP Boolean equations from the final circuit.

- Find the truth table from these equations

- Compare to the formulation truth table

- Finding the Boolean Equations:  $T_1 = \overline{\overline{C} + \overline{D}} = C + D$   $W = \overline{\overline{A}} (\overline{T_1 B}) = A + B T_1$   $X = (T_1 B) (B \overline{C} \overline{D}) = \overline{B} T_1 + B \overline{C} \overline{D}$  $Y = \overline{C\overline{D} + \overline{C}D} = CD + \overline{C}\overline{D}$

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

#### **Verification Example: Manual Analysis**

Find the circuit truth table from the equations and compare

| to specification truth table: |                 |  |  |

|-------------------------------|-----------------|--|--|

| Input BCD                     | Output Excess-3 |  |  |

| A B C D                       | WXYZ            |  |  |

| 0000                          | 0011            |  |  |

| 0001                          | 0100            |  |  |

| 0010                          | 0101            |  |  |

| 0011                          | 0110            |  |  |

| 0100                          | 0111            |  |  |

| 0101                          | 1000            |  |  |

| 0110                          | 1001            |  |  |

| 0111                          | 1010            |  |  |

| 1000                          | 1011            |  |  |

| 1001                          | 1011            |  |  |

Logic and Computer Design Fundamentals, 4e PowerPoint® Slides © 2008 Pearson Education, Inc. The tables match!

Chapter 3 - Part 1 27

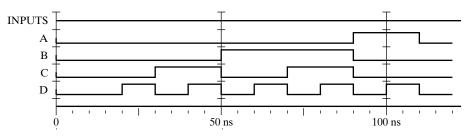

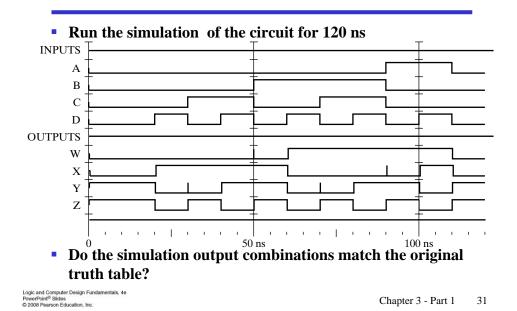

# Verification Example: Simulation

#### Simulation procedure:

- Use a schematic editor or text editor to enter a gate level representation of the final circuit

- Use a waveform editor or text editor to enter a test consisting of a sequence of input combinations to be applied to the circuit

- This test should guarantee the correctness of the circuit if the simulated responses to it are correct

- Short of applying all possible "care" input combinations, generation of such a test can be difficult

#### **Verification Example: Simulation**

#### **Verification Example: Simulation**

Enter waveform that applies all possible input combinations:

Are all BCD input combinations present? (Low is a 0 and high is a one)

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.

#### **Verification Example: Simulation**

## **Terms of Use**

- All (or portions) of this material © 2008 by Pearson Education, Inc.

- Permission is given to incorporate this material or adaptations thereof into classroom presentations and handouts to instructors in courses adopting the latest edition of Logic and Computer Design Fundamentals as the course textbook.

- These materials or adaptations thereof are not to be sold or otherwise offered for consideration.

- This Terms of Use slide or page is to be included within the original materials or any adaptations thereof.

Logic and Computer Design Fundamentals, 4e PowerPoint<sup>®</sup> Slides © 2008 Pearson Education, Inc.