# HMS39C7092

32 비트 임베디드 플래시 MCU

사용자 설명서 한글 ver 1.3a

Released: February. 2001

Revision History:

October 9, 2001 Ver 1.05 PMU 소트프 리셋 레지스터 쓰기 전용으로 변경

타이머 PWM 모드 듀티 0%의 경우 1 클럭 펄스 발생

캡쳐 모드 딜레이

버스 컨트롤러 외부 메모리 바이트 버스시 Thumb 실행불가

외부 웨이트 입력은 로우-액티브만 지원 nRD 신호가 nCS 타이밍내에서만 활성화

ADC 핀의 GPIO 기능 삭제(ADC 입력만 사용)

January 8, 2002 Prel 6 ADC/P7 Aprill 29, 2003 Ver 1.0 설명서 보정

May 20, 2003 한글 1.0 한글화 및 플래시 파라메타 보정

Jun 28, 2003 한글 1.1 교정판 Industrial 온도 스펙

March 30, 2005 한글 1.3 내부 플래시 프로그램 설명서의 제외/별도 문서화

한글 1.3a 버스 타이밍 오류 수정

ARM<sup>®</sup>은 Advanced RISC Machine 社의 등록 상표입니다. ARM7TDMI 는 ARM 社에서 설계하였습니다.

본 문서의 내용은 사전 양해 없이 바뀔 수 있습니다.

본 문서는 저희 제품을 응용하기 위한 설명 용도로 사용되면, 매그나칩에서는 본 문서인해 본 제품을 사용하는 데에 따른 제 3 사의 저작권 및 특허 침해에 관련된 어떠한 내용에 대해서도 책임을 지지 않습니다. 본 문서는 매그나칩 및 다른 제 3 자의 어떠한 특허권의 소유에 대한 내용도 포함하고 있지 않습니다.

이 제품들은 일반 전자 장치에 사용되도록 고려되었습니다 (사무기, 통신기기, 측정장비, 가전 등).

이 제품들을 고성능, 고신뢰성 및 안전에 관련된 분야 (원자력 제어, 우주/항공, 교통신호, 연소제어 및 모든 안전관련 장비 등)에 사용하시기 전에 반드시 매그나칩에 문의 하여 주시기 바랍니다. 사전에 저희 회사와 상의 없이 개발된 제품에 의해 일어난 손해에 대해서는 책임을 지지 않습니다.

Copyright 2003 Magnachip Semiconductor, Inc.

All Rights Reserved

# 목 차

| 제 1 징 | }     |                          | . 13 |

|-------|-------|--------------------------|------|

| 소     | 노개    |                          | . 13 |

|       | 1.1   | 개요                       | . 14 |

|       | 1.2   | 특징                       | . 15 |

|       | 1.3   | 핀 구성                     | . 16 |

|       | 1.4   | 동작 모드                    | . 21 |

|       | 1.5   | 메모리 맵                    | . 25 |

| 제 2 장 | }     |                          | . 29 |

| Α     | RM7TD | OMI 코어                   | . 29 |

|       | 2.1   | 개요                       | . 30 |

|       | 2.2   | 특징                       | . 30 |

|       | 2.3   | 코어 블럭도                   | . 31 |

|       | 2.4   | 명령어 셋                    | . 32 |

|       |       | 2.4.1 ARM 명령어            | . 32 |

|       |       | 2.4.2 THUMB 명령어          |      |

|       |       | 2.4.3 프로그램 스테이터스 레지스터    |      |

|       |       | 2.4.3.1 컨디션 코드 플래그       |      |

|       |       | 2.4.3.2 제어 비트            |      |

|       |       | 2.4.4 ARM 명령어            |      |

|       |       |                          |      |

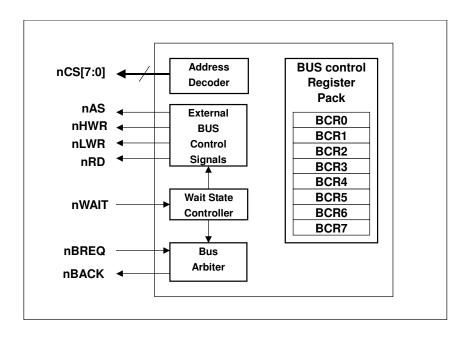

| 바     | l스 컨토 | 트롤러                      |      |

| 3.    | .1    | 개요                       |      |

|       |       | 3.1.1 특징                 |      |

|       |       | 3.1.2 핀 구성               |      |

|       | 3.2   | , a = 2 , 1 , 1 , 2      |      |

|       |       | 3.2.1 버스 설정 레지스터         |      |

|       | 3.3   | , 2 - 2 , , 0 ,          |      |

|       |       | 3.3.1 메모리 영역             |      |

|       |       | 3.3.2 메모리 영역 설정          |      |

|       |       | 3.3.3 칩셀렉트 신호            |      |

|       | 3.4   | , = , = , , ,            |      |

|       |       | 3.4.1 개요                 |      |

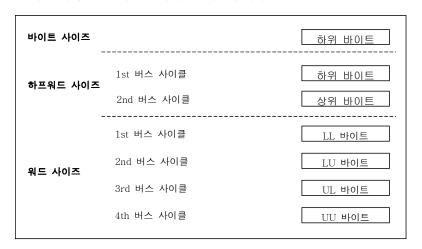

|       |       | 3.4.2 바이트 단위 쓰기 제어       | . 50 |

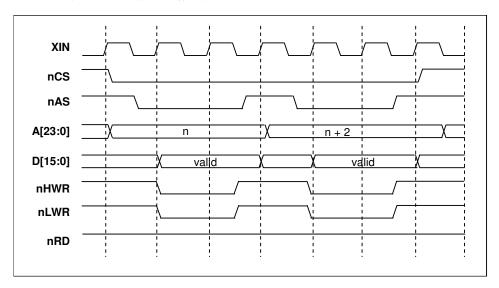

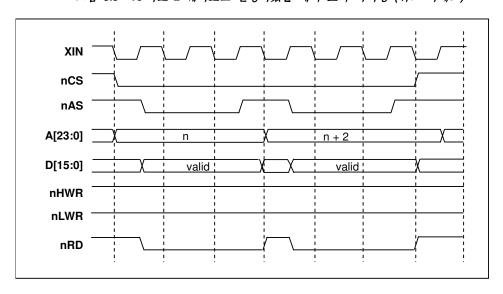

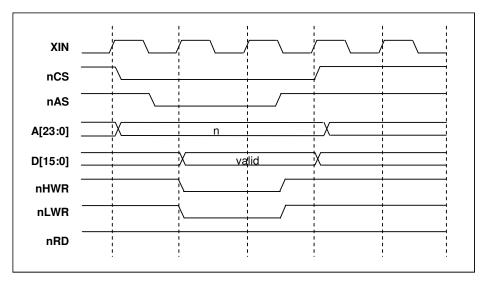

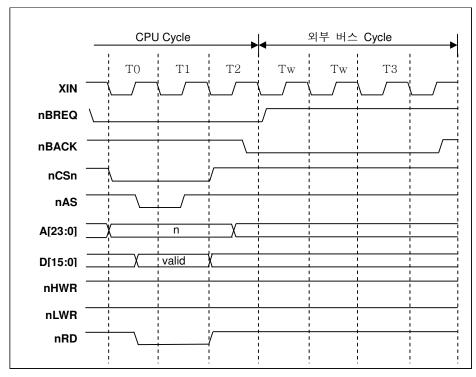

|       |       | 3.4.3 기본적인 버스 컨트롤 신호 타이밍 |      |

|       |       | 3.4.4 웨이트 컨트롤            | . 55 |

| _111  | 1     | 3.4.5 버스 아비터             |      |

|       |       |                          |      |

|       |       | 트롤러                      |      |

| 4.    |       | 게요                       |      |

|       | 4.2   | 핀 기능 설명                  | . 60 |

|                | 4.3   | 레지스터 설명                                            | 61 |

|----------------|-------|----------------------------------------------------|----|

|                |       | 4.3.1 레지스터 메모리 맵                                   | 61 |

|                |       | 4.3.2 PINMUX 레지스터                                  | 62 |

|                |       | 4.3.3 MCU 장치 코드 레지스터 (0x0900_002C 읽기전용)            | 66 |

| 제 5 장          |       |                                                    | 67 |

| 전              | [원 관리 | 위부 (PMU)                                           | 67 |

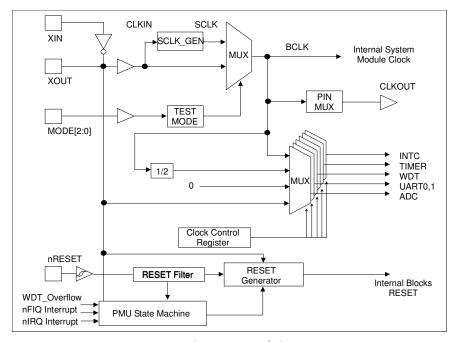

|                | 5.1   | 개요                                                 | 68 |

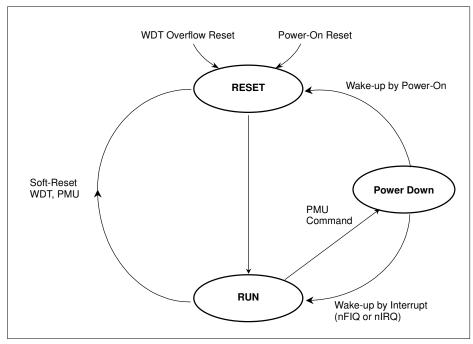

|                | 5.2   | 동작 모드                                              | 69 |

|                |       | 5.2.1 개요                                           |    |

|                |       | 5.2.2 리셋 및 동작 모드                                   |    |

|                | 5.3   | 전력 관리부 레지스터 맵                                      |    |

|                | 5.4   | 레지스터 설명                                            |    |

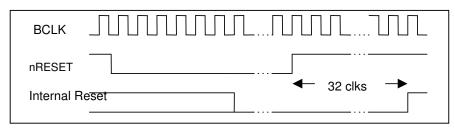

|                | 5.5   | 신호 타이밍                                             |    |

|                |       | 5.5.1 파워 온 리셋                                      |    |

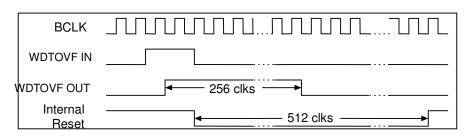

|                |       | 5.5.2 와치독 타이머 오버플로우                                |    |

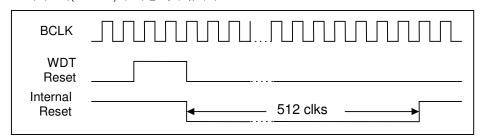

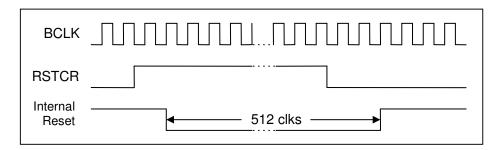

| N = -1         |       | 5.5.3 소프트리셋                                        |    |

|                |       | 7) = 2-7 (NITO)                                    |    |

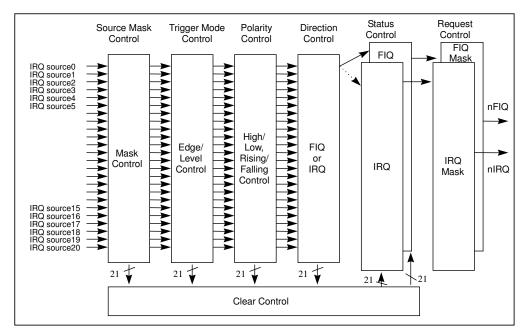

| 인              |       | 컨트롤러 (INTC)                                        |    |

|                | 6.1   | 개요                                                 |    |

|                |       | 6.1.1       인터럽트 소스         6.1.2       인터럽트 신호 제어 |    |

|                | 6.2   | 인터럽트 컨트롤러 레지스터                                     |    |

| 괴] <b>フ</b> 지- | -     | 인터럽트 선트들다 네시스터                                     |    |

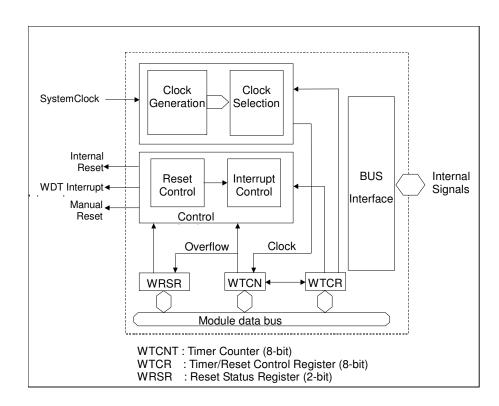

|                |       | 사이머 (WDT)                                          |    |

| 7              | 7.1   | 개요                                                 |    |

|                | 7.1   | 와치독 타이머 개요                                         |    |

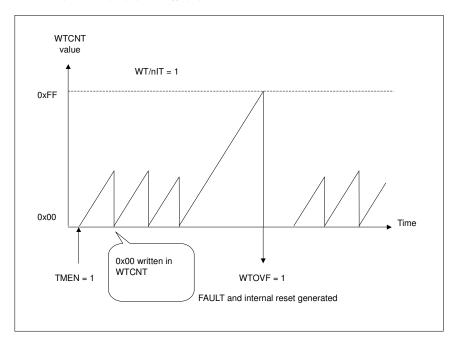

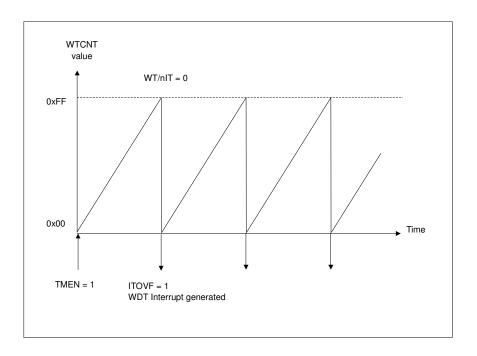

|                | 7.3   | 와치독 타이머 동작                                         |    |

|                | 7.0   | 7.3.1 오버플로우 플래그 세트 및 클리어 타이밍                       |    |

|                | 7.4   | 와치독 타이머 메모리 맵                                      |    |

|                | 7.5   | 와치독 타이머 레지스터 설명                                    |    |

|                | 7.6   | 레지스터 설정 예                                          |    |

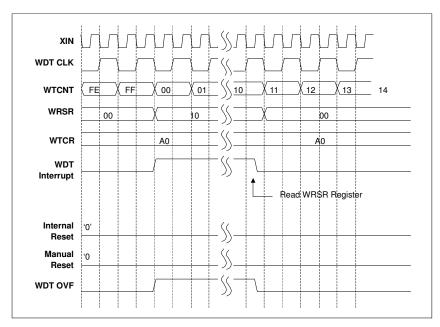

|                |       | 7.6.1 인터벌 타이머 모드                                   |    |

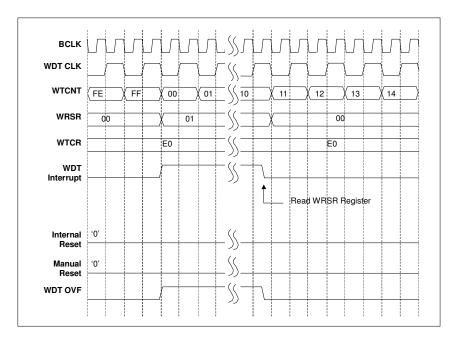

|                |       | 7.6.2 내부 리셋을 금지 시의 와치독 타이머 모드                      |    |

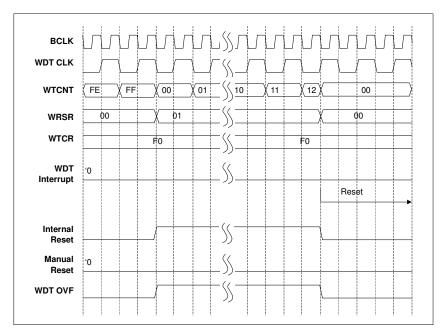

|                |       | 7.6.3 파워 온 리셋 시의 와치독 타이머 모드                        | 96 |

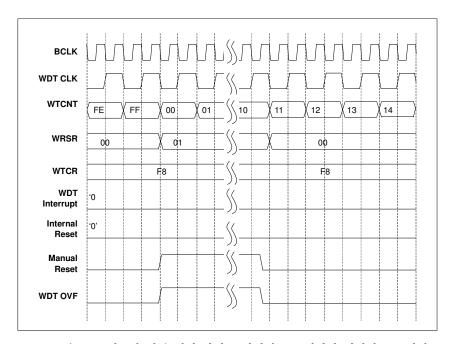

|                |       | 7.6.4 매뉴얼 리셋시의 와치독 타이머 모드                          | 97 |

|                |       |                                                    |    |

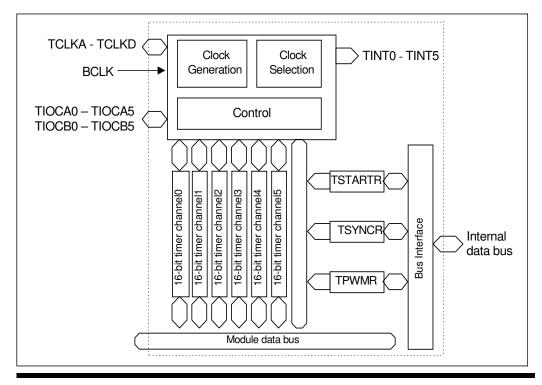

| 범              | 용 타이  | 마 (GPT)                                            | 99 |

| 8.             |       | 개요1                                                | 00 |

|                |       | 8.1.1 범용 타이머 개요1                                   | 01 |

|                | 8.2   | 범용 타이머 메모리 맵1                                      | 02 |

|                |       | 8.2.1 레지스터1                                        | 02 |

|                |       | 8.2.2 범용 타이머 레지스터 설명1                              |    |

|                |       | 8.2.2.1 타이머 글로벌 컨트롤 레지스터1                          | 03 |

|         |      | 8.2.2.2 타이머 채널 컨트롤 레지스터    | . 104 |

|---------|------|----------------------------|-------|

|         | 8.3  | 범용 타이머의 동작                 | . 108 |

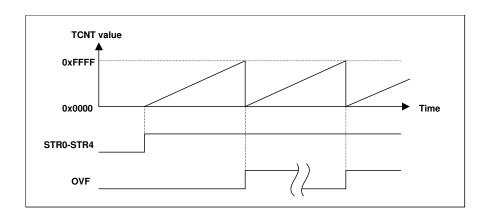

|         |      | 8.3.1 프리런 모드               | . 109 |

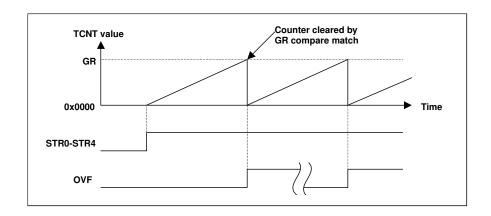

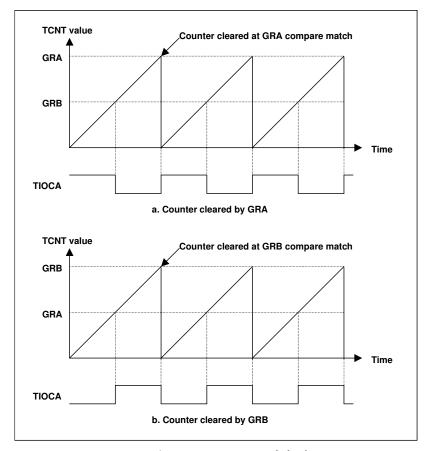

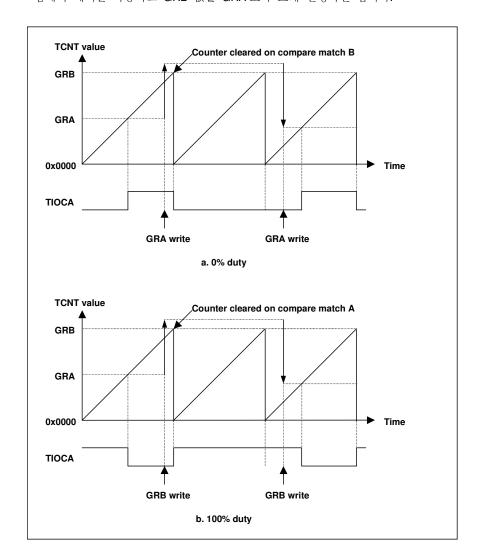

|         |      | 8.3.2 컴페어 매치 모드            | 111   |

|         |      | 8.3.3 입력 캡쳐 모드             |       |

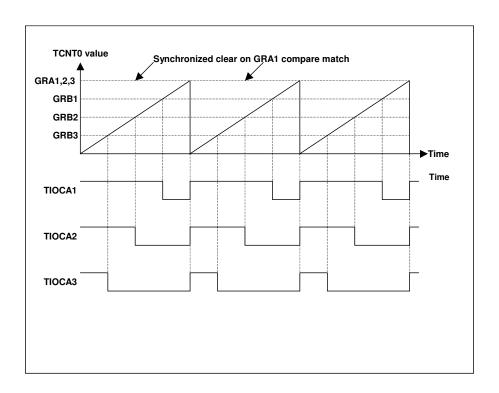

|         |      | 8.3.4 동기 클리어 카운트 모드        | . 114 |

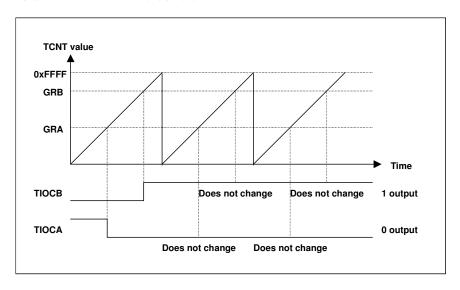

|         |      | 8.3.5 진폭 변조(PWM) 모드        | 115   |

|         |      | 8.3.5.1 진폭 변조(PWM) 모드의 동작  | . 115 |

| 제 9 장   |      |                            |       |

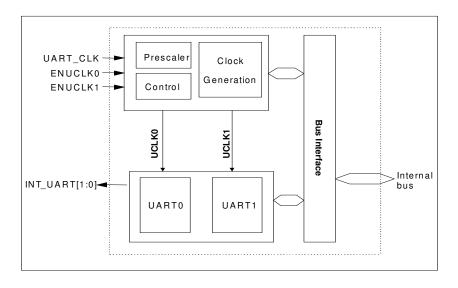

| 비동      | -기 2 | 직렬 통신 포트 (UART)            | . 119 |

|         |      |                            |       |

|         | 9.2  | 특징                         | . 121 |

|         | 9.3  | UART 신호들의 정의               | . 121 |

|         | 9.4  |                            |       |

|         | 9.5  |                            |       |

|         | 9.6  | UART 의 동작                  |       |

|         |      | 9.6.1 FIFO 인터럽트 모드에서의 동작   | . 134 |

|         |      | 9.6.2 FIFO Polled 모드에서의 동작 |       |

|         | 9.7  |                            |       |

| 제 10 장. |      |                            |       |

|         |      | ) 포트 (GPIO)                |       |

|         | 10.1 |                            |       |

|         | 10.2 | 2 범용 I/O 포트 레지스터           |       |

|         |      | 10.2.1 레지스터 메모리 맵          |       |

|         |      | 10.2.2 레지스터 설명             |       |

|         | 10.3 |                            |       |

| 제 11 장. |      |                            |       |

|         |      | RAM                        |       |

| ,, 0    | 11.1 |                            |       |

|         | 11.2 |                            |       |

| 제 12 장. |      |                            |       |

|         |      | 래시 메모리                     |       |

| ,, 0    | 12.1 |                            |       |

|         | 12.2 |                            |       |

|         | 12.3 |                            |       |

|         | 12.4 |                            |       |

|         | 12.5 |                            |       |

|         | 0    | 12.5.1 부트 모드               |       |

|         |      | 12.5.2 유저 프로그램 모드          | . 158 |

| 제 13 장  |      |                            |       |

|         |      | H터                         |       |

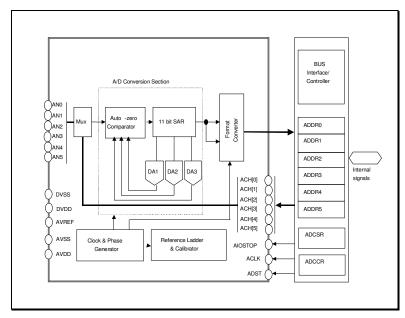

| 13.1    |      | 개요                         |       |

|         |      | 13.1.1 특징                  |       |

|         |      |                            |       |

|         | 13.  | .1.2 핀 구성     | 163 |

|---------|------|---------------|-----|

|         | 13.2 | A/D 컨버터 레지스터들 | 164 |

|         | 13.  | .2.1 레지스터 설명  | 165 |

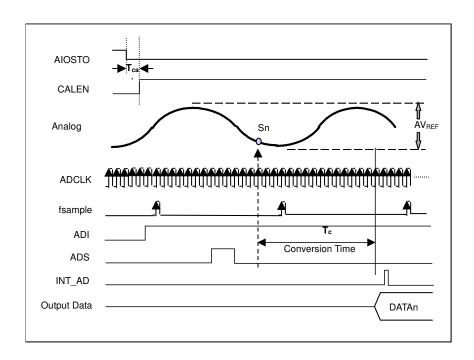

|         | 13.3 | 동작            | 167 |

|         | 13.4 | 인터럽트          | 168 |

|         | 13.5 | 사용시 주의사항      | 169 |

|         | 13.6 | 예제            | 172 |

| 제 14 장. |      |               | 175 |

| 전기      | 적 특성 |               | 175 |

|         | 14.1 | 동작의 절대 한계치    | 176 |

|         | 14.2 | 권장 동작 조건      |     |

|         | 14.3 | DC 특성         | 177 |

|         | 14.4 | AC 특성         |     |

|         | 14.4 | AD 변환 특성      | 180 |

|         |      | 동작 타이밍        |     |

|         |      | .5.1 클럭 타이밍   |     |

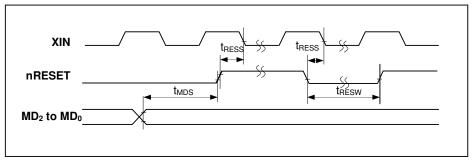

|         | 14.  | .5.2 리셋 타이밍   | 181 |

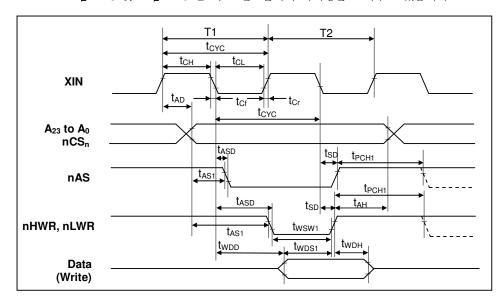

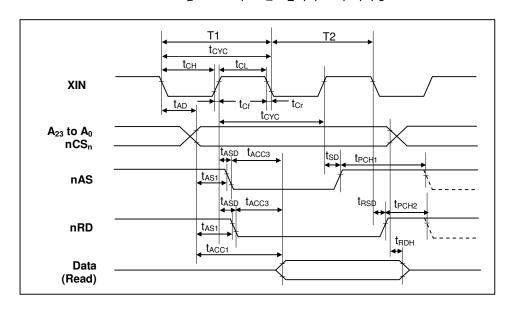

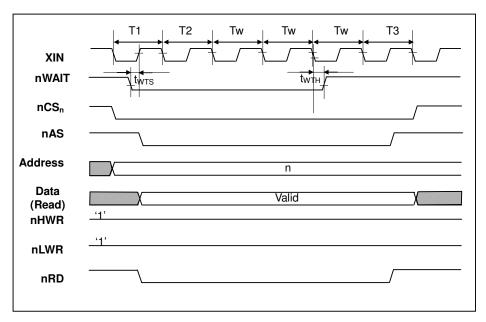

|         | 14.  | 5.3 버스 타이밍    | 182 |

|         |      |               |     |

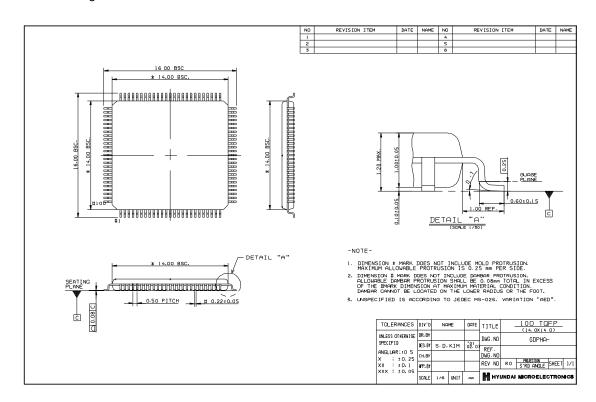

### A-1 Package Dimension

# 그림목차

| 그림 | 1.1  | 핀 배치                                   |      |

|----|------|----------------------------------------|------|

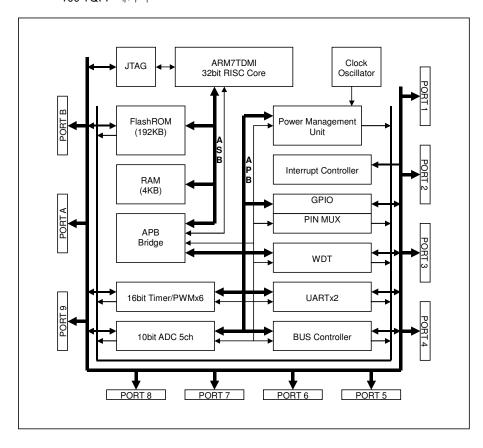

| 그림 | 1.2  | HMS39C7092 블록도                         | . 15 |

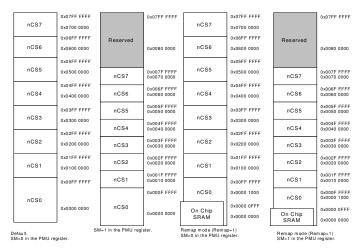

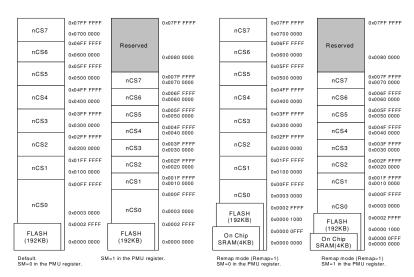

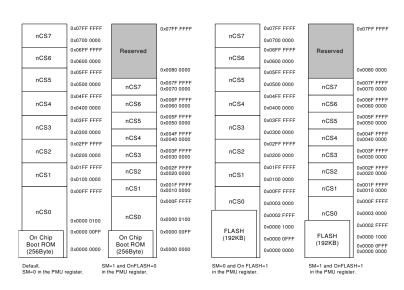

| 그림 | 1.3  | HMS39C7092 메모리 뎁                       | . 25 |

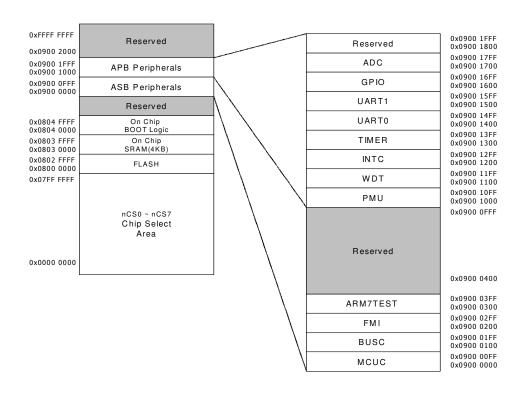

| 그림 | 1.4  | 모드 2,3의 메모리 맵                          | . 26 |

| 그림 | 1.5  | 모드 4와 모드 5의 메모리 맵                      | . 26 |

| 그림 | 1.6  | 모드 6의 메모리 맵                            |      |

| 그림 | 1.6  | 모드 7의 메모리 맵                            |      |

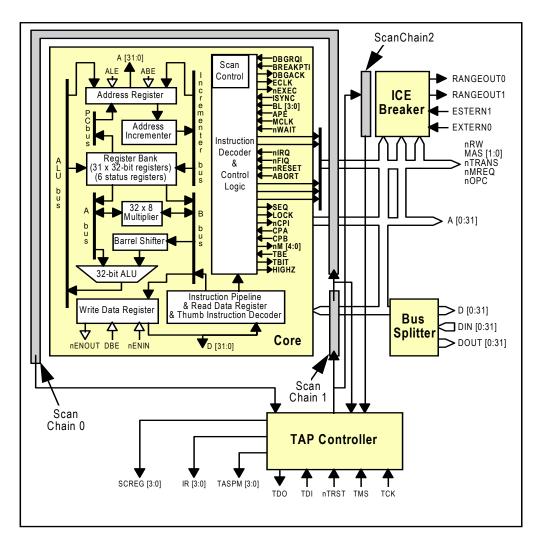

| 그림 | 2.1  | ARM7TDMI 코어 블록도                        | . 31 |

| 그림 | 2.2  | ARM 명령어 집합 형태                          |      |

| 그림 | 2.3  | ARM 상태에서의 레지스터 구성                      | . 34 |

| 그림 | 2.4  | THUMB 명령어 셋 포맷                         | . 35 |

| 그림 | 2.5  | THUMB 상태에서의 레지스터 구성                    |      |

| 그림 | 2.6  | THUMB 상태에서 ARM 상태로의 레지스터 변환            |      |

| 그림 | 2.7  | 프로그램 스테이터스 레지스터 포맷                     | . 38 |

| 그림 | 3.1  | 버스 컨트롤러 블럭도                            |      |

| 그림 | 3.2  | 외부 공간 메모리 맵                            |      |

| 그림 |      | 8비트 억세스 시의 데이터 크기 및 정렬                 |      |

| 그림 |      | 16 비트 억세스 시의 데이터 크기 및 정렬               |      |

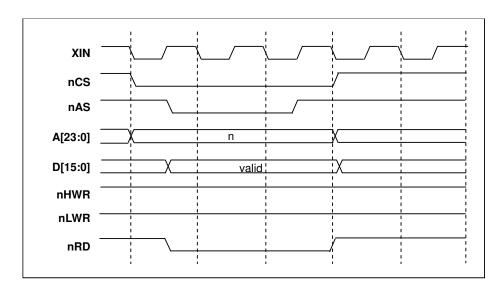

| 그림 |      | 16 비트 2 웨이트로 설정 되었을 때의 쓰기 타이밍 (워드 억세스) |      |

| 그림 | 3.6  | 16 비트 2 웨이트로 설정 되었을 때의 읽기 타이밍 (워드 억세스) |      |

| 그림 | 3.7  | 16 비트 2 웨이트로 설정 시 쓰기 타이밍 (하프워드 억세스)    |      |

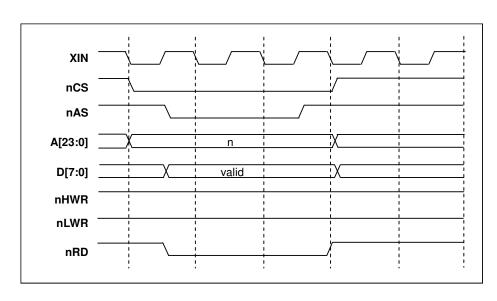

| 그림 |      | 16 비트 2 웨이트로 설정 시 읽기 타이밍 (하프워드 억세스)    |      |

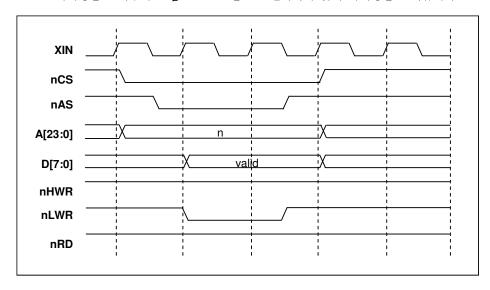

| 그림 | 3.9  | 16 비트 2 웨이트로 설정 시 쓰기 타이밍 (바이트 억세스)     |      |

| 그림 | 3.10 | 16 비트 2 웨이트로 설정 시 읽기 타이밍 (바이트 억세스)     |      |

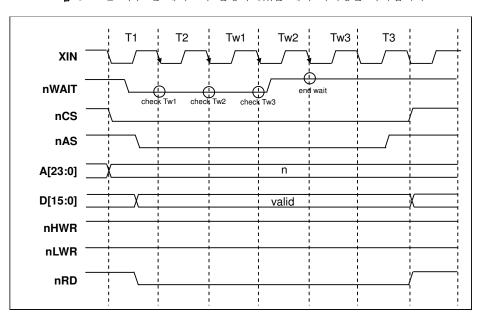

| 그림 | 3.11 | 웨이트 삽입의 예                              |      |

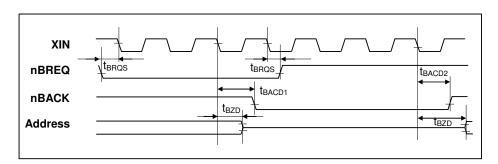

| _  | 3.18 | 외부 버스 마스터 동작의 예                        |      |

| 그림 | 5.1  | PMU 블럭도                                |      |

| 그림 | -    | 동작 모드 별 상태 변화도                         |      |

| 그림 | 5.3  | 외부 리셋 타이밍                              |      |

| 그림 | -    | 와치독 타이머 오버플로우 타이밍                      | . 75 |

| 그림 | 5.5  | 와치독 타이머의 소프트리셋 타이밍                     |      |

| 그림 |      | PMU의 소프트리셋 타이밍                         |      |

| 그림 | 6.1  | 인터럽트 발생 흐름도                            |      |

| 그림 |      | 와치독 타이머 블럭도                            |      |

|    |      | 와치독 타이머 모드 동작 예                        |      |

|    |      | 인터벌 타이머 모드 동작 예                        |      |

|    |      | 인터벌 타이머 모드에서의 인터럽트 클리어                 |      |

|    |      | 와치독 타이머 모드에서의 인터럽트 클리어                 |      |

| 그림 | 7.6  | 와치독 모드에서의 인터럽트 클리어 및 리셋                |      |

| 그림 |      | 매뉴얼 리셋 시의 와치독 타이머 모드에서의 인터럽트 클리어       |      |

| 그림 | 8.1  | 타이머 채널 블럭도                             | 100  |

| 그림 | 8.2  | 프리런 모드의 동작               | 109 |

|----|------|--------------------------|-----|

| 그림 | 8.3  | 인터벌 카운터 모드의 동작           |     |

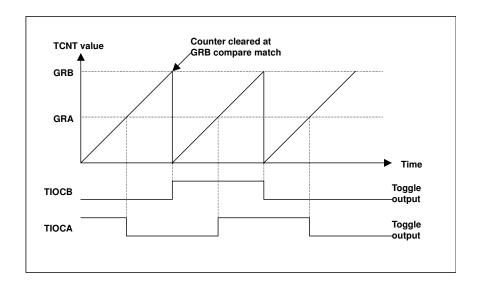

| 그림 | 8.4  | 타이머 출력 0,1 예             | 111 |

| 그림 | 8.5  | 타이머 출력 반전 예              | 112 |

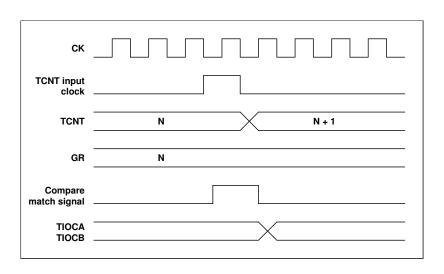

| 그림 | 8.6  | 컴페어 매치 기능 동작의 타이밍        | 112 |

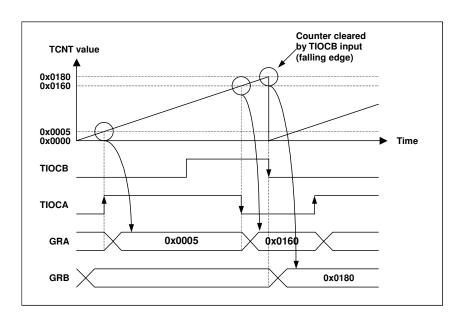

| 그림 | 8.7  | 입력 캡쳐 모드의 동작 예           |     |

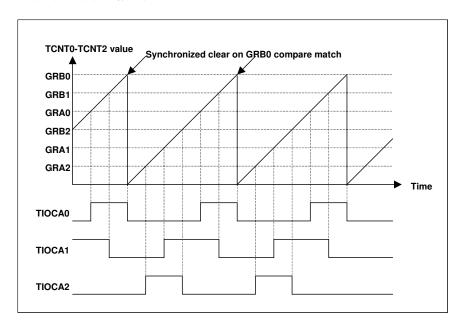

| 그림 | 8.8  | 동기화 모드 동작의 예             | 114 |

| 그림 | 8.9  | PWM 모드 동작의 예 1           |     |

| 그림 | 8.10 | PWM 모드 동작의 예 2           |     |

| 그림 | 8.11 | 리셋 동기 PWM 모드 동작의 예       | 117 |

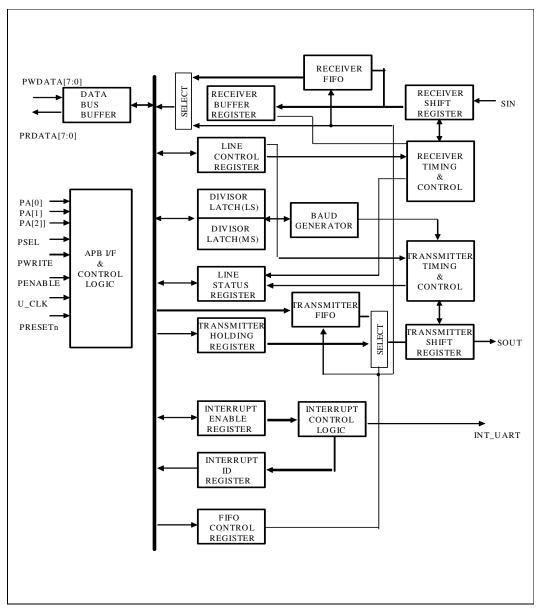

| 그림 | -    | UART 의 블럭도               |     |

| 그림 | 9.2  | UART의 내부 블록도             |     |

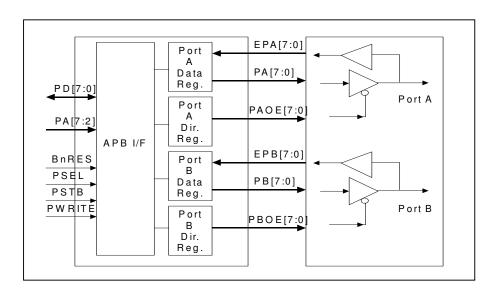

| 그림 |      | GPIO 블럭도 (포트 A, 포트 8의 예) |     |

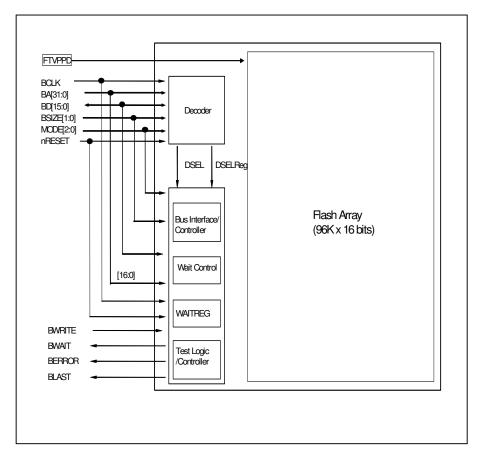

|    |      | 플래시 메모리 구성도              |     |

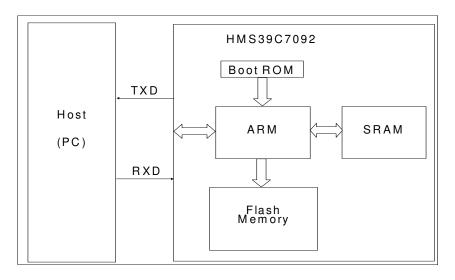

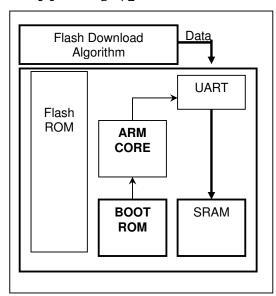

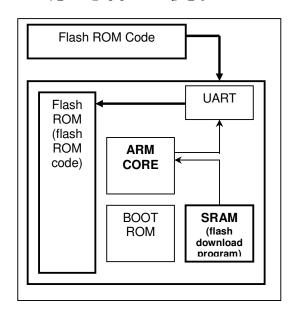

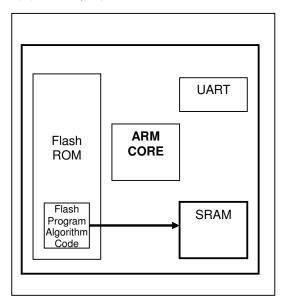

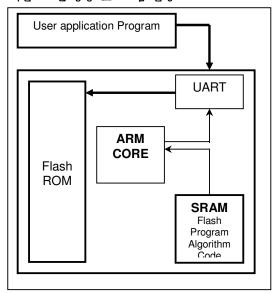

|    |      | On-Board 부트 모드에서의 시스템 구성 |     |

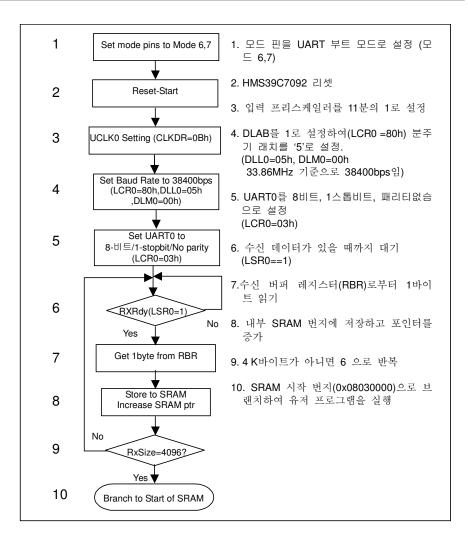

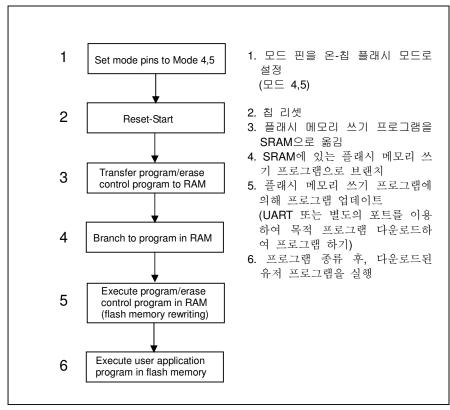

| 그림 | 12.3 | 부트 모드 실행 순서              |     |

|    | 12.4 | 11 1 - 20 12             |     |

| 그림 | 13.1 | A/D 컨버터의 블럭도             |     |

|    | 13.2 |                          |     |

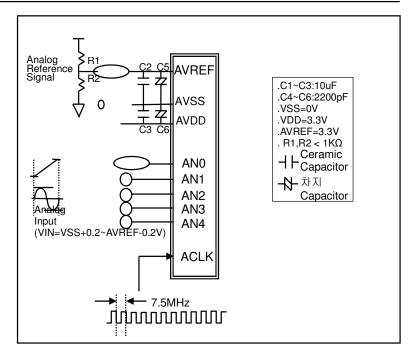

| _  | 13.3 | 아날로그 입력 회로의 예제           |     |

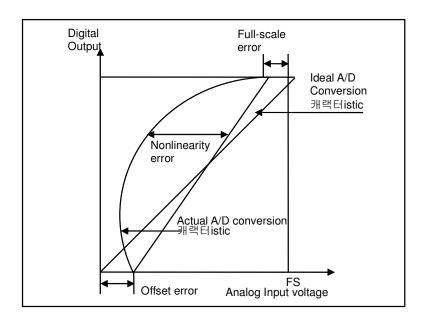

|    | 13.4 | A/D 컨버터 정확도 정의 (1)       |     |

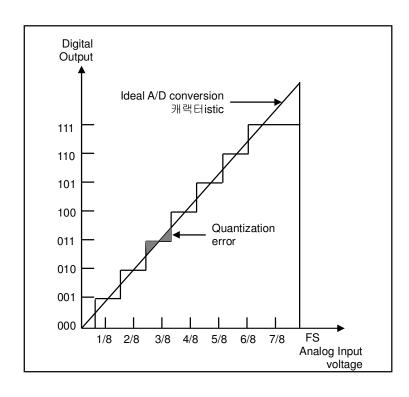

| _  | 13.5 | A/D 컨버터 정확도 정의 (2)       |     |

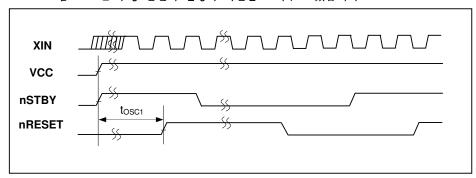

| 그림 |      | 수정 발진의 안정화 시간            |     |

| _  | 14.2 | 12. 4 1 1 0              |     |

| _  | 14.3 | 버스 컨트롤러의 쓰기 타이밍도         |     |

| _  | 14.4 | 버스 컨트롤러의 읽기 타이밍도         |     |

| _  | 14.5 | 외부 웨이트 입력에 의한 기본 버스 사이클  |     |

| 그림 | 14.6 | 버스 릴리스 모드 타이밍            | 183 |

# 표 목 차

|   |      | 핀 설명                                    |     |

|---|------|-----------------------------------------|-----|

| 丑 | 1.1  | 핀 설명 (계속)                               | 17  |

| 丑 | 1.1  | 핀 설명 (계속)                               | 18  |

| 丑 | 1.1  | 핀 설명 (계속)                               | 19  |

| 丑 |      | 핀 설명 (계속)                               |     |

|   | 1.2  | HMS39C7092 동작 모드                        | 21  |

| 丑 | 1.3  | 모드별 핀 할당                                |     |

| 丑 | 1.3  | 모드별 핀 할당 (계속)                           |     |

| 丑 | 1.3  | 모드별 핀 할당 (계속)                           |     |

| 丑 | 2.1  | ARM 명령어 셋 일람                            |     |

| 丑 | 2.2  | THUMB 명령어 셋 일람                          |     |

| 丑 | 2.3  | 컨디션 코드 요약                               | 38  |

| 丑 | 2.4  | PSR 모드 비트 값                             |     |

| 丑 | 3.1  | 버스 컨트롤러의 입·출력 핀                         | 45  |

| 丑 | 3.2  | 버스 컨트롤러의 레지스터 메모리 맵                     | 46  |

| 丑 | 3.3  | A0 에 따른 nHWR, nLWR 상태 (16 비트 버스 설정의 경우) | 51  |

| 丑 | 4.1  | 다기능 핀에 대한 설명                            |     |

| 丑 | 4.2  | MCU 컨트롤러 블록의 메모리 맵                      | 61  |

|   | 4.3  | 모드에 따른 MCU 컨트롤러 블록의 레지스터 초기값            | 61  |

| 丑 | 5.1  | PMU 부의 레지스터 맵                           | 71  |

| 丑 | 6.1  | 기본 우선순위                                 | 79  |

| 丑 | 6.2  | 메모리 맵                                   | 81  |

| 丑 | 6.3  | 인터럽트 소스 트리거 모드                          | 82  |

| 丑 | 7.1  | 와치독 타이머의 메모리 맵                          | 90  |

| 丑 | 7.2  | 카운터 클럭 소스에 따른 주기                        |     |

| 丑 | 8.1  | 타이머 블록 레지스터 맵                           | 102 |

| 丑 | 8.2  | 채널 별 레지스터 맵                             |     |

| 丑 | 8.3  | 각 채널의 기준 어드레스                           | 102 |

| 丑 | 9.1  | 신호 설명                                   |     |

| 丑 | 9.2  | UART 레지스터의 종류와 주소                       | 123 |

| 丑 | 9.3  | UART 레지스터의 초기화 값                        |     |

|   | 9.4a | , , , , , , , , , , , , , , , , , , , , |     |

| 丑 | 9.4b | 각 보레이트에 따른 분주값 (CLK=50MHz)              |     |

| 丑 | 9.5  | 인터럽트와 각각의 인터럽트 제어 방법                    |     |

| 丑 | 9.6  | UART 레지스터들의 요약                          |     |

| 丑 | 10.1 |                                         |     |

| 丑 | 12.1 | 9 ,                                     |     |

| 丑 | 12.2 |                                         | 149 |

|   | 12.3 |                                         | 150 |

|   | 12.4 | . 제어 레지스터                               | 152 |

| 丑 | 12.5 | 소거 섹터 레지스터                              | 153 |

| 丑 | 12.6 | 상태 및 전압 설정 레지스터 |                                        | 154 |

|---|------|-----------------|----------------------------------------|-----|

| 표 | 13.1 | A/D 컨버터 핀       |                                        | 163 |

| 丑 | 13.2 | A/D 컨버터의 레지스터들  |                                        | 164 |

| 丑 | 14.1 | 절대 한계치          |                                        | 176 |

| 丑 | 14.2 | 권장 동작 조건        |                                        | 176 |

|   |      |                 |                                        |     |

| 丑 | 14.4 | 풀업 핀의 특성        |                                        | 177 |

| 莊 | 14.5 | 풀다운 핀의 특성       |                                        | 177 |

|   |      |                 |                                        |     |

| 莊 | 14.7 | 컨트롤 신호 타이밍      |                                        | 178 |

|   |      |                 | (units: ns)                            |     |

|   |      |                 | ······································ |     |

|   |      |                 |                                        |     |

제1장 **소개**

#### 1.1 개요

본 제품은 매그나칩의 플래시메모리 내장형 고성능 32 비트 마이크로컨트롤러 제품군의 하나입니다. 이 제품군은 다양한 주변장치를 내장하고 있습니다. 이 마이크로컨트롤러는 192K 바이트 플리시메모리, 4K 바이트 SRAM, 16 비트 타이머 6 채널, 와치독 타이머, UART 2 채널, 프로그래머블 인터럽트 컨트롤러, 75 비트 GPIO포트, 칩셀렉트 및 웨이트 제어 가능한 버스 컨트롤러 등이 온칩 모듈라 아키텍쳐 (AMBA)로 내장 되어 있습니다.

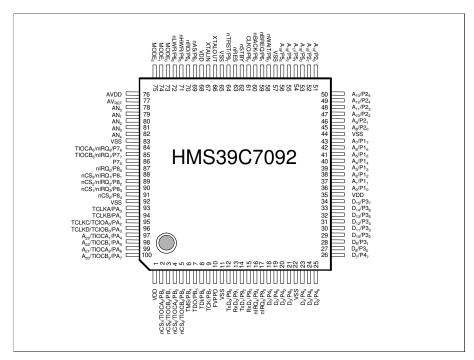

그림 1.1 핀 배치

#### 1.2 특징

- AMBA 를 이용한 단일 칩 모듈라 아키텍쳐

- ARM7TDMI 32 비트 RISC CPU

- 최고 50MHz 동작

- 192K 바이트(1.5Mb) 내장 플래시 메모리

- 4K 바이트 내장 SRAM (32 비트 0 웨이트)

- 8/16-비트 외부 어드레스/데이터 버스 지원

- 외부 8개의 칩셀렉트와 프로그래머블 또는 외부 웨이트 입력

- 전원 관리 유닛을 통한 저전력 설계

- 프로그래머블한 외부 8 입력 인터럽트 컨트롤러

- 다기능 타이머 6 채널 (업카운터/PWM)

- 8 비트 와치독 타이머(WDT)

- 16C550 호환 비동기 직렬 통신 인터페이스(UART) 2 채널

- 프로그래머블한 11 개의 범용 I/O 포트 (75 비트)

- 10 비트 5 채널 A/D 컨버터

- 100 TQFP 패키지

그림 1.2 HMS39C7092 블록도

### 1.3 핀 구성

### 표 1.1 핀 설명

|           | .1 번 설명            | HL#L | MM                                     |

|-----------|--------------------|------|----------------------------------------|

| <u> 핀</u> | 기호                 | 방향   | 설명                                     |

| 1         | VDD                | -    | 전원 (3.3V)                              |

|           | nCS <sub>7</sub>   | 0    | 외부 칩셀렉트 7                              |

| 2         | TCIOA <sub>3</sub> | I/O  | 타이머 3 PWM 출력, 컴페어 매치 GRA 출력 및 신호 캡쳐 입력 |

|           | PB₀                | I/O  | 범용 I/O 포트 B 비트0                        |

|           | nCS <sub>6</sub>   | 0    | 외부 칩셀렉트 6                              |

| 3         | TCIOB <sub>3</sub> | 1/0  | 타이머 3 PWM 출력, 컴페어 매치 GRB 출력 및 신호 캡쳐 입력 |

|           | PB <sub>1</sub>    | I/O  | 범용 I/O 포트 B 비트 1                       |

|           | nCS <sub>5</sub>   | 0    | 외부 칩셀렉트 5<br>                          |

| 4         | TIOCA <sub>4</sub> | I/O  | 타이머 4 PWM 출력, 컴페어 매치 GRA 출력 및 신호 캡쳐 입력 |

|           | PB <sub>2</sub>    | I/O  | 범용 I/O 포트 B 비트2                        |

|           | nCS <sub>4</sub>   | 0    | 외부 칩셀렉트 4                              |

| 5         | TIOCB <sub>4</sub> | I/O  | 타이머 4 PWM 출력, 컴페어 매치 GRB 출력 및 신호 캡쳐 입력 |

|           | PB <sub>3</sub>    | I/O  | 범용 I/O 포트 B 비트3                        |

| 6         | TMS                | l    | JTAG 테스트 모드 셀렉션                        |

|           | PB <sub>4</sub>    | I/O  | 범용 I/O 포트 B 비트4                        |

| 7         | TDO                | 0    | JTAG 테스트 데이터 출력                        |

|           | PB <sub>5</sub>    | I/O  | 범용 VO 포트 B 비트5                         |

| 8         | TDI                | 1    | JTAG 테스트 데이터 입력                        |

|           | PB <sub>6</sub>    | I/O  | 범용 I/O 포트 B 비트6                        |

| 9         | TCK                | ı    | JTAG 테스트 클럭                            |

|           | PB <sub>7</sub>    | I/O  | 범용 I/O 포트 B 비트7                        |

| 10        | VPPD               | ļ    | 플래시 프로그램 전원 (5V - 프로그램/프리프로그램 및 소거 시)  |

| 11        | VSS                | -    | 전원 (GND)                               |

| 12        | TxD <sub>0</sub>   | 0    | UARTO 송신 데이터                           |

|           | P9₀                | I/O  | 범용 I/O 포트 9 비트 0                       |

| 13        | RxD₀               | 0    | UARTO 수신 데이터                           |

|           | P9 <sub>1</sub>    | I/O  | 범용 I/O 포트 9 비트 1                       |

| 14        | TxD <sub>1</sub>   | 0    | UART1 송신 데이터                           |

|           | P9 <sub>2</sub>    | I/O  | 범용 I/O 포트 9 비트 2                       |

| 15        | RxD <sub>1</sub>   | 0    | UART1 수신 데이터<br>                       |

|           | P9 <sub>3</sub>    | I/O  | 범용 I/O 포트 9 비트 3                       |

| 16        | nIRQ <sub>4</sub>  | I    | 외부 인터럽트 입력 4                           |

|           | P9 <sub>4</sub>    | I/O  | 범용 I/O 포트 9 비트 4                       |

| 17        | nIRQ <sub>5</sub>  | l I  | 외부 인터럽트 입력 5                           |

|           | P9 <sub>5</sub>    | I/O  | 범용 I/O 포트 9 비트 5                       |

| 18        | D₀                 | I/O  | 외부 데이터 버스 비트 0                         |

|           | P4 <sub>0</sub>    | I/O  | 범용 I/O 포트 4 비트 0                       |

| 19        | D <sub>1</sub>     | 1/0  | 외부 데이터 버스 비트 1                         |

|           | P4 <sub>1</sub>    | I/O  | 범용 I/O 포트 4 비트 1                       |

| 20        | D <sub>2</sub>     | I/O  | 외부 데이터 버스 비트 2                         |

|           | P4 <sub>2</sub>    | I/O  | 범용 I/O 포트 4 비트 2                       |

| 21 -      | D <sub>3</sub>     | I/O  | 외부 데이터 버스 비트 3                         |

|           | P4 <sub>3</sub>    | I/O  | 범용 I/O 포트 4 비트 3                       |

표 1.1 핀 설명 (계속)

| 丑 1.1          | 핀 설명 (          | 계속) |                      |

|----------------|-----------------|-----|----------------------|

| 핀              | 기호              | 방향  | 설명                   |

| 22             | VSS             | -   | 전원 (GND)             |

| 22             | $D_4$           | I/O | 외부 데이터 버스 비트 4       |

| 23 —           | P4 <sub>4</sub> | I/O | 범용 NO 포트 4 비트 4      |

| 24 —           | D <sub>5</sub>  | I/O | 외부 데이터 버스 비트 5       |

| 24 —           | P4 <sub>5</sub> | I/O | -<br>범용 NO 포트 4 비트 5 |

| 25 —           | D <sub>6</sub>  | I/O | 외부 데이터 버스 비트 6       |

| 25             | P4 <sub>6</sub> | I/O | 범용 NO 포트 4 비트 6      |

| 26 —           | $D_7$           | I/O | 외부 데이터 버스 비트 7       |

| 20             | P4 <sub>7</sub> | I/O | -<br>범용 NO 포트 4 비트 7 |

| 27 —           | D <sub>8</sub>  | I/O | 외부 데이터 버스 비트 8       |

| 21             | P3 <sub>0</sub> | I/O | 범용 NO 포트 3 비트 0      |

| 20             | $D_9$           | I/O | 외부 데이터 버스 비트 9       |

| 28 —           | P3 <sub>1</sub> | I/O | -<br>범용 NO 포트 3 비트 1 |

| 20             | D <sub>10</sub> | I/O | 외부 데이터 버스 비트 10      |

| 29 —           | P3 <sub>2</sub> | I/O | 범용 NO 포트 3 비트 2      |

| 20             | D <sub>11</sub> | I/O | 외부 데이터 버스 비트 11      |

| 30 —           | P3 <sub>3</sub> | I/O | 범용 NO 포트 3 비트 3      |

| 21             | D <sub>12</sub> | I/O | 외부 데이터 버스 비트 12      |

| 31 —           | P3 <sub>4</sub> | I/O | 범용 NO 포트 3 비트 4      |

| 32 —           | D <sub>13</sub> | I/O | 외부 데이터 버스 비트 13      |

| 32 —           | P3 <sub>5</sub> | I/O | -<br>범용 NO 포트 3 비트 5 |

| 33 —           | D <sub>14</sub> | I/O | 외부 데이터 버스 비트 14      |

| 33             | P3 <sub>6</sub> | I/O | 범용 NO 포트 3 비트 6      |

| 34 —           | D <sub>15</sub> | I/O | 외부 데이터 버스 비트 15      |

| 34             | P3 <sub>7</sub> | I/O | 범용 NO 포트 3 비트 7      |

| 35             | VDD             | -   | 전원 (3.3V)            |

| 36 —           | $A_0$           | 0   | 외부 어드레스 버스 비트 0      |

| - 00           | $P1_0$          | I/O | 범용 I/O 포트 1 비트 0     |

| 37 —           | $A_1$           | 0   | 외부 어드레스 버스 비트 1      |

|                | P1 <sub>1</sub> | I/O | 범용 I/O 포트 1 비트 1     |

| 38 —           | $A_2$           | 0   | 외부 어드레스 버스 비트 2      |

| - 00           | P1 <sub>2</sub> | I/O | 범용 I/O 포트 1 비트 2     |

| 39 <del></del> | A <sub>3</sub>  | 0   | 외부 어드레스 버스 비트 3      |

|                | P1 <sub>3</sub> | I/O | 범용 I/O 포트 1 비트 3     |

| 40 —           | $A_4$           | 0   | 외부 어드레스 버스 비트 4      |

|                | P1 <sub>4</sub> | I/O | 범용 I/O 포트 1 비트 4     |

| 41 —           | A <sub>5</sub>  | 0   | 외부 어드레스 버스 비트 5      |

|                | P1 <sub>5</sub> | I/O | 범용 I/O 포트 1 비트 5     |

| 42 —           | $A_6$           | 0   | 외부 어드레스 버스 비트 6      |

|                | P1 <sub>6</sub> | I/O | 범용 NO 포트 1 비트 6      |

| 43 —           | $A_7$           | 0   | 외부 어드레스 버스 비트 7      |

| -10            | P1 <sub>7</sub> | I/O | 범용 I/O 포트 1 비트 7     |

| 44             | VSS             | -   | 전원 (GND)             |

| 45 —           | A <sub>8</sub>  | 0   | 외부 어드레스 버스 비트 8      |

|                | P2 <sub>0</sub> | I/O | 범용 NO 포트 2 비트 0      |

|                |                 |     |                      |

| 丑 1. | .1 핀 설명 (기            | 계속)      |                                      |

|------|-----------------------|----------|--------------------------------------|

| 핀    | 기호                    | 방향       | 설명                                   |

| 46   | <b>A</b> <sub>9</sub> | 0        | 외부 어드레스 버스 비트 9                      |

| 46   | P2 <sub>1</sub>       | I/O      | 범용 NO 포트 2 비트 1                      |

| 47   | A <sub>10</sub>       | 0        | 외부 어드레스 버스 비트 10                     |

| 47   | P2 <sub>2</sub>       | I/O      | 범용 NO 포트 2 비트 2                      |

| 48   | A <sub>11</sub>       | 0        | 외부 어드레스 버스 비트 11                     |

| 40   | P2 <sub>3</sub>       | I/O      | 범용 NO 포트 2 비트 3                      |

| 49   | A <sub>12</sub>       | 0        | 외부 어드레스 버스 비트 12                     |

|      | P2 <sub>4</sub>       | I/O      | 범용 NO 포트 2 비트 4                      |

| 50   | A <sub>13</sub>       | 0        | 외부 어드레스 버스 비트 13<br>-                |

|      | P2 <sub>5</sub>       | I/O      | 범용 NO 포트 2 비트 5                      |

| 51   | A <sub>14</sub>       | 0        | 외부 어드레스 버스 비트 14<br>-                |

|      | P2 <sub>6</sub>       | I/O      | 범용 I/O 포트 2 비트 6                     |

| 52   | A <sub>15</sub>       | 0        | 외부 어드레스 버스 비트 15<br>                 |

|      | P2 <sub>7</sub>       | 1/0      | 범용 VO 포트 2 비트 7                      |

| 53   | A <sub>16</sub>       | 0        | 의부 어드레스 버스 비트 16<br>-                |

|      | P5 <sub>0</sub>       | 1/0      | 범용 VO 포트 5 비트 0                      |

| 54   | P5 <sub>1</sub>       | 0<br>I/O | 의부 어드레스 버스 비트 17<br>- 범용 NO 표트 대비트 1 |

|      |                       | I/O      | 범용 VO 포트 5 비트 1<br>외부 어드레스 버스 비트 18  |

| 55   | P5 <sub>2</sub>       | I/O      | -                                    |

|      | A <sub>19</sub>       | 0        | 외부 어드레스 버스 비트 19                     |

| 56   | P5 <sub>3</sub>       | 1/0      | -<br>범용 VO 포트 5 비트 3                 |

| 57   | VSS                   | -        | 전원 (GND)                             |

|      | nWAIT                 | ı        | 외부 버스 웨이트 입력                         |

| 58   | P6 <sub>0</sub>       | I/O      | - '                                  |

|      | nBREQ                 | ı        | 외부 버스 Request                        |

| 59   | P6 <sub>1</sub>       | I/O      | 범용 I/O 포트 6 비트 1                     |

|      | nBACK                 | ı        | 외부 버스 애크놀로지                          |

| 60   | P6 <sub>2</sub>       | I/O      | 범용 I/O 포트 6 비트 2                     |

|      | CLKO                  | 0        | 버스 클럭 출력                             |

| 61   | P6 <sub>7</sub>       | I/O      | -<br>범용 NO 포트 6 비트 7                 |

| 62   | nSTBY                 | 0        | 스탠바이 모드 신호. 파워 다운 모드 인디케이터           |

| 63   | nRESET                |          | 외부 리셋                                |

| 64   | nTRST                 | I        | JTAG 테스트 리셋 입력 (pull-down)           |

| 04   | P9 <sub>7</sub>       | I/O      | 범용 I/O 포트 9 비트 7 (pull-down)         |

| 65   | VSS                   | -        | 전원 (GND)                             |

| 66   | XTALOUT               | 0        | 수정 발진자 궤환 출력                         |

| 67   | XTALIN                | I        | 수정 발진자 또는 외부 오실레이터 입력                |

| 68   | VDD                   | -        | 전원 (3.3V)                            |

| 69   | nAS                   | 0        | 의부 어드레스 버스 스트로브<br>-                 |

|      | P6 <sub>3</sub>       | I/O      | 범용 NO 포트 6 비트 3                      |

| 70   | nRD                   | 0        | 외부 버스 읽기                             |

|      | P6 <sub>4</sub>       | I/O      | 범용 I/O 포트 6 비트 4                     |

| 71   | nHWR                  | 0        | 외부 상위 8 비트 데이터 버스 쓰기<br>             |

|      | P6 <sub>5</sub>       | I/O      | 범용 VO 포트 6 비트 5<br>                  |

| 핀            | 기호                 | 방향         | 설명                                                                |

|--------------|--------------------|------------|-------------------------------------------------------------------|

| 70           | nLWR               | 0          | 외부 하위 8 비트 데이터 버스 쓰기                                              |

| 72 –         | P6 <sub>6</sub>    | I/O        | -<br>범용 I/O 포트 6 비트 6                                             |

| 73           | MODE₀              | I          | 모드 비트 0                                                           |

| 74           | MODE <sub>1</sub>  | I          | 모드 비트 1                                                           |

| 75           | MODE <sub>2</sub>  | I          | 모드 비트 2                                                           |

| 76           | AVDD               | -          | 아나로그 전원 (3.3V)                                                    |

| 77           | AVREF              | -          | ADC 기준 전압                                                         |

| 78           | $AN_0$             | I          | ADC 입력 채널 0                                                       |

| 79           | AN <sub>1</sub>    | 1          | ADC 입력 채널 1                                                       |

| 80           | AN <sub>2</sub>    | I          | ADC 입력 채널 2                                                       |

| 81           | AN <sub>3</sub>    | 1          | ADC 입력 채널 3                                                       |

| 82           | AN <sub>4</sub>    | 1          | ADC 입력 채널 4                                                       |

| 83           | VSS                | -          | 전원 (GND, 내부적으로 AVSS와 공통)                                          |

|              | TIOCA <sub>5</sub> | I/O        | 타이머 5 PWM 출력, 컴페어 매치 GRA 출력 및 신호 캡쳐 입력                            |

| 84           | nIRQ <sub>6</sub>  | 1          | -<br>외부 인터럽트 입력 6                                                 |

| _            | P7 <sub>6</sub>    | I/O        | -<br>범용 I/O 포트 7 비트 6                                             |

|              | TIOCB <sub>5</sub> | I/O        | 타이머 5 PWM 출력, 컴페어 매치 GRB 출력 및 신호 캡쳐 입력                            |

| 85           | nIRQ <sub>7</sub>  | I          | -<br>외부 인터럽트 입력 7                                                 |

|              | P7 <sub>7</sub>    | I/O        | 범용 I/O 포트 7 비트 7                                                  |

| 86           | P7 <sub>5</sub>    | I/O        | 범용 NO 포트 7 비트 5                                                   |

| 87 —         | nIRQ₀              | 1          | 외부 인터럽트 입력 0                                                      |

| 07           | P8 <sub>0</sub>    | I/O        | 범용 NO 포트 8 비트 0                                                   |

| _            | nCS <sub>3</sub>   | 0          | 외부 칩셀렉트 3                                                         |

| 88           | nIRQ <sub>1</sub>  | I          | 외부 인터럽트 입력 1                                                      |

|              | P8 <sub>1</sub>    | I/O        | 범용 I/O 포트 8 비트 1                                                  |

| _            | nCS <sub>2</sub>   | 0          | 외부 칩셀렉트 2                                                         |

| 89           | nIRQ <sub>2</sub>  | I          | 외부 인터럽트 2                                                         |

|              | P8 <sub>2</sub>    | I/O        | 범용 I/O 포트 8 비트 2                                                  |

| _            | nCS <sub>1</sub>   | 0          | 외부 칩셀렉트 1<br>-                                                    |

| 90           | nIRQ₃              | ı          | 외부 인터럽트 3<br>-                                                    |

|              | P8 <sub>3</sub>    | I/O        | 범용 NO 포트 8 비트 3                                                   |

| 91 —         | nCS₀               | 0          | 외부 칩셀렉트 0                                                         |

|              | P8 <sub>4</sub>    | I/O        | 범용 I/O 포트 8 비트 4                                                  |

| 92           | VSS                | -          | 전원 (GND)                                                          |

| 93 —         | TCLKA              | I          | 외부 타이머 클럭 입력 A                                                    |

|              | PA <sub>0</sub>    | I/O        | 범용 I/O 포트 A 비트 0                                                  |

| 94 —         | TCLKB              | I          | 외부 타이머 클럭 입력 B                                                    |

|              | PA <sub>1</sub>    | 1/0        | 범용 I/O 포트 A 비트 1                                                  |

| 05           | TIOCA <sub>0</sub> | 1/0        | 외부 타이머 클릭 입력 C<br>-<br>- 타이머 O DMAN 초려 컨펜어 메쉬 CDA 초려 미 시호 캐쉬 이려   |

| 95           | PA <sub>2</sub>    | I/O        | 타이머 0 PWM 출력, 컴페어 매치 GRA 출력 및 신호 캡쳐 입력<br>-<br>- 버용 NO 파트 A NE 2  |

|              |                    | 1/O<br>I   | 범용 I/O 포트 A 비트 2<br>외부 타이머 클럭 입력 D                                |

| 96           | TCLKD<br>TIOCB₀    |            |                                                                   |

| <del>-</del> |                    | I/O<br>I/O | 타이머 0 PWM 출력, 컴페어 매치 GRB 출력 및 신호 캡쳐 입력<br>-<br>- 버용 NO 파트 A HLE 2 |

|              | PA <sub>3</sub>    | I/U        | 범용 NO 포트 A 비트 3                                                   |

표 1.1 핀 설명 (계속)

| 11. 11 | 1 TO 28 (/         | <i>""   "   "   "   "   "   "   "   "   " </i> |                                             |

|--------|--------------------|------------------------------------------------|---------------------------------------------|

| 핀      | 기호                 | 방향                                             | 설명                                          |

|        | A <sub>23</sub>    | 0                                              | 외부 어드레스 버스 비트 23                            |

| 97     | TIOCA <sub>1</sub> | I/O                                            | -<br>타이머 1 PWM 출력, 컴페어 매치 GRA 출력 및 신호 캡쳐 입력 |

| •      | PA <sub>4</sub>    | I/O                                            | -<br>범용 NO 포트 A 비트 4                        |

|        | A <sub>22</sub>    | 0                                              | 외부 어드레스 버스 비트 22                            |

| 98     | TIOCB <sub>1</sub> | I/O                                            | -<br>타이머 1 PWM 출력, 컴페어 매치 GRB 출력 및 신호 캡쳐 입력 |

| •      | PA <sub>5</sub>    | I/O                                            | -<br>범용 NO 포트 A 비트 5                        |

|        | A <sub>21</sub>    | 0                                              | 외부 어드레스 버스 비트 21                            |

| 99     | TIOCA <sub>2</sub> | I/O                                            | 타이머 2 PWM 출력, 컴페어 매치 GRA 출력 및 신호 캡쳐 입력      |

| •      | PA <sub>6</sub>    | I/O                                            | -<br>범용 NO 포트 A 비트 6                        |

|        | A <sub>20</sub>    | 0                                              | 외부 어드레스 버스 비트 20                            |

| 100    | TIOCB <sub>2</sub> | I/O                                            | -<br>타이머 2 PWM 출력, 컴페어 매치 GRB 출력 및 신호 캡쳐 입력 |

| •      | PA <sub>7</sub>    | I/O                                            | -<br>범용 NO 포트 A 비트 7                        |

#### 1.4 동작 모드

HMS39C7092 는 플래시 메모리가 내장된 ARM MCU 입니다. 이 MCU 는  $extbf{ ilde H.2}$  에서와 같이 네 종류의 동작 모드를 갖고 있습니다. HMS39C7092 외부 핀 기능은 외부 모드 신호를 설정하거나 PIN MUX 레지스터의 값을 재구성함으로써 변경되어 집니다. 모드에 의한 핀 할당이  $extbf{ ilde H.3.0}$ 에 나타나 있습니다. 모드를 변경에따라 메모리의 구성이 바뀌어 집니다. 그림 1.3 은 디폴트 메모리 맵을 보여 주며,각 모드별 메모리 맵은 그림 1.4, 그림 1.5 그리고 그림 1.6.에서 보여 줍니다. 동작 모드 정의는 다음과 같습니다.

표 1.2 HMS39C7092 동작 모드

| 모드  | 모드 설명                        |

|-----|------------------------------|

| 0,1 | 테스트용 예약                      |

| 2   | PROM 모드                      |

| 2   | 외부 8 비트 데이터버스 (16M 바이트 영역)   |

| 3   | 외부 16 비트 데이터버스 (16M 바이트 영역)  |

| 4   | 플래시 부트 모드 (외부 16 비트 데이터 버스)  |

| 5   | 플래시 부트 모드 (싱글칩 모드)           |

| 6   | UART 부트 모드 (외부 16 비트 데이터 버스) |

| 7   | UART 부트 모드 (싱글칩 모드)          |

표 1.3 모드별 핀 할당

| 班 1.3    | 모드별 핀 할  | な            |              |              |              |              |

|----------|----------|--------------|--------------|--------------|--------------|--------------|

| 핀        | 모드 2     | 모드 3         | 모드 4         | 모드 6         | 모드 5         | 모드 7         |

| 번호       | 외부       | 외부           | 플래시부트 모드     | UART 부트 모드   | 플래시부트 모드     | UART 부트 모드   |

|          | 8 비트 버스  | 16 비트 버스     | 16 비트 버스     | 16 비트 버스     | (싱글칩 모드)     | (싱글침 모드)     |

| 1        | VDD      | +            | +            | +            | <del>+</del> | <del>+</del> |

| 2        | nCS7     | <b>+</b>     | +            | <b>←</b>     | TIOCA3       | <del>+</del> |

| 3        | nCS6     | <b>←</b>     | <b>←</b>     | <del>-</del> | TIOCB3       | +            |

| 4        | nCS5     | +            | +            | <b>←</b>     | TIOCA4       | +            |

| 5        | nCS4     | <b>←</b>     | <b>←</b>     | <b>←</b>     | TIOCB4       | +            |

| 6        | TMS      | <b>←</b>     | <b>←</b>     | <b>←</b>     | <b>←</b>     | <del>-</del> |

| 7        | TDO      | <b>←</b>     | <b>←</b>     | <b>←</b>     | <b>←</b>     | +            |

| 8        | TDI      | <b>←</b>     | <b>←</b>     | <b>←</b>     | <b>←</b>     | +            |

| 9        | TCK      | <b>←</b>     | <b>←</b>     | <del>-</del> | +            | +            |

| 10       | TVPPD    | +            | +            | +            | +            | +            |

| 11       | VSS      | <b>←</b>     | +            | +            | <b>←</b>     | <b>←</b>     |

| 12       | TxD0     | <b>←</b>     | <b>←</b>     | <del>-</del> | <b>←</b>     | +            |

| 13       | RxD0     | +            | +            | <del>-</del> | +            | +            |

| 14       | TxD1     | +            | +            | <del>-</del> | +            | +            |

| 15       | RxD1     | <b>←</b>     | +            | <b>←</b>     | <b>←</b>     | +            |

| 16       | nIRQ4    | <b>←</b>     | <b>←</b>     | +            | +            | +            |

| 17       | nIRQ5    | <b>←</b>     | <b>←</b>     | +            | +            | +            |

| 18       | D0       | +            | +            | <b>←</b>     | P40          | +            |

| 19       | D1       | +            | +            | <b>←</b>     | P41          | +            |

| 20       | D2       | <b>←</b>     | <b>←</b>     | <b>←</b>     | P42          | <b>←</b>     |

| 21       | D3       | +            | +            | <b>←</b>     | P43          | +            |

| 22       | VSS      | +            | +            | <b>←</b>     | +            | +            |

| 23       | D4       | +            | +            | <b>←</b>     | P44          | +            |

| 24       | D5       | +            | +            | <b>←</b>     | P45          | +            |

| 25       | D6       | <b>←</b>     | +            | <del>-</del> | P46          | +            |

| 26       | D7       | +            | +            | <del>-</del> | P47          | <del>+</del> |

| 27       | P30      | D8           | +            | <del>-</del> | P30          | <del>+</del> |

| 28       | P31      | D9           | <del>+</del> | +            | P31          | <del>+</del> |

| 29       | P32      | D10          | <del>+</del> | +            | P32          | <del></del>  |

| 30       | P33      | D11          | <del></del>  | <del></del>  | P33          | <del></del>  |

| 31       | P34      | D12          | <del>+</del> | <del>+</del> | P34          | <del></del>  |

| 32       | P35      | D13          | <del></del>  | <del>+</del> | P35          | <del></del>  |

| 33       | P36      | D14          | <del></del>  | <del>+</del> | P36          | <del></del>  |

| 34       | P37      | D15          | <del>-</del> | <del>+</del> | P37          | <del></del>  |

| 35       | VDD      | <b>←</b>     | <u>←</u>     | <u>←</u>     | ←<br>P10     | <u>←</u>     |

| 36       | A0       | <del>+</del> | <del></del>  | <del></del>  |              | <del></del>  |

| 37<br>38 | A1       | <u></u> ←    | <del></del>  | <del></del>  | P11          | <del></del>  |

| 38       | A2<br>A3 | <del>+</del> | <del>+</del> | <del></del>  | P12<br>P13   | <del></del>  |

| 40       | A3<br>A4 | <del>+</del> | <del></del>  | <del></del>  | P13          | <del></del>  |

| 40       | A4       | Ψ            | <b>~</b>     | 7            | P14          |              |

표 1.3 모드별 핀 할당 (계속)

| 班 1.3 | 모드별 핀 할    | せ (계곡)       |              |              |              |              |

|-------|------------|--------------|--------------|--------------|--------------|--------------|

| 핀     | 모드 2       | 모드 3         | 모드 4         | 모드 6         | 모드 5         | 모드 7         |

| 번호    | 외부         | 외부           | 플래시부트 모드     | UART 부트 모드   | 플래시부트 모드     | UART 부트 모드   |

|       | 8 비트 버스    | 16 비트 버스     | 16 비트 버스     | 16 비트 버스     | (싱글칩 모드)     | (싱글칩 모드)     |

| 41    | A5         | +            | +            | +            | P15          | <del>+</del> |

| 42    | A6         | <del>-</del> | <del>-</del> | <del>-</del> | P16          | <del>-</del> |

| 43    | A7         | <b>←</b>     | <b>←</b>     | <b>←</b>     | P17          | <del>-</del> |

| 44    | VSS        | <del>(</del> | <del>(</del> | <del>-</del> | +            | <del>-</del> |

| 45    | A8         | +            | +            | +            | P20          | +            |

| 46    | A9         | +            | +            | <b>←</b>     | P21          | +            |

| 47    | A10        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P22          | +            |

| 48    | A11        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P23          | +            |

| 49    | A12        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P24          | <del>-</del> |

| 50    | A13        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P25          | +            |

| 51    | A14        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P26          | <b>←</b>     |

| 52    | A15        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P27          | <b>←</b>     |

| 53    | A16        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P50          | <b>←</b>     |

| 54    | A17        | <b>←</b>     | <b>←</b>     | <b>←</b>     | P51          | <del>-</del> |

| 55    | A18        | <del>-</del> | <del>-</del> | <del>-</del> | P52          | +            |

| 56    | A19        | +            | +            | <b>←</b>     | P53          | +            |

| 57    | VSS        | +            | +            | <b>←</b>     | <b>←</b>     | +            |

| 58    | nWAIT      | +            | +            | +            | P60          | +            |

| 59    | nBREQ      | +            | +            | +            | P61          | +            |

| 60    | nBACK      | <b>←</b>     | +            | <b>←</b>     | P62          | <b>←</b>     |

| 61    | CLKO       | <b>←</b>     | <b>←</b>     | +            | P67          | +            |

| 62    | nSTBY      | +            | +            | <b>←</b>     | nSTBY        | +            |

| 63    | nRES       | +            | +            | +            | nRES         | +            |

| 64    | nTRST      | <b>←</b>     | +            | <b>←</b>     | nTRST        | +            |

| 65    | VSS        | <b>←</b>     | +            | <b>←</b>     | <b>←</b>     | +            |

| 66    | XTALOUT    | +            | +            | <del>-</del> | <del>-</del> | <u>+</u>     |

| 67    | XTALIN     | +            | +            | <del>-</del> | <del>-</del> | <u>+</u>     |

| 68    | VDD        | +            | +            | +            | <b>←</b>     | <u>+</u>     |

| 69    | nAS        | +            | <del>-</del> | +            | P63          | <u>+</u>     |

| 70    | nRD        | <del></del>  | <u>+</u>     | <u>+</u>     | P64          | <u>+</u>     |

| 71    | nHWR       | <del>-</del> | <del>-</del> | <del>-</del> | P65          | <del>+</del> |

| 72    | nLWR       | <del>-</del> | <del>-</del> | <del>-</del> | P66          | <del>+</del> |

| 73    | MODE0      | <del>-</del> | <del>-</del> | <del>-</del> | <del>+</del> | <del>+</del> |

| 73    | MODE1      | <del>-</del> | <del>-</del> | +            | <del>+</del> | <del></del>  |

| 75    | MODE2      | <del>-</del> | <del>+</del> | +            | <del>+</del> | <del></del>  |

| 76    | AVDD       | <del>-</del> | +            | +            | <del>+</del> | <del>+</del> |

| 77    | AVREF      | <del></del>  | <del></del>  | <del>+</del> | <del>+</del> | <del>+</del> |

| 78    | AN0        | <del>-</del> | <del>-</del> | <del>+</del> | <del>+</del> | <del>+</del> |

| 79    | AN1<br>AN2 | <del></del>  | <del>-</del> | <del></del>  | <del>+</del> | <u>←</u>     |

| 80    | AINZ       | +            | +            | +            | +            |              |

표 1.3 모드별 핀 할당 (계속)

| 並 1.3 | 모드별 편 말 | 경 ( <i>계숙</i> ) |              |              |          |              |

|-------|---------|-----------------|--------------|--------------|----------|--------------|

| 핀     | 모드 2    | 모드 3            | 모드 4         | 모드 6         | 모드 5     | 모드 7         |

| 번호    | 외부      | 외부              | 플래시부트 모드     | UART 부트 모드   | 플래시부트 모드 | UART 부트 모드   |

|       | 8 비트 버스 | 16 비트 버스        | 16 비트 버스     | 16 비트 버스     | (싱글칩 모드) | (싱글침 모드)     |

| 81    | AN3     | <b>←</b>        | <b>←</b>     | <b>←</b>     | <b>←</b> | <b>←</b>     |

| 82    | AN4     | <b>←</b>        | <b>←</b>     | <del>-</del> | <b>←</b> | +            |

| 83    | VSS     | <b>←</b>        | <b>←</b>     | <del>-</del> | <b>←</b> | +            |

| 84    | TIOCA5  | +               | +            | +            | +        | +            |

| 85    | TIOCB5  | <b>←</b>        | <del>-</del> | <del>-</del> | <b>←</b> | +            |

| 86    | P75     | +               | +            | +            | <b>←</b> | <del>-</del> |

| 87    | nIRQ0   | +               | +            | +            | <b>←</b> | <del>-</del> |

| 88    | nCS3    | <b>←</b>        | <del>-</del> | <del>-</del> | P81      | <b>←</b>     |

| 89    | nCS2    | +               | +            | +            | P82      | +            |

| 90    | nCS1    | +               | +            | +            | P83      | <del>-</del> |

| 91    | nCS0    | <b>←</b>        | <del>-</del> | <b>←</b>     | P84      | <b>←</b>     |

| 92    | VSS     | <b>←</b>        | <del>-</del> | <del>-</del> | <b>←</b> | <b>←</b>     |

| 93    | TCLKA   | <b>←</b>        | <del>-</del> | <del>-</del> | <b>←</b> | <b>←</b>     |

| 94    | TCLKB   | <b>←</b>        | <del>-</del> | <del>-</del> | <b>←</b> | <b>←</b>     |

| 95    | TCLKC   | <b>←</b>        | <del>-</del> | <del>-</del> | <b>←</b> | <b>←</b>     |

| 96    | TCLKD   | +               | +            | +            | +        | <del>-</del> |

| 97    | A23     | +               | <b>←</b>     | TIOCA1       | <b>←</b> | <del>-</del> |

| 98    | A22     | +               | +            | TIOCB1       | <b>←</b> | <del>-</del> |

| 99    | A21     | <b>←</b>        | <b>←</b>     | TIOCA2       | +        | +            |

| 100   | A20     | +               | +            | TIOCB2       | +        | +            |

#### 1.5 메모리 맵

그림 1.3 HMS39C7092 메모리 멤

그림 1.4 모드 2,3의 메모리 맵

그림 1.5 모드 4와 모드 5의 메모리 맵

|                             | 0x07FF FFFF |                                      | 0x07FF FFFF                |                                          | 0x07FF FFFF |                                       | 0x07FF FFFF                |

|-----------------------------|-------------|--------------------------------------|----------------------------|------------------------------------------|-------------|---------------------------------------|----------------------------|

| nCS7                        | 0x0700 0000 |                                      |                            | nCS7                                     | 0x0700 0000 |                                       |                            |

|                             | 0x06FF FFFF | Reserved                             |                            |                                          | 0x06FF FFFF | Reserved                              |                            |

| nCS6                        | 0x0600 0000 |                                      |                            | nCS6                                     | 0x0600 0000 |                                       |                            |

|                             | 0x05FF FFFF |                                      | 0x0080 0000                |                                          | 0x05FF FFFF |                                       | 0x0080 0000                |

| nCS5                        | 0x0500 0000 | nCS7                                 | 0x007F FFFF<br>0x0070 0000 | nCS5                                     | 0x0500 0000 | nCS7                                  | 0x007F FFFF<br>0x0070 0000 |

| nCS4                        | 0x04FF FFFF | nCS6                                 | 0x006F FFFF                | nCS4                                     | 0x04FF FFFF | nCS6                                  | 0x006F FFFF                |

| 11054                       | 0x0400 0000 | 11036                                | 0x0060 0000                | 11054                                    | 0x0400 0000 | 11036                                 | 0x0060 0000                |

| nCS3                        | 0x03FF FFFF | nCS5                                 | 0x005F FFFF<br>0x0050 0000 | nCS3                                     | 0x03FF FFFF | nCS5                                  | 0x005F FFFF<br>0x0050 0000 |

| 11033                       | 0x0300 0000 | nCS4                                 | 0x004F FFFF<br>0x0040 0000 | 11033                                    | 0x0300 0000 | nCS4                                  | 0x004F FFFF<br>0x0040 0000 |

|                             | 0x02FF FFFF |                                      |                            |                                          | 0x02FF FFFF |                                       |                            |

| nCS2                        | 0x0200 0000 | nCS3                                 | 0x003F FFFF<br>0x0030 0000 | nCS2                                     | 0x0200 0000 | nCS3                                  | 0x003F FFFF<br>0x0030 0000 |

| nCS1                        | 0x01FF FFFF | nCS2                                 | 0x002F FFFF<br>0x0020 0000 | nCS1                                     | 0x01FF FFFF | nCS2                                  | 0x002F FFFF<br>0x0020 0000 |

| 11031                       | 0x0100 0000 |                                      | 0x001F FFFF                | 11031                                    | 0x0100 0000 |                                       | 0x001F FFFF                |

|                             | 0x00FF FFFF | nCS1                                 | 0x0010 0000                |                                          | 0x00FF FFFF | nCS1                                  | 0x0010 0000                |

|                             |             |                                      | 0x000F FFFF                |                                          | 0x0003 0000 |                                       | 0x000F FFFF                |

| nCS0                        |             | nCS0                                 | 0x0000 0100                |                                          | 0x0002 FFFF |                                       | 0x0003 0000                |

|                             | 0x0000 0100 |                                      |                            | nCS0                                     | 0x0000 1000 | nCS0                                  | 0x0002 FFFF                |

| On Chip                     | 0x0000 00FF | On Chip                              | 0x0000 00FF                |                                          | 0x0000 0FFF |                                       | 0x0000 1000                |

| Boot ROM<br>(256Byte)       | 0x0000 0000 | Boot ROM<br>(256Byte)                | 0x0000 0000                |                                          | 0x0000 0000 |                                       | 0x0000 0FFF<br>0x0000 0000 |

| Default.<br>SM=0 in the PMU |             | =1 and OnFLASH=0<br>ne PMU register. | •                          | SM=0 and On FLAS<br>in the PMU register. | H=1         | SM=1 and OnFLAS<br>in the PMU registe |                            |

그림 1.6 모드 6의 메모리 맵

그림 1.6 모드 7의 메모리 맵

제2장

# ARM7TDMI 코어

#### 2.1 개요

ARM7TDMI 는 범용 32 비트 CPU 로, 저전력과 낮은 가격에 비해 고성능의 CPU 입니다. 이 CPU 는 THUMB 이라는 아키텍쳐를 채용하여 메모리가 제약되어 있거나 코드 길이가 한정된 응용에 적합합니다.

ARM7TDMI는 32 비트 표준 ARM 명령어 셋과 16 비트 THUMB 명령어 셋의 두 개의 명령어 셋을 가지고 있습니다. 이 THUMB 명령어 셋에 의한 코드 길이는 32 비트 표준 명령어 셋으로 구성된 코드 길이의 최대 1/2 이며, 전형적인 16 비트 레지스터를 사용하는 16 비트 프로세서에 비해 ARM 의 고성능을 그대로 보유하고 있는데, 이는 THUMB 코드가 ARM 코드로서 같은 32 비트 레지스터로 동작하기 때문입니다.

자세한 ARM7TDMI 에 대한 자세한 설명은 데이터 시트(ARM DDI 0029E)를 참조하십시오.

#### 2.2 특징

- 32 비트 RISC 아키텍쳐

- 저전력 소모

- ARM7TDMI 및 주변 블록;

- On-chip ICEbreaker 디버그 지원

- 32 비트 x 8 하드웨어 승산기

- Thumb 명령어 디코더

- ARM7TDMI 임베디드 프로세서 사용

- 고성능 32 비트 RISC 아키텍쳐

- 고밀도 16 비트 명령어 셋 (THUMB 코드)

- 안정적인 동작: 0 ~ 50MHz

- 3 단계 파이프라인 아키텍쳐 (Fetch, decode, and execution stage)

- 향상된 ARM 소프트웨어 개발 환경

THUMB 코드는 ARM 코드에 비해 약 35% 정도의 절약 효과가 있으며, 외부에 16 비트 메모리 구성 시 약 60% 정도의 성능 향상이 있습니다.

#### 2.3 코어 블럭도

그림 2.1 ARM7TDMI 코어 블록도

### 2.4 명령어 셋

### 2.4.1 ARM 명령어

| Cond                              | 0 | 0 | I | С | )pc | 000      | de | s | Rn      | Rd                       |    | Operand |    |     |    |     | ar | nd     |                                        | Data Processing / PSR Transfer          |

|-----------------------------------|---|---|---|---|-----|----------|----|---|---------|--------------------------|----|---------|----|-----|----|-----|----|--------|----------------------------------------|-----------------------------------------|

| Cond                              | 0 | 0 | 0 | 0 | 0   | 0        | Α  | s | Rd      | Rn                       |    | R       | s  |     | 1  | 0   | 0  | 1      | Rm                                     | Multiply                                |

| Cond                              | 0 | 0 | 0 | 0 | 1   | U        | Α  | s | RdHi    | RdLo                     |    | Rn      |    |     | 1  | 0   | 0  | 1      | Rm                                     | Multiply Long                           |

| Cond                              | 0 | 0 | 0 | 1 | 0   | В        | 0  | 0 | Rn      | Rd                       | 0  | 0       | 0  | 0   | 1  | 0   | 0  | 1      | Rm                                     | Single Data Swap                        |

| Cond                              | 0 | 0 | 0 | 1 | 0   | 0        | 1  | 0 | 1 1 1 1 | 1 1 1 1                  | 1  | 1       | 1  | 1   | 0  | 0   | 0  | 1      | Rn                                     | Branch and Exchange                     |

| Cond                              | 0 | 0 | 0 | Р | U   | 0        | W  | L | Rn      | Rd                       | 0  | 0       | 0  | 0   | 1  | S   | Н  | 1      | Rm                                     | Halfword Data Transfer: Register offset |

| Cond                              | 0 | 0 | 0 | Р | U   | 1        | W  | L | Rn      | Rd Offset 1 S H 1 Offset |    |         |    |     | S  | Η   | 1  | Offset | Halfword Data Transfer: immediate offs |                                         |

| Cond                              | 0 | 1 | I | Р | U   | В        | W  | L | Rn      | Rd                       |    |         |    |     | C  | Off | se | t      |                                        | Single Data Transfer                    |

| Cond                              | 0 | 1 | 1 |   |     |          |    |   |         |                          |    |         |    |     |    |     |    | 1      |                                        | Undefined                               |

| Cond                              | 1 | 0 | 0 | Р | U   | S        | W  | L | Rn      |                          |    | R       | eg | ist | er | Lis | st |        |                                        | Block Data Transfer                     |

| Cond                              | 1 | 0 | 1 | L |     |          |    |   |         | Off                      | se | t       |    |     |    |     |    |        |                                        | Branch                                  |

| Cond                              | 1 | 1 | 0 | Р | U   | N        | W  | L | Rn      | CRd                      |    | CI      | Ρ# |     |    |     | (  | Off    | set                                    | Coprocessor Data Transfer               |

| Cond                              | 1 | 1 | 1 | 0 | C   | Р        | Op | С | CRn     | CRd                      |    | CI      | Ρ# |     | (  | CP  |    | 0      | CRm                                    | Coprocessor Data Operation              |

| Cond                              | 1 | 1 | 1 | 0 |     | CI<br>Op |    | L | CRn     | Rd CP# CP 1 CRm          |    |         |    |     | CP |     | 1  | CRm    | Coprocessor Data Transfer              |                                         |

| Cond 1 1 1 1 Ignored by processor |   |   |   |   |     |          |    |   |         | Software Interrupt       |    |         |    |     |    |     |    |        |                                        |                                         |

그림 2.2 ARM 명령어 집합 형태

표 2.1 ARM 명령어 셋 일람

| <b>班 2.1 ARM</b> | 표 2.1 ARM 명령어 셋 일람                             |                                            |  |  |  |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Mnemonic         | Instruction                                    | Action                                     |  |  |  |  |  |  |  |  |  |  |  |

| ADC              | Add with carry                                 | Rd := Rn + Op2 + Carry                     |  |  |  |  |  |  |  |  |  |  |  |

| ADD              | Add                                            | Rd := Rn + Op2                             |  |  |  |  |  |  |  |  |  |  |  |

| AND              | AND                                            | Rd := Rn AND Op2                           |  |  |  |  |  |  |  |  |  |  |  |

| В                | Branch                                         | R15 := Address                             |  |  |  |  |  |  |  |  |  |  |  |

| BIC              | Bit Clear                                      | Rd := Rn AND NOT Op2                       |  |  |  |  |  |  |  |  |  |  |  |

| BL               | Branch with Link                               | R14 := R15, R15 := Address                 |  |  |  |  |  |  |  |  |  |  |  |

| вх               | Branch and Exchange                            | R15 := Rn, T Bit := Rn[0]                  |  |  |  |  |  |  |  |  |  |  |  |

| CDP              | Coprocessor Data Processing                    | (Coprocessor-specific)                     |  |  |  |  |  |  |  |  |  |  |  |

| CMN              | Compare Negative                               | CPSR flags := Rn + Op2                     |  |  |  |  |  |  |  |  |  |  |  |

| CMP              | Compare                                        | CPSR flags := Rn - Op2                     |  |  |  |  |  |  |  |  |  |  |  |

| EOR              | Exclusive OR                                   | Rd := (Rn AND NOT Op2) OR (op2 AND NOT Rn) |  |  |  |  |  |  |  |  |  |  |  |

| LDC              | Load coprocessor from memory                   | Coprocessor load                           |  |  |  |  |  |  |  |  |  |  |  |

| LDM              | Load multiple Registers                        | Stack manipulation (Pop)                   |  |  |  |  |  |  |  |  |  |  |  |

| LDR              | Load Register from memory                      | Rd := (Address)                            |  |  |  |  |  |  |  |  |  |  |  |

| MCR              | Move CPU Register to coprocessor Register      | cRn := rRn { <op>cRm}</op>                 |  |  |  |  |  |  |  |  |  |  |  |

| MLA              | Multiply Accumulate                            | Rd := (Rm * Rs) + Rn                       |  |  |  |  |  |  |  |  |  |  |  |

| MOV              | Move Register or constant                      | Rd : = Op2                                 |  |  |  |  |  |  |  |  |  |  |  |

| MRC              | Move from coprocessor Register to CPU Register | Rn := cRn { <op>cRm}</op>                  |  |  |  |  |  |  |  |  |  |  |  |

| MRS              | Move PSR Status/flags to Register              | Rn := PSR                                  |  |  |  |  |  |  |  |  |  |  |  |

| MSR              | Move Register to PSR Status/flags              | PSR := Rm                                  |  |  |  |  |  |  |  |  |  |  |  |

| MUL              | Multiply                                       | Rd := Rm * Rs                              |  |  |  |  |  |  |  |  |  |  |  |

| MVN              | Move negative Register                         | Rd := 0XFFFFFFF EOR Op2                    |  |  |  |  |  |  |  |  |  |  |  |

| ORR              | OR                                             | Rd := Rn OR Op2                            |  |  |  |  |  |  |  |  |  |  |  |

| RSB              | Reverse Subtract                               | Rd := Op2 - Rn                             |  |  |  |  |  |  |  |  |  |  |  |

| RSC              | Reverse Subtract with Carry                    | Rd := Op2 - Rn - 1 + Carry                 |  |  |  |  |  |  |  |  |  |  |  |

| SBC              | Subtract with Carry                            | Rd := Rn - Op2 - 1 + Carry                 |  |  |  |  |  |  |  |  |  |  |  |

| STC              | Store coprocessor Register to memory           | Address:= CRn                              |  |  |  |  |  |  |  |  |  |  |  |

| STM              | Store Multiple                                 | Stack manipulation (Push)                  |  |  |  |  |  |  |  |  |  |  |  |

| STR              | Store Register to memory                       | < Address > := Rd                          |  |  |  |  |  |  |  |  |  |  |  |

| SUB              | Subtract                                       | Rd := Rn - Op2                             |  |  |  |  |  |  |  |  |  |  |  |

| SWI              | Software Interrupt                             | OS call                                    |  |  |  |  |  |  |  |  |  |  |  |

| SWP              | Swap Register with memory                      | Rd := [Rn], [Rn] := Rm                     |  |  |  |  |  |  |  |  |  |  |  |

| TEQ              | Test Bitwise equality                          | CPSR flags := Rn EOR Op2                   |  |  |  |  |  |  |  |  |  |  |  |

| TST              | Test Bits                                      | CPSR flags := Rn AND Op2                   |  |  |  |  |  |  |  |  |  |  |  |

|                  |                                                |                                            |  |  |  |  |  |  |  |  |  |  |  |

| ARM 상태 범용     | - 레지스터와 프              | 로그램 카운터          |          |                  |               |  |  |  |  |  |  |  |

|---------------|------------------------|------------------|----------|------------------|---------------|--|--|--|--|--|--|--|

| System & User | FIQ                    | Supervisor       | Abort    | IRQ              | Undefined     |  |  |  |  |  |  |  |

| R0            | R0                     | R0               | R0       | R0               | R0            |  |  |  |  |  |  |  |

| R1            | R1                     | R1               | R1       | R1               | R1            |  |  |  |  |  |  |  |

| R2            | R2                     | R2               | R2       | R2               | R2            |  |  |  |  |  |  |  |

| R3            | R3                     | R3               | R3       | R3               | R3            |  |  |  |  |  |  |  |

| R4            | R4                     | R4               | R4       | R4               | R4            |  |  |  |  |  |  |  |

| R5            | R5                     | R5               | R5       | R5               | R5            |  |  |  |  |  |  |  |

| R6            | R6                     | R6               | R6       | R6               | R6            |  |  |  |  |  |  |  |

| R7            | R7                     | R7               | R7       | R7               | R7            |  |  |  |  |  |  |  |

| R8            | R8_fiq                 | R8               | R8       | R8               | R8            |  |  |  |  |  |  |  |

| R9            | R9_fiq                 | R9               | R9       | R9               | R9            |  |  |  |  |  |  |  |

| R10           | R10_fiq                | R10              | R10      | R10              | R10           |  |  |  |  |  |  |  |

| R11           | R11_fiq                | R11              | R11      | R11              | R11           |  |  |  |  |  |  |  |

| R12           | R12_fiq                | R12              | R12      | R12              | R12           |  |  |  |  |  |  |  |

| R13           | R13_fiq                | R13_svc          | R13_abt  | R13_irq          | R13_und       |  |  |  |  |  |  |  |

| R14           | R14_fiq                | R14_svc          | R14_abt  | R14_irq          | R14_und       |  |  |  |  |  |  |  |

| R15 (PC)      | R15 (PC)               | R15 (PC)         | R15 (PC) | R15 (PC)         | R15 (PC)      |  |  |  |  |  |  |  |

| ARM 상태 프로     | ARM 상태 프로그램 스테이터스 레지스터 |                  |          |                  |               |  |  |  |  |  |  |  |

| CPSR          | CPSR SPSR_fiq          | CPSR<br>SPSR_svc | CPSR     | CPSR<br>SPSR_irq | CPSR SPSR_und |  |  |  |  |  |  |  |

| = banked reg  | gister                 |                  |          |                  |               |  |  |  |  |  |  |  |

그림 2.3 ARM 상태에서의 레지스터 구성

### 2.4.2 THUMB 명령어

|    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6   | 5 4 3    | 2 1 0          |                                        |

|----|----|----|----|----|----|----|----|------|-------|-----|----------|----------------|----------------------------------------|

| 1  | 0  | 0  | 0  |    |    |    |    | ffse |       |     | Rs       | Rd             | Move shifted Register                  |

| 2  | 0  | 0  | 0  | 1  | 1  | I  | Ор | Rn   | offs/ | et3 | Rs       | Rd             | Add/subtract                           |

| 3  | 0  | 0  | 1  | 0  | p  |    | Rd |      |       |     | Offset8  |                | Move/compare/add/subtract immediate    |

| 4  | 0  | 1  | 0  | 0  | 0  | 0  |    | С    | )p    |     | Rs       | Rd             | ALU operation                          |

| 5  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | р    | H1    | H2  | Rs/Hs    | Rd/Hd          | Hi register operations/branch exchange |

| 6  | 0  | 1  | 0  | 0  | 1  |    | Rd |      |       |     | word8    |                | PC-relative load                       |

| 7  | 0  | 1  | 0  | 1  | L  | В  | 0  |      | Ro    |     | Rb       | Rd             | Load/store with Register Offset        |

| 8  | 0  | 1  | 0  | 1  | Ι  | S  | 1  |      | Ro    |     | Rb       | Rd             | Load/store sign-extended Byte/Halfword |

| 9  | 0  | 1  | 1  | В  | ш  |    | 0  | ffse | t5    |     | Rb       | Rd             | Load/store with immediate              |

| 10 | 1  | 0  | 0  | 0  | L  |    | 0  | ffse | t5    |     | Rb       | Rd             | Load/store Halfword                    |

| 11 | 1  | 0  | 0  | 1  | L  |    | Rd |      |       |     | word8    |                | SP-relative load/store                 |

| 12 | 1  | 0  | 1  | 0  | SP |    | Rd |      |       |     | word8    |                | Load Address                           |

| 13 | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0    | S     |     | Sword    | <del>1</del> 7 | Add offset to stack pointer            |

| 14 | 1  | 0  | 1  | 1  | L  | 1  | 0  | R    |       |     | Rlist    |                | Push/pop Registers                     |

| 15 | 1  | 1  | 0  | 0  | L  |    | Rb |      |       |     | Rlist    |                | Multiple load/store                    |

| 16 | 1  | 1  | 0  | 1  |    | Со | nd |      |       |     | Soffset8 |                | Conditional branch                     |

| 17 | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1    |       |     | Value8   |                | Software Interrupt                     |

| 18 | 1  | 1  | 1  | 0  | 0  |    |    |      |       | Of  | ffset11  |                | Unconditional branch                   |

| 19 | 1  | 1  | 1  | 1  | Н  |    |    |      |       | Of  | ffset11  |                | Long branch with link                  |

|    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6   | 5 4 3    | 2 1 0          |                                        |

그림 2.4 THUMB 명령어 셋 포맷

표 2.2 THUMB 명령어 셋 일람

| Mnemonic | Instruction                 | Lo reg. oper. | Hi reg. oper | Condition code set |

|----------|-----------------------------|---------------|--------------|--------------------|

| ADC      | Add with Carry              | V             |              | V                  |

| ADD      | Add                         | V             | V            | V                  |

| AND      | AND                         | V             |              | V                  |

| ASR      | Arithmetic Shift Right      | V             |              | V                  |

| В        | Unconditional branch        | V             |              |                    |

| В хх     | Conditional branch          | V             |              |                    |

| BIC      | Bit Clear                   | V             |              | V                  |

| BL       | Branch and Link             |               |              |                    |

| вх       | Branch and Exchange         | V             |              | V                  |

| CMN      | Compare Negative            | V             |              | V                  |

| СМР      | Compare                     | V             | V            | V                  |

| EOR      | EOR                         | V             |              | V                  |

| LDMIA    | Load multiple               | V             |              |                    |

| LDR      | Load Word                   | V             |              |                    |

| LDRB     | Load Byte                   | V             |              |                    |

| LDRH     | Load Halfword               | V             |              |                    |

| LSL      | Logical Shift Left          | V             |              | V                  |

| LDSB     | Load sign-extended Byte     | V             |              |                    |

| LDSH     | Load sign-extended Halfword | V             |              |                    |

| LSR      | Logical Shift Right         | V             |              | V                  |

| MOV      | Move Register               | V             | V            | V                  |

| MUL      | Multiply                    | V             |              | V                  |

| MVN      | Move Negative Register      | V             |              | V                  |

| NEG      | Negate                      | V             |              | V                  |

| ORR      | OR                          | V             |              | V                  |

| POP      | Pop Registers               | V             |              |                    |

| PUSH     | Push Registers              | V             |              |                    |

| ROR      | Rotate Right                | V             |              | V                  |

| SBC      | Subtract with Carry         | V             |              | V                  |

| STMIA    | Store Multiple              | V             |              |                    |

| STR      | Store Word                  | V             |              |                    |

| STRB     | Store Byte                  | V             | _            |                    |

| STRH     | Store Halfword              | V             |              |                    |

| SWI      | Software Interrupt          |               |              |                    |

| SUB      | Subtract                    | V             |              | V                  |

| TST      | Test Bits                   | V             |              | V                  |

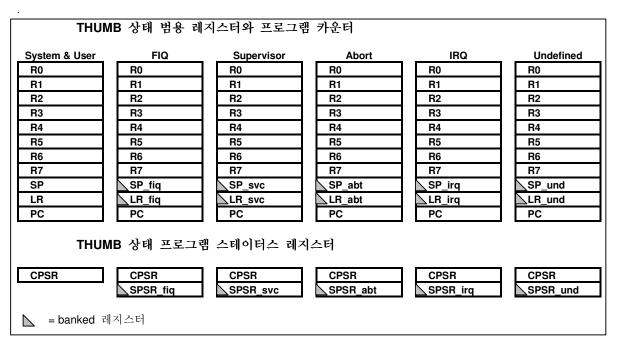

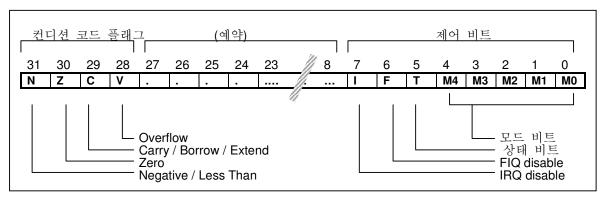

그림 2.5 THUMB 상태에서의 레지스터 구성

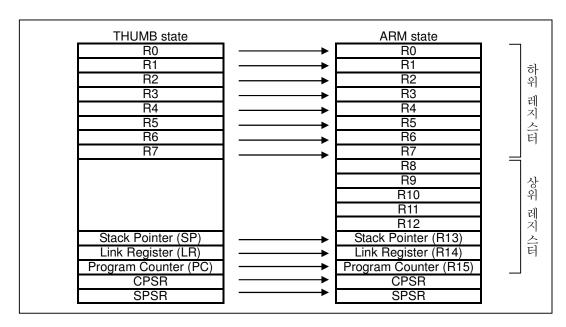

그림 2.6 THUMB 상태에서 ARM 상태로의 레지스터 변환

| 11. 2.U 1 | 2-72   |           |                                              |

|-----------|--------|-----------|----------------------------------------------|

| Code      | Suffix | Flags     | Meaning                                      |

| 0000      | EQ     | Z         | set equal                                    |

| 0001      | NE     | Z         | Clear not equal                              |