# Vision Hardware for a Humanoid Robot

Ho Wong s33544119

16<sup>th</sup> October 2002

#### ACKNOLEDGEMENTS

Gordon Wyeth for providing the thesis topic.

David Prasser for all his help and understanding of what I went through this year. Mark Chang for his help on understanding the SH4, camera and FPGA.

All the people on the vhdl newsgroup (comp.lang.vhdl) for helping me with my vhdl problems.

And all my friends who've encouraged me throughout the year when things looked the bleakest.

#### ABSTRACT

The University of Queensland has entered a humanoid robot (GuRoo) for Robocup's Humanoid Soccer League. GuRoo was first conceived in 2001 and its design was undertaken by 12 undergraduates.

The objective of this thesis is to take what's been previously done, combine them to make a vision system for the GuRoo and then make improvements. Objects on the playing field are colour-coded hence only 8 colours are approximately needed. The onboard memory on the vision board is only 512Kbytes and is barely sufficient to store a 240x180 (approximately 8cm x 6 cm) image. It is mainly because the image is stored as raw data. This can be greatly improved by moving the Colour Lookup onto the FPGA (Field Programmable Gate Array). Unfortunately, the FPGA has only 100,000 system gates and 10 x 4Kbytes of Block Ram. This means only a few pixels can be processed on the FPGA and a new Lookup Table has to be developed because a 256 x 256 Lookup Table (UV only) will exceed the available space. Timing is also critical because each pixel has to be processed by the time a new pixel is sent from the camera.

The greatest challenge this thesis faced was setting up of the SH4 and camera. The camera board and workings of the code were poorly documented and it was not until mid-year that all the setup needed for the thesis was completed. This left little time to pursue the improvements this thesis intended.

Only the Colour Lookup has been moved onto the FPGA. The time it takes to read a pixel's colour from the FPGA is  $\approx$  900ns and to do a colour lookup for a 240x180 image is  $\approx$  19.44ms. By removing the raw image from the SH4, it is now possible to store a 640x480 image or two 360x 270 images.

# **Table of Contents**

| 1 | Intro | duction                                         | . 1 |

|---|-------|-------------------------------------------------|-----|

|   | 1.1   | Thesis Objective                                | . 1 |

|   | 1.2   | The GuRoo Project                               | . 1 |

|   | 1.3   | Robocup                                         | . 3 |

|   | 1.4   | Robocup Vision                                  | . 4 |

| 2 | Prev  | ious Technology                                 | . 5 |

|   | 2.1   | Hitachi SH4                                     | . 5 |

|   | 2.1.1 | On Board Memory                                 | . 7 |

|   | 2.1.2 | 2 DMAC ( Direct Memory Access Controller)       | . 8 |

|   | 2.1.3 | Interfaces                                      | . 8 |

|   | 2.2   | Spartan II FPGA (Field Programmable Gate Array) | . 9 |

|   | 2.3   | Interface to the rest of the robot              | . 9 |

|   | 2.4   | OmniVision OV7620                               | 10  |

|   | 2.5   | Vision Software                                 | 12  |

|   | 2.5.1 | Colour Lookup                                   | 12  |

|   | 2.5.2 | 2 Morphological Erosion                         | 13  |

|   | 2.5.3 | Run Length Encoding (RLE)                       | 13  |

|   | 2.5.4 | Blob Detection                                  | 13  |

| 3 | Proje | ect Plan                                        | 14  |

|   | 3.1   | Summary of Vision System at the start of 2002   | 14  |

|   | 3.2   | Initial Project Plan                            | 14  |

|   | 3.3   | Project Progress by June                        | 15  |

| 4 | Tech  | nnical Design                                   | 17  |

|   | 4.1   | Problem Definition                              | 17  |

|   | 4.2   | Initial Approach                       |  |

|---|-------|----------------------------------------|--|

|   | 4.2.1 | Bruce's Lookup Table                   |  |

|   | 4.2.2 | 2 Distributed RAM vs Block RAM         |  |

|   | 4.2.3 | 3 Spartan II Block RAM                 |  |

| 5 | Desi  | gn Implementation                      |  |

|   | 5.1   | Testing Procedure                      |  |

|   | 5.2   | Test Environment                       |  |

|   | 5.2.  | Test Image Size                        |  |

|   | 5.2.2 | 2 Colour Codes                         |  |

|   | 5.2.3 | Bruce's Lookup Table                   |  |

|   | 5.3   | FPGA Software implementation           |  |

|   | 5.3.1 | Storage of Bruce's Lookup Table        |  |

|   | 5.3.2 | 2 Colour Lookup                        |  |

| 6 | Test  | ing and Analysis                       |  |

|   | 6.1   | Test Image                             |  |

|   | 6.2   | Lookup Table                           |  |

|   | 6.3   | Colour Coded Image                     |  |

|   | 6.4   | FPGA Resource Usage and Timing         |  |

|   | 6.5   | SH4 Timing                             |  |

|   | 6.5.  | Improving the Timing                   |  |

|   | 6.6   | Analysis of Results                    |  |

| 7 | Eval  | uation of Project                      |  |

|   | 7.1   | Evaluation of Project Goals            |  |

|   | 7.2   | Evaluation of Project Schedule         |  |

|   | 7.3   | Evaluation of Risk Management          |  |

|   | 7.4   | Recommendations for future improvement |  |

| 8 | Futu  | re Work                                |  |

|   | 8.1   | Data transfer between the SH4 and FPGA |  |

| 8.2      | Integration with OV7620         |    |

|----------|---------------------------------|----|

| 8.3      | Further Pre-processing          |    |

| 9 Coi    | nclusion                        | 41 |

| Bibliogr | aphy                            |    |

| Appendi  | x A: Colour Images              | 44 |

| Appendi  | x B: Users Manuals              |    |

| B.1      | Software Implementation         |    |

| B.1      | .1 Boot Loader                  |    |

| B.1      | .2 FPGA                         |    |

| B.1      | .3 Memory                       |    |

| B.1      | .4 GIO Ports                    |    |

| B.1      | .5 Interrupts                   |    |

| B.1      | .6 DMAC                         |    |

| B.2      | Users Manual                    |    |

| B.2      | .1 Initial Boot Up              |    |

| B.2      | .2 Cross-compiler               |    |

| B.2      | .3 Loading of Program           |    |

| B.2      | .4 Downloading of data          |    |

| B.2      | .5 Uploading of data            |    |

| B.2      | .6 Error Codes                  |    |

| Appendi  | x C: CODE                       |    |

| C.1      | FPGA CODE                       |    |

| C.2      | FPGA Synthesis Report (Trimmed) | 61 |

| C.3      | FPGA Map Report (Trimmed)       |    |

| C.4      | SH4 CODE                        |    |

# **List of Tables**

| Table 1-1: Colour Codes           | 4  |

|-----------------------------------|----|

| Table 2-1: Colour Formulas        | 10 |

| Table 2-2: 8bit 4:2:2             | 11 |

| Table 2-3: 16bit 4:2:2            | 11 |

| Table 4-1: Memory Usage           | 17 |

| Table 4-2: Projected Memory Usage |    |

| Table 6-1: SH4 timing             |    |

| Table 6-2: New SH4 Timing         |    |

| Table 6-3: Processing Time        |    |

| Table B-1: Camera Error Codes     |    |

|                                   |    |

# **List of Figures**

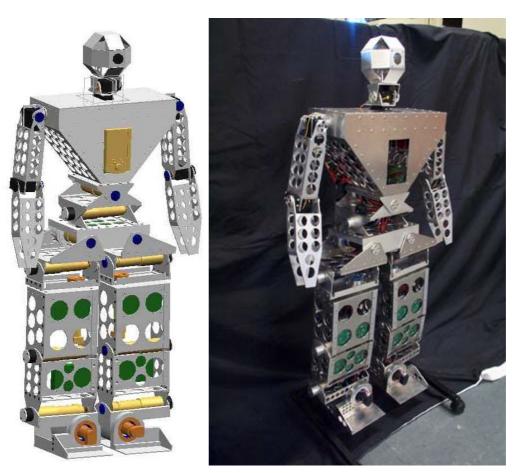

| Figure 1-1: GuRoo                         | 2  |

|-------------------------------------------|----|

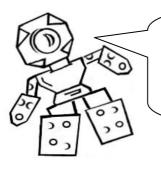

| Figure 2-1: Vision Board Block Diagram    | 6  |

| Figure 2-2: Memory Mapping                | 7  |

| Figure 2-3: Vision Software Block Diagram |    |

| Figure 2-4: RLE                           |    |

| Figure 2-5: Grouping                      |    |

| Figure 3-1: Initial Plan                  | 14 |

| Figure 3-2: New Project Plan              |    |

| Figure 4-1: Normal Lookup Table           |    |

| Figure 4-2: Bruce's Lookup Table          |    |

| Figure 4-3: FPGA Block Diagram            |    |

| Figure 4-4: Block Ram Timing              |    |

| Figure 5-1: Colour Codes                  |    |

| Figure 5-2: FPGA Flow Chart               |    |

| Figure 5-3: FPGA timing                   |    |

| Figure 5-4: Colour Lookup                 |    |

| Figure 5-5: Colour Lookup Timing          |    |

| Figure 6-1: RGB Image                     |    |

| Figure 6-2: YUV image                     |    |

| Figure 6-3: Normal Lookup Table           |    |

| Figure 6-4: Bruce's Lookup Table          |    |

| Figure 6-5: Colour Coded Image            |    |

| Figure 6-6: Memory Summary                |    |

| Figure 6-7: Timing Summary                |    |

| Figure 6-8: Toggle                        |    |

| Figure 8-1: Dual Port RAM                 |    |

| Figure 8-2: OV7620 Timing                 |    |

| Figure 8-3: OV7620 integration            |    |

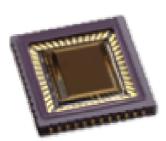

| Figure A-1: Spartan II xc2s100 FPGA         | . 44 |

|---------------------------------------------|------|

| Figure A-2: OmniVision OV7620               | . 44 |

| Figure A-3: Colour as a function of U and V | . 45 |

| Figure A-4: Vision Board                    | . 45 |

# **1** Introduction

## **1.1 Thesis Objective**

The objective of this thesis is to take what's been previously done, combine them to make a vision system for the GuRoo and then make improvements.

# 1.2 The GuRoo<sup>1</sup> Project

Due to the success of the RoboRoos (The University of Queensland's Small Sized Global Vision Robocup soccer team), the GuRoo was started in 2001 by a team of 12 undergraduate students to enter the Robocup2001 Humanoid Soccer League. The GuRoo is in the medium sized division (1.2m) although for Robocup2002, the size divisions were combined.

The difficulty of building a robot that can not only stand by itself, but move and decide its own actions based on what it sees and knows is unfathomable. Beyond the simple desire to play soccer with other robots, the GuRoo is a test bench for future University Of Queensland students to test new ideas on creating a humanoid that could eventually have the full capabilities of a real human being.

The GuRoo has 23 degrees of freedom corresponding to its 23 motors. There are 8 Hi-Tec HS705-MG Servo Motors controlling the upper body and 15 70W DC geared motors from Maxon control the lower body [1].

The 2002 GuRoo team consists of Ho Wong (Vision Hardware for a Humanoid Robot), Andrew Hood (Distributed Motion Controllers for a Humanoid Robot), Adam Drury (Gait Generation and Control Algorithms for a Humanoid Robot) and Ian Marshall (Active Balance Control for a Humanoid Robot). Supervising the project is Gordon Wyeth and Assistant supervisor is postgraduate student, Damien Kee.

<sup>&</sup>lt;sup>1</sup> Grossly Underfunded Roo. The 'Roo' has been adopted as a suffix for all of the University of Queensland's robot soccer teams.

a) CAD Drawing

b) Real Picture

Figure 1-1: GuRoo

FACT: There are over 600 individual muscles in the body which account for 40% of the body's weight.

Besides the hands and toes, GuRoo has almost all the major degrees of freedom as a human.

# 1.3 Robocup

RoboCup is an international research and education initiative. Its goal is to foster artificial intelligence and robotics research by providing a standard problem where a wide range of technologies can be examined and integrated. The concept of soccerplaying robots was first introduced in 1993. Following a two-year feasibility study, in August 1995, an announcement was made to introduce the first international conferences and soccer games. In July 1997, the first official conference and game was held in Nagoya, Japan. Followed by Paris, Stockholm, Melbourne and Seattle, the annual events attracted many participants. Following previous conferences and games, the 6th RoboCup will be held in Fukuoka, Japan in cooperation with Busan, Korea in June, 2002. This RoboCup will coincide with the"2002 World Cup Korea/Japan.<sup>2</sup>

There are various divisions in Robocup: Simulation, Small Sized Robot, Middle Size Robot, Sony Legged Robot and Humanoid. In the Humanoid division, there are also three height divisions: 40cm, 80cm and 120cm.

The University Of Queensland has 4 different teams: The CrocaRoo's (Simulation League); The RoboRoos (Small Sized League – Global Vision); The ViperRoos (Small Sized League – Local Vision) and the GuRoo (Humanoid League). The difference between Global Vision and Local Vision is that Global Vision uses overhead cameras whereas Local Vision uses cameras mounted on the robots themselves.

The Humanoid League competition for 2002 has many different events. These are: Humanoid Walk – humanoid is required to walk from a starting line, to and around a red marker and back again; Shoot – humanoid is required to kick a ball into the goal; Penalty Shoot Out – humanoid is required to kick a ball into a goal defended by another humanoid and Freestyle – humanoid has 10mins for freestyle actions [2]. For information on how well GuRoo performed in Robocup2002, please visit http://www.itee.uq.edu.au/~damien/\_guroo .

"By the year 2050, develop a team of fully autonomous humanoid robots that can win against the human world soccer champion team." – Robocup's Goal

<sup>&</sup>lt;sup>2</sup> Abstract from RoboCup2002 website: www.robocup2002.org

# **1.4 Robocup Vision**

The vision requirements for GuRoo are currently determined by the events in Robocup. The requirements needed to participate effectively in the events are:

- Ability to identify the ball and its location.

- Ability to identify objects, e.g. Opponents.

- Ability to identify the goal.

- Ability to identify the boundaries of the playing field.

The playing environment has been easily colour coded. **Table 1-1** shows the colour-coded environment [3].

| Object              | Colour         |

|---------------------|----------------|

| Field               | Green          |

| Ball                | Red            |

| Edge of Field Lines | White          |

| Opponents           | Black          |

| Goals               | Blue or Yellow |

Table 1-1: Colour Codes

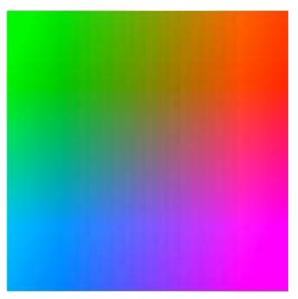

There are many problems involved with colour detection. One of the major problems is ambient light. All the studio lighting will make everything very bright and saturate any light sensitive sensors. The solution to this is to view everything in YUV as opposed to RGB. In YUV, the visible colour spectrum is mapped onto U (Red chrominance) and V (Blue chrominance). The intensity is mapped onto Y (Yellow). **Figure A3** shows the colour spectrum mapped onto U and V. This should solve the ambient light problem.

Another problem is identifying distances to objects. With only a single camera, the size of objects has to be pre-known. For the ball, it is simple because no matter which angle it is viewed from, it is always round. However, an opponent robot would be much thinner when viewed from the side than it would be when viewed from the front. This problem; however, is beyond the scope of this thesis.

# **2** Previous Technology

It is silly to reinvent something that's already available. Mark Chang is a postgraduate working under Gordon Wyeth. He worked on the ViperRoos<sup>3</sup> for three years. Recently, he has been developing a new vision board and camera to supersede the current ones used in the ViperRoos. The ViperRoos run on SH3 microprocessors and use a PB-159 Photobit CMOS camera. The new boards use SH4 microprocessors and use a CMOS OmniVision OV7620 camera.

David Prasser and Andrew Blower were undergraduate thesis students who were part of the 2001 GuRoo team. David Prasser's thesis was on Vision Software for a Humanoid robot and Andrew Blower's thesis was on Vision Hardware for a Humanoid Robot.

# 2.1 Hitachi SH4

The vision system that the GuRoo uses is the new vision board developed by Mark Chang. The core processor is the Hitachi SH4. The SH4 runs at 360MIPS (Mega Instructions Per Second) whereas the SH3 ran at 104MIPS.

A general block diagram of the vision board is shown in **Figure 2-1**. The following pages are a brief documentation of some of the SH4's functionalities and the setup done by Mark Chang.

<sup>&</sup>lt;sup>3</sup> University Of Queensland's Small Localised Vision, Robocup Soccer Team.

Figure 2-1: Vision Board Block Diagram

The SH4 has 3 external memory banks and 1 bank of EEPROM. There are also 2 serial ports, a USB controller and a Peripheral Controller which has an infra-red sensor, parallel port and a UART serial port. Connected to this is a SpartanII FPGA that is also the interface to the OmniVision OV7620 camera and other external devices: push buttons, LEDs, usb port and an expansion port.

### 2.1.1 On Board Memory

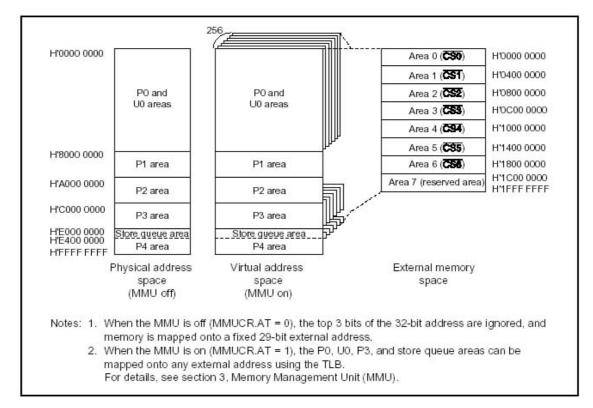

The SH4 runs on external memory. Only 8Kbyte can be used as on-chip RAM. There are four blocks of 128Kbyte SRAM stacked together to form a single 512Kbyte bank and four blocks of 2Mbyte SDRAM in each of the two 8Mbyte SDRAM banks. There is also 768Kbyte of EEPROM made up by stacking a 512Kbyte and a 256Kbyte chip. Only the SRAM is used because it performs much faster than the SDRAM but as expected, it costs much more as well. The price of the SRAM is approximately \$10 per 128Kbyte chip compared to \$6 for per 8Mbyte SDRAM chip. The memory addressing of the SH4 is shown in **Figure 2-2** [4]. Area's P0 to P4 are physically mapped and Area's 0-7 are external memory. Areas U0, P0 and P3 are accessed using the TLB (Translation Lookaside Buffer), while areas P1, P2 and P4 are not accessed using the TLB.

Figure 2-2: Memory Mapping

### 2.1.2 DMAC (Direct Memory Access Controller)

The SH4 has 4 DMA channels. In normal operation, only channels 1 and 2 can have external requests. On board peripherals can be used on all 4 channels. In DDT (Direct Data Transfer) Mode, all 4 channels can have external requests. There are two modes of DMA transfer available: Cycle Steal Mode and Burst Mode. In Cycle Steal Mode, the DMAC holds the bus until a transfer-unit (8-bit, 16-bit, 32-bit, 64- bit or 32-byte) is transferred. Burst Mode is when the DMAC holds the bus and only releases it back to the CPU after all the transfer-units in a block are transferred.

### 2.1.3 Interfaces

The Hitachi SH4 has a single-channel serial communication interface (SCI) and a single-channel serial communication interface with built-in FIFO registers. The SCI can handle both asynchronous and synchronous serial communication while the SCIF is a dedicated asynchronous serial communication interface with a 16-stage FIFO registers. Both are full duplex. The benefit of a FIFO register is that serial data can be continuously transmitted or received until part or all of the 16-stage registers are used up.

There are 20 general purpose I/O pins (GIO PINs). The direction for each pin can be individually specified as can the use of a pull-up resistor. Interrupt input is possible for 16 of the 20 pins.

Interfaced to the FPGA is also a 32bit data bus and 19bit address bus. This is for when memory is created on the FPGA and added onto the SH4's addressable external memory.

"If the automobile had followed the same development cycle as the computer, a Rolls-Royce would today cost \$100, get a million miles per gallon, and explode once a year, killing everyone inside".

- Robert X. Cringely, InfoWorld magazine

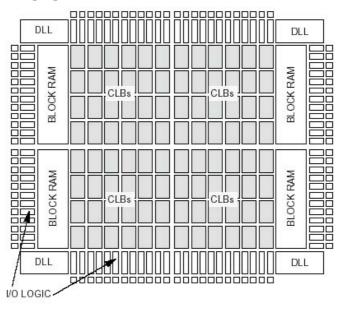

# 2.2 Spartan II FPGA (Field Programmable Gate Array)

An FPGA can be thought of as a software programmable hardware interface. The device that is used in the vision board is a Spartan II xc2s100. The xc2s100 has 100, 000 System Gates, 176 I/O pins, 4 Delay-Lock Loops and 40K of Block RAM. The xc2s100 has a system speed of over 200MHz [5]. Previously, the FPGA only acted as a direct connection between all the peripherals: camera, USB, Expansion Port and LEDs etc. and the SH4.

The Spartan II xcs100 does not have enough memory to store a whole picture on it. It is; therefore, only possible to store images either pixel-by-pixel or by blocks of pixels.

Currently, the USB and Expansion Port are disabled. Nearly all of the 176 I/O pins have been assigned: 32 pins for the data bus, 19 pins for the address bus, 16 pins for the camera data, 20 pins for each of the GIO, and the rest made up by control signals to and from the SH4 and the peripheral modules. Provision has been made for the use of the Block RAM but has not been implemented.

### **2.3 Interface to the rest of the robot**

Originally, the SH4 interfaces to an IPAQ but this year, the IPAQ has been put aside as there were insufficient resources to complete its interface. The main processing code for the GuRoo is currently running from Board 6 – the motor control board for the upper torso.

Serial port SCIF can be used to interface to the SH4. Currently, serial ports SCI and SCIF are being used to interface to a PC for testing and debugging; therefore, changing SCIF to interface to Board 6 or the IPAQ is easy.

A future development for the GuRoo is to create a separate control board (Board 7).

# 2.4 OmniVision OV7620

The OmniVision OV760 is a CMOS digital camera able to take YCrCb or YUV (Yellow, Red chrominance, Blue chrominance) and RGB (Red, Green, Blue) images. The formulas for YUV and YCrCb are shown in **Table 2-1** [6].

|   | YUV Colour                        | YCrCb Colour |                                   |

|---|-----------------------------------|--------------|-----------------------------------|

| Y | 0.299 x R + 0.587 x G + 0.114 x B | Y            | 0.299 x R + 0.587 x G + 0.114 x B |

| U | -0.147 x R -0.289 x G + 0.436 x B | Cb           | $(B - Y)/(2 - 2 \times 0.114)$    |

| V | 0.615 x R - 0.515 x G - 0.100 x B | Cr           | (R - Y)/(2-2 x 0.299)             |

Table 2-1: Colour Formulas

The default output for the OV7620 is  $640 \times 480$  but it has a windowing feature enabling the window size to be changed anywhere from 4x2 to 664x492. The OV7620 supports both interlaced and progressive scanning.

The OV7620 was the camera of choice by Mark Chang for the ViperRoos and so it was adopted along with his vision board for the GuRoo. One reason for its choice is that the output is digital and not analogue. This means less noise and better performance (i.e. no need for an A/D converter). The other reason is that it supports the YUV colour space because, as mentioned earlier, colour detection in YUV is the best method.

Output for YUV is either 8bit or 16bit 4:2:2. If it is 8bit, the transfer rate is twice the pixel rate. **Table 2-2** and **Table 2-3** [7] on the next page show the output timing for 16bit and 8bit transfer.

Control of the registers is done through the SCCB (Serial Camera Control Bus), which is half duplex and timing has to be carefully monitored. Refer to the datasheets for more detail.

| Data Bus    | Pixel Byte Sequence |    |     | Pi | xel Byte | e Sequen | ce |    |

|-------------|---------------------|----|-----|----|----------|----------|----|----|

| Y7          | U7                  | Y7 | V7  | Y7 | U7       | Y7       | V7 | Y7 |

| Y6          | U6                  | Y6 | V6  | Y6 | U6       | Y6       | V6 | Y6 |

| Y5          | U5                  | Y5 | V5  | Y5 | U5       | Y5       | V5 | Y5 |

| Y4          | U4                  | Y4 | V4  | Y4 | U4       | Y4       | V4 | Y4 |

| Y3          | U3                  | Y3 | V3  | Y3 | U3       | Y3       | V3 | Y3 |

| Y2          | U2                  | Y2 | V2  | Y2 | U2       | Y2       | V2 | Y2 |

| Y1          | U1                  | Y1 | V1  | Y1 | U1       | Y1       | V1 | Y1 |

| Y0          | U0                  | Y0 | V0  | Y0 | U0       | Y0       | V0 | Y0 |

| Y Frame 0 1 |                     | 1  | 2 3 |    |          | 3        |    |    |

| UV Frame    | 0                   |    |     |    |          | 1        |    |    |

Table 2-2: 8bit 4:2:2

| Data Bus | Pixel Byte Sequence |    |    |    |

|----------|---------------------|----|----|----|

| Y7       | Y7                  | Y7 | Y7 | Y7 |

| Y6       | Y6                  | Y6 | Y6 | Y6 |

| Y5       | Y5                  | Y5 | Y5 | Y5 |

| Y4       | Y4                  | Y4 | Y4 | Y4 |

| Y3       | Y3                  | Y3 | Y3 | Y3 |

| Y2       | Y2                  | Y2 | Y2 | Y2 |

| Y1       | Y1                  | Y1 | Y1 | Y1 |

| Y0       | Y0                  | Y0 | Y0 | Y0 |

| UV7      | U7                  | V7 | U7 | V7 |

| UV6      | U6                  | V6 | U6 | V6 |

| UV5      | U5                  | V5 | U5 | V5 |

| UV4      | U4                  | V4 | U4 | V4 |

| UV3      | U3                  | V3 | U3 | V3 |

| UV2      | U2                  | V2 | U2 | V2 |

| UV1      | U1                  | V1 | U1 | V1 |

| UV0      | U0                  | V0 | U0 | V0 |

| Y Frame  | 0                   | 1  | 2  | 3  |

| UV Frame | (                   | )  |    | 1  |

Table 2-3: 16bit 4:2:2

### 2.5 Vision Software

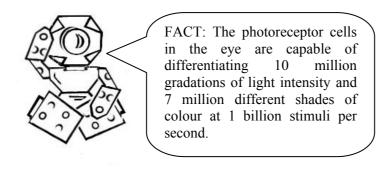

Vision Software had been developed by David Prasser in 2001 for the GuRoo. The image processing is described in **Figure 2-3**.

Figure 2-3: Vision Software Block Diagram

### 2.5.1 Colour Lookup

Colour Lookup is done through the use of a Lookup Table. There are only a preset number of colours that the GuRoo has to identify. These were described in **Table 1-1**. The code for sorting out which pixel belongs to which colour is described below [3]:

if Y > Max Threshold colour = White elsif Y< Min Threshold colour = Black else colour = Lookuptable(U,V) // Where U and V are indexes to the lookup table

Y measures the intensity of the colour; therefore, Max Threshold is the intensity threshold for white and Min Threshold is the intensity threshold for black. Whatever's in between is sorted through the Lookup Table. The Lookup Table is a simple table with vertices made up by the U and V components. One of the problems that occur is the identification of the colour yellow. Yellow is very close to white and hence unless the Max Threshold is calibrated properly, what is yellow will be categorised as white. **Figure 6-3** in Chapter 6: Testing and Analysis, shows a sample lookup table.

### 2.5.2 Morphological Erosion

After the colour lookup, each pixel is colour coded. Morphological Erosion is then used to remove noise. E.g. a black pixel surrounded by red pixels would be removed. For more information regarding Morphological Erosion, please refer to David Prasser's Undergraduate Thesis [3].

### 2.5.3 Run Length Encoding (RLE)

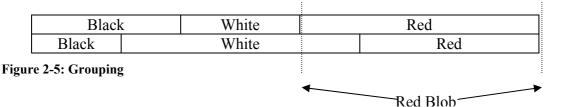

Run length encoding is where each row is examined and every run of the same colour becomes RLE elements. Each RLE element contains: the start x coordinate; end x coordinate; y coordinate; colour; run number and blobpointer. Figure 2-4 shows an example of RLE.

| Black |  | White | Red |  |

|-------|--|-------|-----|--|

| Black |  | White | Red |  |

Figure 2-4: RLE

### 2.5.4 Blob Detection

Each run is examined one at a time and compared to the runs on the following row. Runs that have the same colour and are directly underneath each other are grouped together to form a blob. **Figure 2-5** shows how a red blob is formed.

A blob is a four connected region of pixels of the same colour. Blobs have an: area, colour and rectangular boundary co-ordinates.

These blobs are then analysed and associated with objects. E.g. the large white blobs are walls, the largest red blob is the ball and any black blob greater than a certain size is an object.

# **3 Project Plan**

### 3.1 Summary of Vision System at the start of 2002

By the end of 2001, the GuRoo's Vision System was using the SH4 vision board developed by Mark Chang but did not have a working camera. David Prasser did all of his vision software using images downloaded from a PC through serial communications. Andrew Blower wrote FPGA code for a dual ram buffer [8] but could only test it in simulation because there was no working camera. The interface to the IPAQ was not fully developed either.

At the start of 2002, it was said that Mark Chang had developed a working camera board and that the board he developed should be used on the GuRoo. Unfortunately, Mark Chang went on leave for half a year and was not contactable until July, second semester.

# 3.2 Initial Project Plan

Robocup2002 was held from Wednesday June 19<sup>th</sup> to Tuesday June 25<sup>th</sup> in Fukuoka, Japan. At the start of the year, a project plan was drawn up for the development of the vision system of the GuRoo. This was outlined in the Progress Report and is shown in **Figure 3-1** [9].

| Task                                   | Duration | Start Date |

|----------------------------------------|----------|------------|

| SH4 Board Setup                        | 1day     | April 2    |

| SH4 Compiler (example LED code)        | 2days    | April 3    |

| David Prassers' old code running       | 4days    | April 5    |

| FPGA (Camera to SH4)                   | 5days    | April 9    |

| Camera (filling SH4 buffer with image) | 7days    | April 14   |

| Image back to PC                       | Odays    | April 21   |

| Ball/ Horizon detection                | 10days   | May 1      |

| Bearing/ distance to ball              | 10days   | May 11     |

| Main area of Interest                  | 10days   | May 21     |

| Serial Tx of vision information        | 5days    | May 25     |

Figure 3-1: Initial Plan

This plan was made based on the assumption that the camera was working. All that needed to be done was to plug it in and the setup for the SH4 would be easy.

To make the deadline for the competition, it was initially decided that the goal was to get the GuRoo being able to see a red ball or red object. To this end, all that was needed was to run David's Prasser's vision code with images taken from a camera mounted in its head. The FPGA would be a direct wire connection between the camera and the SH4. Interface from the SH4 to the rest of the Humanoid would be through serial communications.

## **3.3 Project Progress by June**

Unfortunately, problems were rife throughout the whole project. At the start, David Prasser did not leave behind the SH4 cross-compiler and a new one had to be made. Little problems like:

- Inability to find a computer that had RPM (RedHat Package Manager).

- Only newest version of cross-compiler available.

Made the progress very slow. Only source documents compressed with RPM could be found. While it may seem to be a simple matter, the fact was that all the UNIX computers available to students used SunOS on Sun Spark computers. There was no available Linux Operating System and RPM could not be installed onto the SunOS computers due to security reasons. Weeks were wasted while attempting to make the cross-compiler. The solution finally came in the form of a Backup CD found on Mark Chang's desk. This provided the cross-compiler he used as well as all the source codes.

By the time the setup was complete for the SH4's usage, the initial goals could not be met. Mark Chang returned in July and was of invaluable help in understanding the vision board but; unfortunately, there were only 11 weeks left and hence a new project plan was drafted.

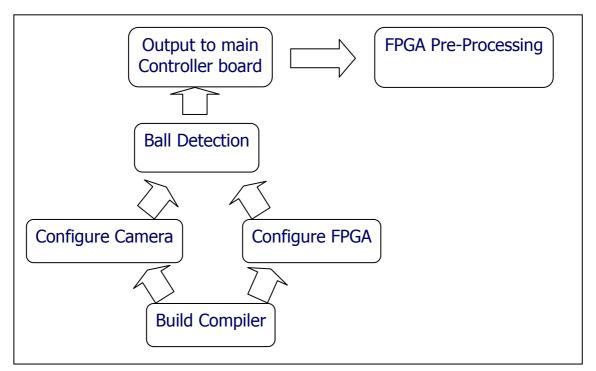

Figure 3-2: New Project Plan

**Figure 3-2** shows the Block Diagram for the new plan [10]. Due to the amount of time left, the main focus of the thesis had to be shifted to the FPGA, where the pre-processing of the image will be done. Performance of image processing can be greatly improved if the pre-processing is taken off the SH4 because the FPGA runs at a much faster speed than the SH4.

By September, the camera was still not working and it was finally accepted that all the cameras available (2 built by Mark Chang and 1 built by Ho Wong) may not be operational. Configuration of the camera was put aside and the focus of the thesis moved onto the FPGA pre-processing.

The time left was judged to be sufficient for research and development on the FPGA, even though Ho Wong had no prior experience with FPGAs and the software required to program them. The programming language, VHDL, will have to be learnt from the basics.

The steps that need to be completed for the FPGA pre-processing are:

- Learn VHDL.

- Storage and retrieval of lookup-table on FPGA.

- Colour Lookup with static inputs pixel's colour a static constant.

- Colour Lookup with dynamic inputs pixel's colour provided by SH4.

- Colour Lookup of whole image.

- Optimisation of process.

# **4** Technical Design

### 4.1 Problem Definition

There is only 512Kbyte of SRAM available on the SH4. SRAM performs much faster than SDRAM so the usage of the SDRAM was never even been considered.

Table 4-1 shows the memory usage on the SH4 with David Prasser's vision software

[3].

| Buffer                | Size      | Memory   |

|-----------------------|-----------|----------|

| YUV Image             | 240 x 180 | 168.75KB |

| Lookup Table          | 256 x 256 | 64KB     |

| Colour Detected Image | 240 x 180 | 42.2KB   |

| Eroded Image          | 240 x 180 | 42.2KB   |

| RLE Elements          | 3072      | 72KB     |

| Blobs                 | 512       | 12KB     |

| Objects               | 64        | 768Bytes |

| Edge Profile          | 180       | 720Bytes |

| Total                 |           | 401.8KB  |

#### Table 4-1: Memory Usage

The biggest usage of memory is the storage of the raw YUV image. Each pixel has an 8-bit Y, U and V component. The size of the YUV Image (240x180) chosen by David Prasser was the largest image possible keeping the 4:3 ratio. The Colour Detected Image is only a 240 x 180 table of 8 bit data. A full 640 x 480 Colour Detected Image with 4 bit data will only take up 153.6KB of memory. Removing the YUV Image and the Lookup Table from the SH4 will free up 232.75KB of memory. If dual ram buffering is required an image 360 x 270 could be used.

Table 4-2 shows the projected memory usage if two 360x270 Colour Detected Images are used.

| Buffer                  | Size      | Memory   |  |

|-------------------------|-----------|----------|--|

| Colour Detected Image 1 | 360 x 270 | 97.2KB   |  |

| Colour Detected Image 2 | 360 x 270 | 97.2KB   |  |

| Eroded Image            | 360 x 270 | 97.2KB   |  |

| RLE Elements            | 3072      | 72KB     |  |

| Blobs                   | 512       | 12KB     |  |

| Objects                 | 64        | 768Bytes |  |

| Edge Profile            | 180       | 720Bytes |  |

| Total                   |           | 377.1KB  |  |

Table 4-2: Projected Memory Usage

This is assuming that the RLE Elements, Blobs and objects stay the same. Even if they increase, there is still enough space.

### 4.2 Initial Approach

The FPGA only has 100,000 system gates and 40KB of Block Ram. An image 240 x 180 will definitely not fit inside it. The Lookup Table will have to be stored inside the FPGA as well. Unfortunately, the standard Lookup Table takes up 64KB of memory and there is not enough Block RAM to store it. Distributed RAM could be used but the better solution is to find a different way to do the colour lookup.

### 4.2.1 Bruce's Lookup Table<sup>4</sup>

The solution to the colour lookup is what can be thought of as a compressed lookup table. A normal 2 dimensional lookup table lists, for every index of V and U, a colour. This makes a 256 x 256 8bit table if the colour is an 8bit data type. Bruce's Lookup Table only has two 256 arrays of the number of bits corresponding to the total number of available colours. For example, if the total number of colours is 8, then it will have two 256 8bit arrays.

<sup>&</sup>lt;sup>4</sup> Named after James Bruce, co-author of *Fast and Inexpensive Color Image Segmentation for Interactive Robots* [11]

It uses a bitwise AND of the U and V arrays to check if it belongs in a certain colour. A small example is provided below.

If the available colour range is 8, then a normal UV Lookup Table would look similar to **Figure 4-1**. Where G, Y B & R are: Green, Yellow, Blue and Red respectively. The data types of these can be anywhere from 4 bits to 8 bits.

To find out the colour of pixel  $\langle U, V \rangle \langle 1, 2 \rangle$ , the row U1 would be searched until element V1 is found and the colour contained there is retrieved (reverse process for column major) In this example, it would be the colour Yellow.

| U7 | G  | G  |    |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|

| U6 | G  | G  |    |    |    |    |    |    |

| U5 | G  |    |    |    | В  | В  |    |    |

| U4 |    |    |    |    |    |    |    | R  |

| U3 |    |    | Y  |    |    |    | R  | R  |

| U2 |    | Y  | Y  | Y  |    | R  | R  | R  |

| U1 |    | Y  | Y  |    |    | R  | R  | R  |

| U0 | Y  | Y  |    |    | R  | R  | R  | R  |

|    | V0 | V1 | V2 | V3 | V4 | V5 | V6 | V7 |

Figure 4-1: Normal Lookup Table

If we assume each colour is a 4bit data type, then the total memory usage would be

8 x 8 x 4 = 256 bits.

Bruce's Lookup Table would look similar to **Figure 4-2**. Here there are two arrays: one for U and one for V. Each element of U and V have 4 bit data with each bit representing whether or not that element is part of a colour or not.

To find the colour of pixel  $\langle U, V \rangle \langle 1, 2 \rangle$  element U1 [0, 1, 0, 1] would be bit ANDed with element V2 [0, 1, 0, 0] which would produce:

Which corresponds to the colour Yellow.

| R | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  |

|---|----|----|----|----|----|----|----|----|

| В | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| Y | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| G | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  |

|   | U0 | U1 | U2 | U3 | U4 | U5 | U6 | U7 |

|   |    |    |    |    |    |    |    |    |

| R | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

| В | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  |

| Y | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| G | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

|   | V0 | V1 | V2 | V3 | V4 | V5 | V6 | V7 |

Figure 4-2: Bruce's Lookup Table

The memory total memory usage would be

$$2 \times 8 \times 4 = 64$$

bits

As can be seen, the size of this table is a quarter the size of a normal Lookup Table. If there are 8 colours (i.e. all 4 bits in the normal lookup table correspond to a colour) then Bruce's Lookup Table will require 8 bits per element but the total size will still be smaller than the normal Lookup Table (128bits). Bruce's Lookup Table has the same functionality except that it uses a lot smaller space.

A normal 256 x 256 table with 8 bit data (has a capacity to represent 256 colours) would take up approximately 65.5Kbytes. Bruce's Lookup Table would take up 16.4Kbytes when representing 256 colours.

### 4.2.2 Distributed RAM vs Block RAM

Distributed RAM is where RAM is created from the system gates. The advantages of using Distributed RAM are:

- Variable RAM size no need to stack RAM blocks.

- Maximum size dependant on available system gates

- Variable interface i.e. buses are user defined

Disadvantages are:

- Non-dedicated hardware would run slower than actual RAM

- A driver would have to be created.

- Timing not predefined the timing would be determined by the coding inside the driver.

The main factor in deciding which type to use was ease of use. Time is very limited and the easiest solution would be the Block RAM. It is the easiest to implement because all the drivers already exist. The drawback is that Block RAM comes in 4KB blocks. To stack them would also require a separate driver program or the use of a core generator.

### 4.2.3 Spartan II Block RAM

The Spartan II series of FPGA comes with 2 columns of Block RAM located to the left and right of the CLB, as shown in **Figure 4-3**. The number of Block RAM available is dependent upon the version of Spartan II, with the minimum being 4 blocks and the maximum being 20 blocks. The xc2s100 has 10 blocks making a total of 40KB of available Block Ram. [12]

Figure 4-3: FPGA Block Diagram

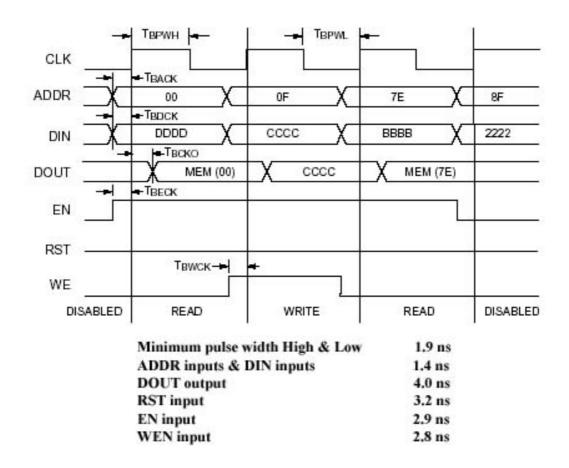

The timing for the Block RAM is shown in **Figure 4-4**.[13]

On the rising edge of CLK, the WE, ADDR, DI & EN pins are sampled. If WE & EN is high (write), then DI is written into address ADDR and DO mirrors the data. If WE is low & EN is high (read), then DO mirrors the data stored in address ADDR. If EN is low, reading and writing are disabled and DO retains its last value. If RST is high, DO is latched to low.

Figure 4-4: Block Ram Timing

As can be seen from **Figure 4-4**, the Block RAM is very fast. Mark Chang has made provision for the addition of the FPGA's Block RAM onto the SH4's BSC (Bus State Controller).

# **5 Design Implementation**

## **5.1 Testing Procedure**

All three cameras available were deemed inoperable; therefore, David Prasser's method of downloading an image directly to the SH4 from a PC had to be adopted [3]. The experiment procedure is:

- Take picture from normal digital camera.

- Convert picture into YUV colour space through Matlab.

- Download picture into SH4 through serial communications.

- Download Lookup Table into SH4 through serial communications.

- Upload Lookup Table into FPGA.

- Upload a pixel from SH4 into FPGA and receive back the associated colour. Repeat for all the pixels in picture.

- Upload colour-coded image back to the PC for verification.

### **5.2 Test Environment**

#### 5.2.1 Test Image Size

David Prasser used a 240 x 180 image because it was the largest possible size for the given memory available. The image that will be used to test the FPGA pre-processing is  $150 \times 112$ . This will free up memory to store the new Lookup Table.

#### 5.2.2 Colour Codes

There are only 4 colours besides white and black that will be used. These are: Red, Yellow, Green and Blue. The colour codes are displayed in **Figure 5-1**.

| RED    | 00000001 |

|--------|----------|

| YELLOW | 00000010 |

| GREEN  | 00000011 |

| BLUE   | 00000100 |

| WHITE  | 00000101 |

| BLACK  | 00000110 |

| OTHER  | 00000000 |

|        |          |

Figure 5-1: Colour Codes

#### 5.2.3 Bruce's Lookup Table

There are only 4 colours in the Lookup Table; therefore, only 4 bits are needed for the Lookup Table. The Lookup Table will be a 256 array of 8 bit data. Each 8 bit data contains both the U and the V.

MSB <7 6 5 4><3 2 1 0> LSB < U >< V > <B G Y R><B G Y R>

The Lookup Table now only takes up 256 bytes of memory.

### 5.3 FPGA Software implementation

It was decided to use GIO pins 0 to 7 as the FPGA's data bus for simplicity. There were not enough free GIO pins for a 16bit bus because 4 are used for the LED's and another 4 are used for the camera's SCCB control. GIO pin 10 has been temporarily used as the source for an external clock. The input and output buses (DI & DO) are tri-stated to the GIO bus.

#### 5.3.1 Storage of Bruce's Lookup Table

Bruce's Lookup Table is stored on the FPGA's Block RAM. Initial design of the code was to store each byte of the table at each state change of the external clock (rising and falling edge). This proved to be impossible to implement due to the need to clock the Block RAM twice in one clock cycle.

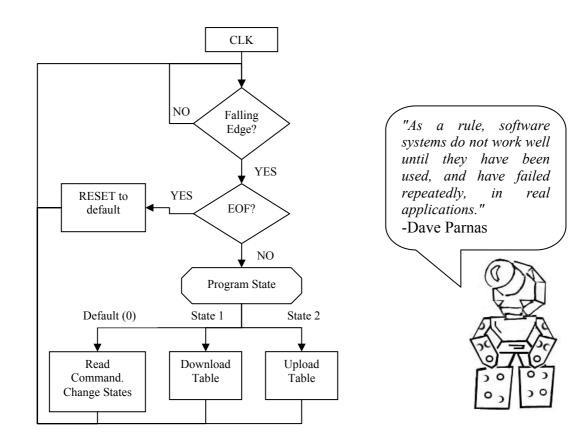

The current implementation is shown in **Figure 5-2**. The program continually checks the input data bus for commands. When a command is received, the state is changed and the program stays in that state till all the data is uploaded or downloaded. If more commands are required, additional states can be added easily. **Figure 5-3** shows the timing for the program.

Figure 5-2: FPGA Flow Chart

Figure 5-3: FPGA timing

As can be seen from the Block RAM timing diagram in **Figure 4-4**, the Block RAM only samples the input pins at the rising edge of the clock. The minimum hold time for the clock is 1.9ns and the largest minimum setup time for any of the inputs is 2.9ns (EN). If the clock had a period of at least 6ns, then it is possible to configure the setup on the falling edge and the Block RAM would do the read/write on the rising edge.

### 5.3.2 Colour Lookup

There were several options for the implementation of the colour lookup. The Lookup Table is stored in Block RAM and can only be accessed through the Block RAM's interface.

The pixel's raw YUV data and the colour for that pixel can be stored as either Block RAM or as a signal.

There are two methods to extract the lookup table from the Block RAM. One is to use the same input and output buses to retrieve the table. If the Block RAM is not used after storage of the Lookup Table, this method would be appropriate.

The other method is to use Dual Port RAM. This way, the SH4 can read from the Block RAM while the FPGA is writing into the Block RAM. Disadvantages of Dual Port RAM are that half the accessible memory is lost and a second clock signal has to be established.

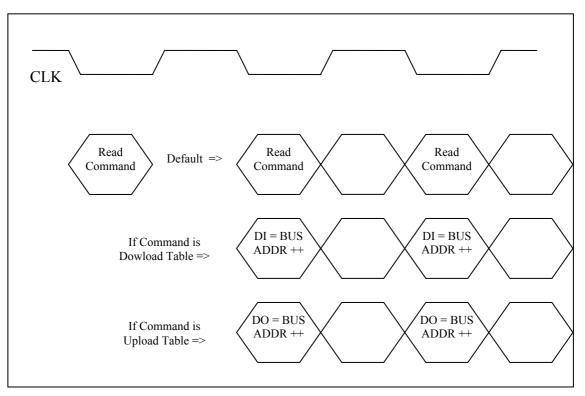

The method that is currently being implemented is to only store the Y data and rout the U and V straight into the address bus. Therefore, at the next clock cycle, the indexed element is retrieved from the DO bus. The Y data and the lookup table elements for U and V are stored as signals. The pseudo code is shown in **Figure 5-4**. The timing of the code is shown in **Figure 5-5**.

Implementation is simply done by adding another state to the command process.

```

if counter = 5

addr bus = 0;

counter = 0;

elsif State = ColourLookup

switch counter

case 0 : Y = in bus; // First byte is Y

case 1 : addr bus = in bus; // Load U to read.

case 2 : U = out bus: // Take element from lookup table

addr bus = in bus // Load V to read.

case 3 : V = out bus; // Take element from lookup table

// This step calls a function returns the bitwise AND of

// U and V. Signals don't update till after the process is

// finished in VHDL.

temp var = bit and(U,out bus)

case 4 : if Y > YMAX

pixel = WHITE;

elsif Y < YMIN

pixel = BLACK;

else // Do colour lookup.

switch temp var

case "00000001"

pixel = RED;

case "00000010"

pixel = YELLOW;

case "00000100"

pixel = GREEN;

case "00001000"

pixel = BLUE;

case others

pixel = NOTHING;

end switch:

end if:

end switch;

counter ++; // Increment counter

```

Figure 5-4: Colour Lookup

Figure 5-5: Colour Lookup Timing

# **6** Testing and Analysis

## 6.1 Test Image

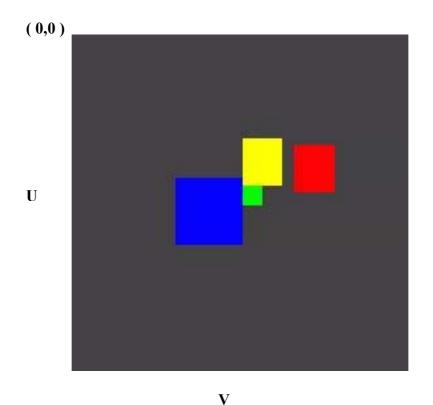

Figure 6-1 shows a RGB test image. Figure 6-2 shows the YUV equivalent.

Figure 6-1: RGB Image

Figure 6-2: YUV image

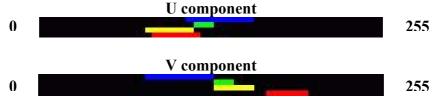

### 6.2 Lookup Table

**Figure 6-3** shows the test Lookup Table used. **Figure 6-4** shows the Bruce's Lookup Table equivalent. The lookup table is not an accurate representation of the real colours i.e. what is blue in the Lookup Table may not be blue in RGB space. The table was created from David Prasser's GurooView program and simplified in Matlab [14]. The orange tube is chosen as the "RED" colour, the yellow book is chosen as the "YELLOW" colour, the green tube is chosen as the "BLUE" colour and green is chosen from a random spot.

Figure 6-3: Normal Lookup Table

Figure 6-4: Bruce's Lookup Table

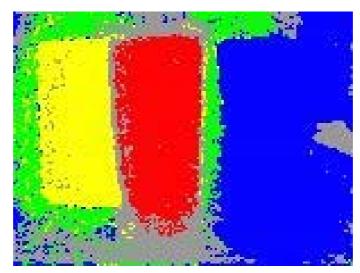

## 6.3 Colour Coded Image

**Figure 6-5** shows the image after the colour lookup. As mentioned earlier, the Lookup Table is not accurate and only serves to test the functionality of the FPGA code. As can be seen from the outputted image, yellow, and red and blue have been accurately identified (remembering the green tube is considered blue).

Figure 6-5: Colour Coded Image

## 6.4 FPGA Resource Usage and Timing

The trimmed Synthesis and Map Reports are located in Appendix C. A summary of the memory usage is outlined in **Figure 6-6**.

| Design Summary                                 |         |        |       |     |

|------------------------------------------------|---------|--------|-------|-----|

|                                                |         |        |       |     |

| Number of errors:                              | 0       |        |       |     |

| Number of warnings:                            | 2       |        |       |     |

| Number of Slices:                              | 183     | out of | 1,200 | 15% |

| Number of Slices containing                    |         |        |       |     |

| unrelated logic:                               | 0       | out of | 183   | 0%  |

| Number of Slice Flip Flops:                    | 124     | out of | 2,400 | 5%  |

| Total Number 4 input LUTs:                     | 292     | out of | 2,400 | 12% |

| Number used as LUTs:                           | 259     |        |       |     |

| Number used as a route-thru:                   | 33      |        |       |     |

| Number of bonded IOBs:                         | 161     | out of | 176   | 91% |

| IOB Flip Flops:                                | 4       |        |       |     |

| Number of Block RAMs:                          | 1       | out of | 10    | 10% |

| Number of GCLKs:                               | 1       | out of | 4     | 25% |

| Total equivalent gate count for design: 19,466 |         |        |       |     |

| Additional JTAG gate count for IC              | DBs: 7, | 728    |       |     |

Figure 6-6: Memory Summary

Figure 6-7 shows the timing summary.

```

Timing Summary:

Speed Grade: -5

Minimum period: 17.686ns (Maximum Frequency: 56.542MHz)

Minimum input arrival time before clock: 5.440ns

Maximum output required time after clock: 12.734ns

Maximum combinational path delay: 13.230ns

```

Figure 6-7: Timing Summary

## 6.5 SH4 Timing

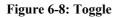

The timing of the SH4 is far slower than the FPGA. The external clock for the FPGA is implemented through the clocking of GIO PIN 10. A toggling function has been implemented to change the state of the pin. **Figure 6-8** shows the function.

```

void toggle_clock(){

if (low){

gio_set_bit_h(GIO_PORTA, GIO_PA10);

low = 0;

}

else{

gio_set_bit_l(GIO_PORTA, GIO_PA10);

low = 1;

}

}

```

The time it takes to execute this function has been measured to be  $\approx 1.3 \mu s$ . This is a very long and the time it takes to transmit a pixel and receive back the colour is  $\approx 1.13 m s$ . **Table 6.1** shows the execution times.

| Function                       | Execution Time |

|--------------------------------|----------------|

| Toggle Clock                   | 1.3µs          |

| Send Pixel                     | 940µs          |

| Get Colour                     | 192µs          |

| Colour Lookup of 150x112 Image | 29.56s         |

Table 6-1: SH4 timing

### 6.5.1 Improving the Timing

The minimum period for the External Clock is 17.68ns. The current period is 2.6µs. The clocks period can be improved by setting the clock high and low manually. The speed that this occurs is 280ns. This is the maximum limit at which the SH4 can toggle a GIO pin. To get faster times, a dedicated clock pin will have to be used (e.g. the BSC clock). **Table 6.2** shows the timing when this new clocking is implemented.

| Function                       | Execution Time |

|--------------------------------|----------------|

| Toggle Clock                   | 280ns          |

| Send Pixel                     | 4.4µs          |

| Get Colour                     | 900ns          |

| Colour Lookup of 150x112 Image | 294ms          |

Table 6-2: New SH4 Timing

Timing can also be improved by changing the storage of the colours. 4 bits can represent up to 16 different colours - which is plenty for the current implementation. Therefore, two pixels can be transferred in one read from the FPGA. This can cut the transfer time in half.

## 6.6 Analysis of Results

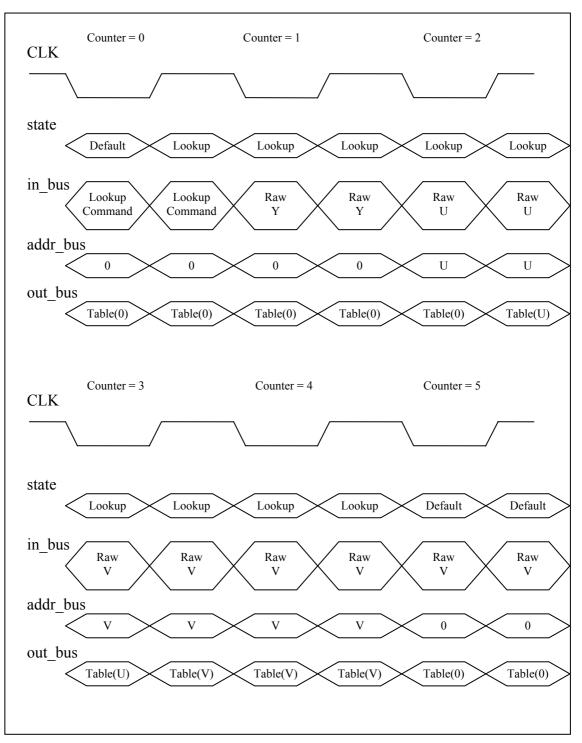

The minimum period for the External Clock is 17.68ns. The SH4 can only currently achieve ten times that speed using a GIO pin. The time it takes to send a pixel to the FPGA from the SH4 is not important. This is because the eventual implementation will have the OV7620 sending the pixel to the FPGA, not the SH4. The execution time that is more important is the time it takes to get the pixel's colour from the FPGA. With current implementation, that time is  $\approx$  900ns.

The OV7620's clock period for 16 bit data is 74ns when the system clock is 27MHz. The time it takes to transmit a pixel in 4:2:2 would be 296ns. In the time it takes to read a colour back from the FPGA (450µs using 4 bit data), approximately 1.5 pixels would have been sent.

The time it takes the OV7620 to transmit a 150x112 image is  $\approx 5$  ms. A 360x270 image (**Table 4-2: Projected Memory Usage**) is  $\approx 28$ ms and a full 640x480 image is  $\approx 90$ ms. The total processing time for David Prasser's code is shown in **Table 6-3** [3].

| Task                         | Time (ms)  |

|------------------------------|------------|

| Colour Detection             | 28         |

| Erosion                      | 22         |

| RLE                          | 49         |

| Grouping                     | Negligible |

| Analysis                     | Negligible |

| Edge Detection and Summation | 25         |

| Edge Analysis                | Negligible |

| Total Time                   | 124ms      |

Table 6-3: Processing Time

Currently, the Colour Detection takes 764ms for a 240x180 image. The bulk of this consists of the SH4 transmitting the image to the FPGA for processing. If it is only retrieving the colour from the FPGA, then it would take approximately 19.44ms – which, as expected, faster than processing the image on the SH4 itself. This proves that even moving the Colour Lookup onto the FPGA would speed up the processing time. The retrieval code is not even optimised because it retrieves 5 types of data: Pixel Colour; Y colour; Lookup data of U; Lookup data of V and the bit AND of U and V.

If the code is optimised a bit more, it is possible to match the pixel rate of the OV7620. The FPGA code will have to be modified first to complete in 4 clock cycles instead of the current implementation of 5. If optimisation of the SH4 code is not enough, then increasing the bus width is another solution. The current bus width is 8 bits due to the constraints on the GIO pins. If a larger bus is used, i.e. the BSC's 32 bit data bus, then it is definitely possible to match the pixel clock. The FPGA can process a pixel faster than the rate at which a pixel is transferred (provided it operates in 4 cycles). A 16 bit bus (4 pixels) is sufficient. If 12 GIO pins can be used as the data bus, then it is possible to match the pixel clock as well.

## 7 Evaluation of Project

It is necessary to evaluate the planning of the project and the decisions that have been made throughout the project. This will provide feedback on whether the assumptions made at the start were correct and valid as well as whether the actions and decisions made throughout the project were correct and justified. The ultimate aim of an evaluation is so future projects do not make the same mistakes.

## 7.1 Evaluation of Project Goals

• Were the Project's Goals achievable?

The initial project goals (Section 3-2) were achievable provided the assumption that the camera was operational and did not require much work to configure was correct. This was not the case.

The project goals made afterwards (**Figure 3-2**) were achievable and have been partly achieved. The Colour Lookup did managed to get moved onto the FPGA and the RLE could be moved as well if there was more time.

## 7.2 Evaluation of Project Schedule

The project schedule is fundamental to the project and if followed, should lead to the completion of the project. This, of course, is provided that it is properly constructed and is reviewed and evaluated regularly.

The initial project schedule (**Figure 3-1**) was correct based on the assumptions made at that time. Unfortunately, the setup of the compiler (scheduled for 1 day) took weeks, which pushed back the rest of the project. However, Ho Wong still thought that the project could be completed in time but this was not the case because the schedule never got past the configuration of the camera.

## 7.3 Evaluation of Risk Management

A risk assessment was done in the Progress Report [9] but; unfortunately, the risks were not adequately defined. A time limit should have been set such that if the camera was not working by that date, then it would be abandoned and the focus would be moved elsewhere.

The risk that the camera was not working did not fully eventuate until all possible actions were tried (e.g. direct wire connection, checking both FPGA and SH4 code for errors and checking PCB). It was very late (August) by the time it was realised that the cameras were not working after all options were exhausted. It was assumed that the problem lay elsewhere because of the initial assumption that Mark Chang had a working camera board.

The assumption made that the configuration of the camera was integral to the start of the other parts of the project was incorrect. It has turned out that a lot can be done on the FPGA itself without the need of a camera.

## 7.4 Recommendations for future improvement

Recommendations for future improvement are:

- Clearly define the risks and actions to be taken in the event they occur.

- Clearly define the time it takes to complete tasks so that the Critical Path methodology can be used. This will provide early warning when things start going wrong so changes to the schedule and even the goals can be made.

- Place milestones in the schedule. These can form part of the risk assessment.

## **8** Future Work

## 8.1 Data transfer between the SH4 and FPGA

The use of the SH4's BSC is advisable. Dual Port RAM will have to be implemented on the FPGA but there are drawbacks.

If Block RAM is not stacked, then only half the available memory is accessible. The best solution is to have a port width of 16 bits. This will allow 4 pixels to be sent in one read. The draw back is only 128 elements can be stored [15]. This equates to 512 pixels. A whole line can be easily stored.

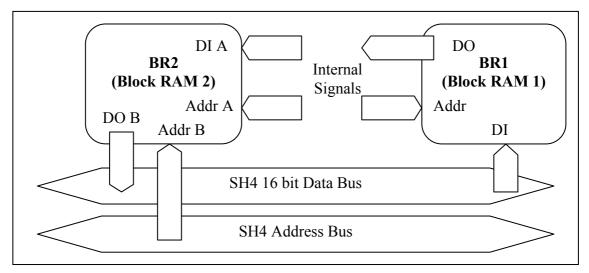

A possible implementation is described by Figure 8-1.

Figure 8-1: Dual Port RAM

BR1 is a Single Port RAM and BR 2 is a Dual Port RAM. The DI of BR1 is from the SH4 (this is how the Lookup Table is stored). The DO of BR1 is used by internal signals to retrieve Lookup Table data. DI A of BR2 comes from internal signals storing pixel colours. DO B of BR2 is the other port that only reads stored data.

## 8.2 Integration with OV7620

The current design on the FPGA is through the use of only a single process. This was because it was easier to understand. The special feature of FPGAs is that a lot of things can run concurrently - unlike normal microprocessors which run sequentially.

The colour lookup can be taken out of the Command Process and made into a separate process with the OV7620's pixel clock (PCLK) as its sensitivity list. A switch will have to be added (similar to the one used to switch output buses) for the address bus and CLK.

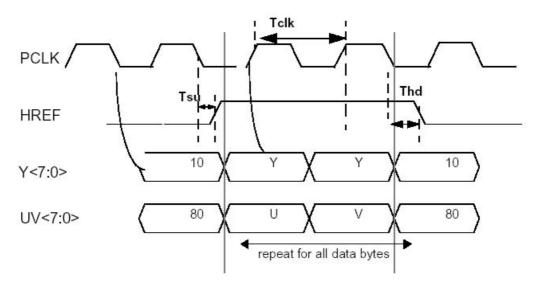

The OV7620 timing diagram is shown in Figure 8-2 [7].

Figure 8-2: OV7620 Timing

Tclk is pixel clock period. When OV7620 system clock is 27MHz, Tclk=74ns for 16 Bit output;Tclk=37ns for 8 Bit output. Tsu is HREF set-up time, maximum is 15 ns; Thd is HREF holdtime, maximum is 15 ns.

The colour lookup process will have to be changed such that it fits inside 4 clock cycles. The comparing of the bit ANDed data can also be made into a separate process because there is no shared signal being written to.

From **Figure 8-2**, the storage of the pixel's data will have to occur on the rising edge of PCLK. The CLK signal to the Block RAM will have to be inverted such that the falling edge of PCLK will trigger the sampling of the inputs and the retrieval of the Lookup Table data.

#### Figure 8-3 shows a pseudo VHDL implementation.

```

-- Lookup process. It is run only when tmp_var changes state. This should happen straight after the

-- Pixel Store process has finished.

Colour Lookup : process (tmp_var)

begin

if conv_integer(unsigned(y_colour)) > INTEN_MAX then

pixel_colour <= WHITE;

elsif conv_integer(unsigned(y_colour)) < INTEN_MIN then

pixel_colour <= BLACK;

else

case temp var is

when "00000001" \Rightarrow pixel colour \leq RED;

when "00000010" => pixel colour <= YELLOW;

when "00000100" => pixel_colour <= GREEN;

when "00001000" => pixel_colour <= BLUE;

when others => pixel colour <= OTHER;

end case;

end if:

end process Colour Lookup;

Pixel Store : process (PCLK)

begin

if counter = 4 then

counter \leq 0;

addr bus \leq 0;

elsif rising_edge (PCLK) then

if counter = 0 then

y colour <= gio in bus; -- Store Y

elsif counter = 1 then

gio addr bus <= '0'& gio in bus; -- Rout U into address bus

elsif counter = 2 then

u_colour <= ram_out_bus; -- Retrieve Lookup Table data

gio_addr_bus <= '0' & gio_in_bus; -- Rout V into address bus

elsif counter = 3 then

v_colour <= ram_out_bus; -- Retrieve Lookup Table data

tmp var <= vectorAnd(u colour,ram out bus); -- BIT AND U & V

else;

end if;

else;

end if;

end process Pixel Store;

```

Figure 8-3: OV7620 Integration

## 8.3 Further Pre-processing

If erosion is ignored, RLE can also be moved onto the FPGA. The constraint; however, will be on the available memory. Each RLE component contains the following data members [3]:

- **begin:** The x coordinate corresponding to the beginning of a run.

- end: The x coordinate of the end of the run.

- y: The y coordinate of the run.

- **colour:** The colour of the pixels in the run.

- tag: The number of the run counting from the top left corner.

- **blob pointer:** A pointer to a blob structure.

In a worse case scenario, every pixel is a RLE element. If this was the case, then the memory required would be:

begin:1byte, end:1byte, y:1byte, colour:4bits, tag: 3bytes blob pointer:2bytes = 12.5bytes. or 13 bytes (98bits) rounded up.

For a 360x270 image, to store a line of RLE's, 4.4Kbytes would be required. It is possible to store this in a single block of RAM but Single Port will have to be used and arbitration will have to be implemented. An easier way is to stack a couple of blocks and use Dual Port. A final alternative is to store it in Distributed RAM, because currently only 15% of the available memory is being used by the FPGA. The bus widths can be manually determined if a Distributed RAM driver is made [16]. It is even possible to make a 32bit Dual Port RAM with Distributed RAM.

"Any sufficiently advanced technology is indistinguishable from magic." - Arthur C. Clarke

## 9 Conclusion

Although the thesis started late due to complications at the start, some progress has been achieved. The problems that occurred early in the year were unavoidable and there were no other actions that could have been taken at that time to resolve them. It is; therefore, simple bad luck that the thesis got off to a slow start.

There was only enough time to move the Colour Lookup onto the FPGA. More could've been accomplished with more time. Details on the future work needed have been documented in this thesis and the next student to work on GuRoo's vision system would be properly informed on the current status and ideas that never got implemented due to the lack of time.

This thesis has managed to improve upon the image processing done by David Prasser's vision software. The time it would take to process a 240x180 image is estimated to be about 19.44ms as opposed to 28ms with David Prasser's code. The pixel clock can be matched by optimising the code on the FPGA or using a larger data bus.

The impact of the results of this thesis is that the processing time for an image can be decreased and hence increase the frame rate. Also, larger images can be used because the raw image is not stored on the SH4.

Future work would have the RLE put onto the FPGA as well. It is not impossible that the image processing can match the rate at which images are sent from the camera. If this is the case, then a high frame rate of 35fps for a 360x270 image can be achieved.

## **Bibliography**

- [1] Damien Kee, GuRoo Electro Mechanical Design, <u>http://www.itee.uq.edu.au/</u> <u>~damien/\_guroo/specification.htm</u>, 23 September 2002, accessed 10 September 2002.

- [2] Robocup2002, Humanoid League 2002 Rule, <u>http://www.robocup.org/</u> <u>regulations/humanoid/rule\_humanoid.htm</u>. 2 September 2002, accessed 10 September 2002.

- [3] David Prasser, *Vision Software for a Humanoid Soccer Robot*, Undergraduate Thesis, University of Queensland, 2001.

- [4] Hitachi Ltd., SH7750 SeriesSH7750, SH7750S Hardware Manual http://www.hitachi-eu.com/hel/ecg/products/micro/32bit/sh\_4.html, Revision 5.0, 19 June 2001,

- [5] Xilinx Inc, Spartan II Product Flyer, <u>http://www.xilinx.com/products/spartan2/</u>

- [6] David Bourgin, *Colour space FAQ*, <u>http://www.neuro.sfc.keio.ac.jp/</u> ~aly/polygon/info/color-space-faq.html, 28 September 1994.

- [7] OmiVision Technologies Inc, *OV7620 Product Specifications* http://www.ovt.com/cc7620.html, Version 2.1 July 10, 2001.

- [8] Andrew Blower, *Development of a Vision System for a Humanoid Robot*, Undergraduate Thesis, University of Queensland 2001.

- [9] Ho Wong, *Vision Hardware for a Humanoid Robot*, Undergraduate Thesis Progress Report, University of Queensland, 2002.

- [10] Ho Wong, *Vision Hardware for a Humanoid Robot*, Undergraduate Thesis Seminar Presentation, University of Queensland, 2002.

- [11] Bruce, Balch, Veloso, *Fast and Inexpensive Colour Segmentation for Interactive Robots*, Proceedings of the 2000 IEEE/RSJ International Conference on Intelligent Robots and Systems, 2000.

- [12] Xilinx Inc, Spartan-II 2.5V FPGA Family: Introduction and OrderingInformation, Xilinx Datasheets,<u>http://www.xilinx.com/partinfo/ds001.htm</u>, v2.3 November 1, 2001.

- [13] Xilinx Inc, Spartan II 2.5V FGPA Family : Functional Description, Xilinx Datasheets, http://www.xilinx.com/partinfo/ds001.htm, v 2.1 March 1, 2001.

- [14] *Image Processing ToolBox 3*, <u>http://www.cat.csiro.au/cmst/staff/pic/vision-tb.html</u>, accessed 18 September 2002.

- [15] Xilinx Inc, Using Block SelectRAM+ Memory in Spartan-II FPGAs, Xilinx Applications, http://www.xilinx.com/apps/sp2app.htm, v1.1 11 December, 2000.

- [16] Xilinx Inc, Implementing Memory, Xilinx Applications, http://toolbox.xilinx.com/docsan/xilinx4/data/docs/sim/fpgahdl10.html, accessed 10 September 2002.

# **Appendix A: Colour Images**

Figure A-1: Spartan II xc2s100 FPGA

Figure A-2: OmniVision OV7620

Figure A-3: Colour as a function of U and V

Figure A-3: Vision Board

# **BAppendix B: Users Manuals**

## **B.1 Software Implementation**

#### **B.1.1 Boot Loader**

The EEPROM holds the boot program for the SH4. Loading of the SH4 is done through Mark Chang's Ploader program. This has to be run under a Unix environment. However; David Prasser has a modified Ploader that runs under Windows.

#### **B.1.2 FPGA**

The FPGA program has to be first converted into a header file first then compiled with the rest of the code – refer to the User's Manual.

#### **B.1.3 Memory**

The SH4 program is stored in P2 and the SRAM is mapped to Area 4 while the 2 SDRAMs are mapped to Areas 2 and 3 respectively. Base RAM address is 0xB0000000. Currently, 4Kbyte of memory is allocated for the main program and the rest is used for storage of images.

#### **B.1.4 GIO Ports**

GIO ports 1 to 8 have not been allocated any special functions. Ports 8 to 11 are used for the camera. Ports 12 to 15 are for each of the four LEDs and ports 16 to 20 are used for the FPGA loading.

### **B.1.5 Interrupts**

There is currently no external interrupt enabled. Only SCI receive and transmit interrupts are currently enabled. Provisions have been made for SCIF interrupts but are currently not being used.

#### **B.1.6 DMAC**

DMA has been set up for the camera's data and also for transmission on SCI. For the camera's data, DMA is activated by an external DMA pin. SCI DMA is activated as part of the on-board peripheral setting.

## **B.2** Users Manual

### **B.2.1 Initial Boot Up**

When the SH4 is powered up initially, all the Voltage Control LEDs (5.0, 3.3, 2.5 & 1.95) should be lit and the SH4 will do a 'LED dance'. When the boot program is finished, LED 3 will be lit. If there other LEDs lit, then there is an error so check all the connections and make sure nothing is shorted together accidentally.

### **B.2.2** Cross-compiler

The SH4 program is compiled using GNU GCC. Refer to Masahiro Abe's manual on building a cross-compiler for the SH4. Mark Chang's compiler is based on Intel architecture. A new cross-compiler will have to be built if the code is to be compiled on a different computer system. E.g. Sun's Spark computers.

#### **B.2.3** Loading of Program

The FPGA bit file has to be converted into a header file first. This header file is then compiled with the rest of the code. Folder /fpga in /viper has the Makefile for it. Copy the binary .rbt file into that directory and run make. This will convert the FPGA program into fpgadata.h. If a new fpga program is not required, do not include fpgadata.h in the main.c.

The makefile in /vbsh4 will compile everything and produce a vbsh4.bin binary file. After compilation, ploader will upload the program into the SH4. Use of ploader is simple. The command is: ploader <COM PORT> <File>. E.g. 'ploader COM1 vbsh4.bin'.

After the program is loaded, the "Heart Beat" should be activated. The "Heart Beat" is the continuous blinking of LED4, hence the term "Heart Beat". This is just the TMU inverting LED4 every time it over-runs.

#### **B.2.4 Downloading of data**

Due to the malfunction of the camera, images have to be directly loaded onto the SH4. This is done through David Prasser's dloader. Three options currently exist for dloader: loading of an image; loading of a lookup table and loading of Bruce's Lookup Table. The file format of all three is '.raw' raw binary file. Usage is simple. The command line is 'dloader <COM PORT> <FILE> <COMMAND>' where COMMAND is either: 'i' for image; 't' for a normal lookup table or 'n' for Bruce's Lookup Table. E.g. 'dloader COM1 image.raw i'.

#### **B.2.5** Uploading of data

Data can be uploaded from the SH4 through David Prasser's uloader. Similar to the dloader images (unprocessed and processed) can be uploaded as well as the lookup tables and blob information. Usage is also similar to dloader. 'uloader <COM PORT> <FILE> <COMMAND>. Where COMMAND is 'i' for image, 's' for processed image, 't' for normal lookup table, 'n' for Bruce's Lookup Table, 'b' for blob information and 'o' for object information. For the images, the output format is '.ppm'(Portable Pixel Map). For the lookup table and colour coded image, the output format is '.pgm'(Portable Gray Map). E.g. 'uloader COM1 processedImage.ppm i'.

#### **B.2.6 Error Codes**

Mark Chang has made error codes for the camera. **Table 10** lists them. The error is identified by the number of pulses of LED2 to LED1. E.g. if LED2 pulses twice for every pulse of LED1, then the error is SCCB CAM.

| Error Type     | No. pulses |

|----------------|------------|

| ERROR_CAM_SCCB | 2          |

| ERROR_CAM_SET  | 3          |

| ERROR_CAM_DMA  | 4          |

| ERROR_CAM      | 5          |

**Table B-1: Camera Error Codes**

# **Appendix C: CODE**

## C.1 FPGA CODE

-- module: vbsh4.vhd

-- Modified by Ho Wong

-- 21/9/02

-- Final Version 14/10/02

-- This is the top level module that ties all sub-modules for vbsh4 together

library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; use IEEE.STD\_LOGIC\_ARITH.ALL; use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

#### entity vbsh4 is

| 5 |                 |                |

|---|-----------------|----------------|

|   | Port (          |                |

|   | CLOCK IN        |                |

|   | PIN_U_CLKOUT :  | in std_logic;  |

|   | PIN_TCLK :      | in std_logic;  |

|   | PIN_I_CLKOUT0 : | in std_logic;  |

|   | PIN_I_CLKOUT1 : | in std_logic;  |

|   |                 |                |

|   | CPU             |                |

|   | PIN_RD :        | in std_logic;  |

|   | PIN_RDWR :      | in std_logic;  |

|   |                 |                |

|   | PIN_BS :        | in std_logic;  |

|   | PIN_RDY :       | in std_logic;  |

|   | PIN_SCK :       | in std_logic;  |

|   | PIN_CS1 :       | in std_logic;  |

|   | PIN_CS2 :       | in std_logic;  |

|   | PIN_WE0 :       | in std_logic;  |

|   | PIN_WE1 :       | in std_logic;  |

|   | PIN_WE2 :       | in std_logic;  |

|   | PIN_WE3 :       | in std_logic;  |

|   |                 |                |

|   | PIN_DRAK0 :     | in std_logic;  |

|   | PIN_DRAK1 :     | in std_logic;  |

|   | PIN_DREQ0 :     | out std_logic; |

|   | PIN_DREQ1 :     | in std_logic;  |

|   |                 |                |

|         | PIN_DACK0 :                      |            | in std_lo              |                                                            |

|---------|----------------------------------|------------|------------------------|------------------------------------------------------------|

|         | PIN_DACK1 :                      |            | in std_lo              | gic;                                                       |

|         | PIN NMI :                        |            | in std_lo              | gic;                                                       |

|         | PIN_IRL0 :                       |            | out std_l              |                                                            |

|         | PIN_IRL1 :                       |            | in std_lo              |                                                            |

|         | PIN_IRL2 :                       |            | in std_lo              |                                                            |

|         | PIN_IRL3 :<br>PIN_MRESET :       |            | in std_lo<br>in std_lo |                                                            |

|         | I IIV_WIKESEI .                  |            | III stu_io             | git,                                                       |

| ADDF    | RESS BUS                         |            |                        |                                                            |

|         | PIN_ADDRBUS :                    | in std_lo  | gic_vecto              | r(18 downto 0);                                            |

| DATA    | DUC                              |            |                        |                                                            |

| DATA    | PIN_DATABUS :                    | inout std  | logic ve               | ctor(31 downto 0).                                         |

|         | Int_Diffibed.                    | inout stu  | _10510_10              |                                                            |

| GENE    | ERAL I/O                         |            |                        |                                                            |

|         | PIN_GIO :                        | inout std  | _logic_ve              | ctor(7 downto 0); My databus.                              |

|         | sech 4                           | wire - 1 c | lock 2 da              | ta, 1 rd/wr                                                |

|         | PIN GIO8 :                       | in std lo  |                        | sccb clock                                                 |

|         | PIN_GIO9 :                       | in std_lo  |                        | sccb data                                                  |

|         | PIN_GIO10:                       | out std_l  |                        |                                                            |

|         | PIN_GIO11 :                      | in std_lo  | gic;                   | secb data direction control                                |

|         | sccb 3 wire - 1 c                | lock 1 da  | ta 1 rd/wi             |                                                            |