## VS1000 Programmer's Guide

VSMPG "VLSI Solution Audio Decoder"

Project Code: Support.VS1000 Project Name: VSMPG

All information in this document is provided as-is without warranty. Features are subject to change without notice.

This is a preliminary version of the document. It may contain mistakes and typing errors. Please contact VLSI if you suspect an error.

| Revision History |            |        |                                               |  |

|------------------|------------|--------|-----------------------------------------------|--|

| Rev.             | Date       | Author | Description                                   |  |

| 0.1              | 2007-03-23 | PKP    | Preliminary version                           |  |

| 0.11             | 2007-04-16 | PKP    | Minor adjustments                             |  |

| 0.12             | 2007-06-28 | PKP    | Additions for version 1.33 of developer tools |  |

## Who needs to read this document

This document describes the programming interface, register map and and integrated peripherals of the VS1000. It's primarily meant for those that wish to add to the functionality of the ROM code in VS1000 or design completely new software for the chip.

#### If you use the USB...

The example "Changing the USB descriptors" should be read by all vendors that have USB functionality in their end-products. Although the ROM software is functional as is, all such vendors should change the USB descriptors to identify the vendor and product ID's correctly.

Additionally, all vendors that ship devices conforming to the USB Mass Storage Class specification should change the USB descriptors and create a unique serial number for each device. Instructions on how to do this are given in the example.

#### VS1000B/C

VS1000B is an updated version of VS1000A, which has many small internal fixes and some additions that remove some of the restricitions in VS1000A. It's mainly compatible with VS1000A, but code needs to be recompiled for VS1000B. This guide is written for VS1000A and does not yet take advantage of the extra features in VS1000B. VS1000C is another production test version of VS1000B. All new code should be written for VS1000B.

# **Table of Contents**

| 1        | Int            | roducing the VS1000                                                 | 5  |

|----------|----------------|---------------------------------------------------------------------|----|

|          | 1.1            | VS_DSP Basics                                                       | 6  |

|          | 1.2            | VS1000 Integrated Peripherals                                       | 7  |

|          | 1.3            | VS1000 Register Map and Frequently Used Tables                      | 8  |

| <b>2</b> | $\mathbf{Sof}$ | tware Tools                                                         | 12 |

| 3        | Exa            | amples                                                              | 14 |

|          | 3.1            | Hello, World!                                                       | 14 |

|          | 3.2            | Making the LEDs blink                                               | 18 |

|          | 3.3            | Adjusting the Player User Interface                                 | 19 |

|          | 3.4            | Hooking custom storage controller                                   | 21 |

|          | 3.5            | Setting your own USB descriptors                                    | 25 |

|          | 3.6            | Booting from SPI EEPROM.                                            | 28 |

|          | 3.7            | Booting from NAND FLASH                                             | 32 |

|          |                | 3.7.1 Nand Flash startup sequence and structure                     | 32 |

|          |                | 3.7.2 Preparing a nand flash image                                  | 33 |

|          |                | 3.7.3 Using the VS1000 Demostration/Developer Board as a nand flash | 00 |

|          |                | writer                                                              | 34 |

|          | 3.8            | Additional examples                                                 | 36 |

|          | 0.0            | 3.8.1 playloop.c                                                    | 36 |

|          |                | 3.8.2 display.c                                                     | 36 |

|          |                | 3.8.3 execdemo1.c and execdemo2.c                                   | 36 |

|          |                | 3.8.4 power.c                                                       | 37 |

|          |                | 3.8.5 nandprog.c                                                    | 37 |

|          | 3.9            | Using an external display                                           | 38 |

|          | 0.0            |                                                                     | 00 |

| <b>4</b> | Per            | ipheral documentation                                               | 39 |

|          | 4.1            | VS1000 System Controller                                            | 39 |

|          |                | 4.1.1 General                                                       | 39 |

|          |                | 4.1.2 Registers                                                     | 39 |

|          |                | 4.1.3 Conserving Power                                              | 41 |

|          |                | 4.1.4 I/O Pin Routing                                               | 42 |

|          |                | 4.1.5 VS1000A ROM code usage                                        | 42 |

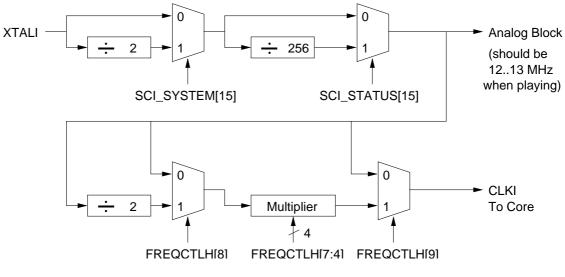

|          | 4.2            | PLL controller v1.0 2006-05-10                                      | 44 |

|          |                | 4.2.1 General                                                       | 44 |

|          |                | 4.2.2 DAC Interpolator control                                      | 44 |

|          |                | 4.2.3 Registers                                                     | 44 |

|          |                | 4.2.4 Overview of VS1000A Clocking                                  | 46 |

|          |                | 4.2.5 VS1000A ROM code usage                                        | 47 |

|          | 4.3            | Interruptable General Purpose IO (VS1000A) v1.0 2002-04-23          | 48 |

|      | 4.3.1   | General                                                        | 48 |

|------|---------|----------------------------------------------------------------|----|

|      | 4.3.2   | Registers                                                      | 48 |

|      | 4.3.3   | VS1000A GPIO Pin Mappings                                      | 51 |

|      | 4.3.4   | VS1000A ROM code usage                                         | 51 |

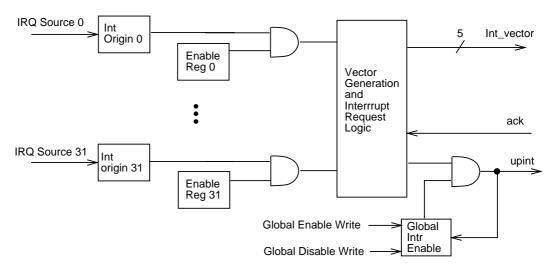

| 4.4  | Interru | ıpt Controller v1.0 2002-04-23                                 | 52 |

|      | 4.4.1   | Registers                                                      | 52 |

|      | 4.4.2   | VS1000A Interrupt Sources                                      | 55 |

|      | 4.4.3   | VS1000A ROM code usage                                         | 55 |

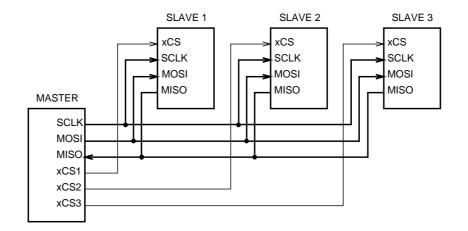

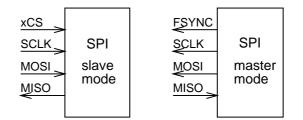

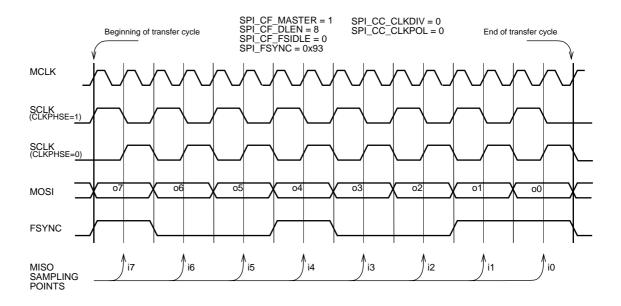

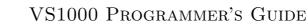

| 4.5  | SPI v1  |                                                                | 56 |

|      | 4.5.1   | General                                                        | 56 |

|      | 4.5.2   | The SPI Block                                                  | 57 |

|      | 4.5.3   | Registers                                                      | 59 |

|      | 4.5.4   | Interrupts                                                     | 62 |

|      | 4.5.5   | Changes from 1.2                                               | 62 |

|      | 4.5.6   | VS1000A ROM code usage                                         | 63 |

|      | 4.5.7   | Effect of Clock Multiplier                                     | 63 |

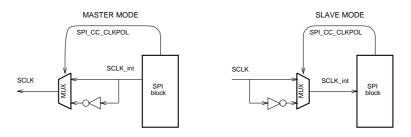

| 4.6  | Byte-w  | vide bus/Nand Flash controller v1.0 2006-05-10                 | 64 |

|      | 4.6.1   | General                                                        | 64 |

|      | 4.6.2   | Block Diagram                                                  | 64 |

|      | 4.6.3   | Registers                                                      | 65 |

|      | 4.6.4   | VS1000A ROM code usage                                         | 68 |

| 4.7  | Timers  | s v1.0 2002-04-23                                              | 69 |

|      | 4.7.1   | General                                                        | 69 |

|      | 4.7.2   | Registers                                                      | 69 |

|      | 4.7.3   | Interrupts                                                     | 70 |

|      | 4.7.4   | VS1000A ROM code usage                                         | 70 |

| 4.8  | UART    | v1.11 2007-03-16                                               | 71 |

|      | 4.8.1   | General                                                        | 71 |

|      | 4.8.2   | Registers                                                      | 71 |

|      | 4.8.3   | Interrupts and Operation                                       | 72 |

|      | 4.8.4   | VS1000A ROM code usage                                         | 73 |

| 4.9  | Univer  | rsal Serial Bus Controller v1.0 2006-01-05                     | 74 |

|      | 4.9.1   | General                                                        | 74 |

|      | 4.9.2   | Registers                                                      | 74 |

|      | 4.9.3   | Receiving Packets from PC (EP0OUT, EP1OUT, $\dots$ , EP3OUT) . | 77 |

|      | 4.9.4   | VS1000A ROM code usage                                         | 80 |

| 4.10 |         | dog v1.0 2002-08-26                                            | 83 |

|      |         | General                                                        | 83 |

|      |         | Registers                                                      | 83 |

|      | 4.10.3  | VS1000A ROM code usage                                         | 83 |

**VLSI**

# 1 Introducing the VS1000

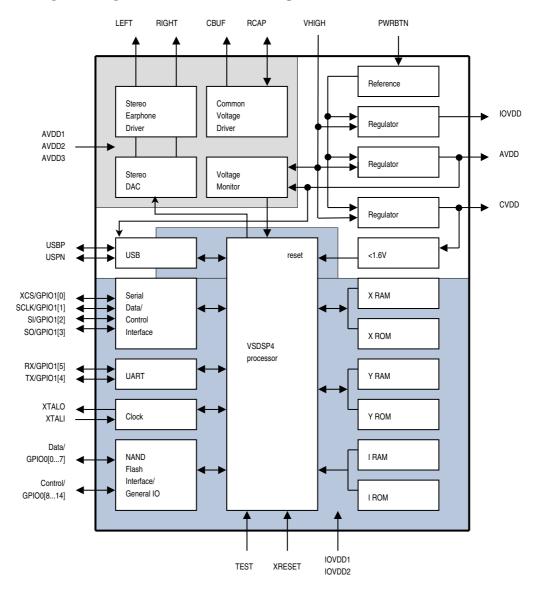

VS1000 is a complete DSP system-on-chip that can be used to implement a multitude of applications such as a single-chip Ogg Vorbis player. VS1000 contains a high-performance low-power DSP core VS\_DSP<sup>4</sup>, NAND-FLASH interface, Full Speed USB port, general purpose I/O pins, SPI, UART, as well as a high-quality variable-sample-rate stereo DAC, and an earphone amplifier and a common voltage buffer.

Figure 1.1: VS1000A Block Diagram

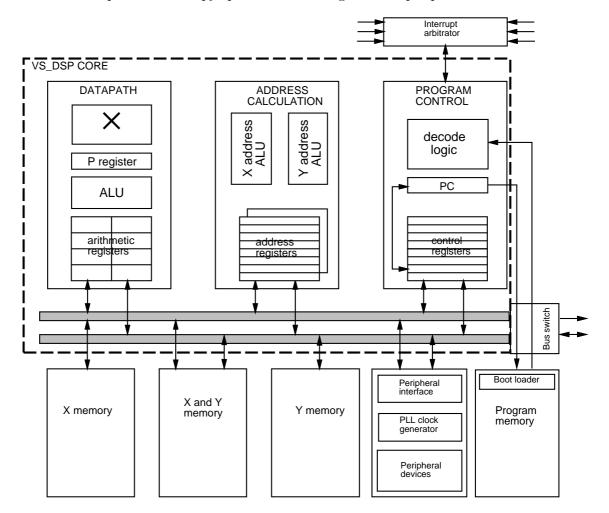

## 1.1 VS\_DSP Basics

At VS1000's core is the VS\_DSP4 signal processor. It has a 16-bit Harward architecture with three separate 16-bit address spaces: X and Y space for data and I space for instructions (running code). All of these spaces have both ROM and RAM. In addition, X and or Y spaces can occupy special function registers for peripheral devices.

Figure 1.2: VS\_DSP General Architecture

Most of the features of the VS\_DSP processor can be accessed by using standard C language, without any specific VS\_DSP knowledge. But if you need to develop really powerful DSP algorithms, use the 40-bit datapath, control the pipeline and take the maximum out of the parallel X, Y and I buses, you need to study the VS\_DSP architecture and use assembly language.

Currently the VS\_DSP4 architecture manual is not freely available from VLSI, but VS\_DSP2 User's Manual is distributed in the VSKIT command line toolset for VS\_DSP2, which is downloadable from the VLSI website (vskit116.zip).

Since VS\_DSP4 is downward compatible with VS\_DSP2 in all other respects except index register postmodification modes 010 and 011 (modulo +2 and modulo -2), which have

different meanings in VS\_DSP4, the VS\_DSP2 User's Manual is the best free resource for learning about the DSP core operation of VS1000.

## 1.2 VS1000 Integrated Peripherals

VS1000 contains several integrated peripherals. They are controlled by memory-mapped special function registers. From the programmer's point of view this means reading and writing special memory locations. The peripheral registers in VS1000 are located in the X address space.

VS1000A chip has the following integrated peripherals:

- 21 GPIO pins multiplexed with peripherals, each capable of generating an interrupt

- SPI port with master/slave operation and programmable Frame Sync

- UART port with programmable bit rate and framing error detection

- USB port with 12 Mbit/s signaling rate and 4 KiB of buffer memory

- Digital-to-Analog converter and integrated earphone driver

- $\bullet\,$  Byte-wide Bus / Nand Flash controller with fast 32-byte buffer and ECC calculation

- 2 32-bit timers with shared master clock divider

- Interrupt controller, 11 interrupt sources

- 3 programmable linear regulators for generating analog, I/O and core voltages

- Internal oscillator for external crystal, can also use external oscillator

- Integrated Clock Generator with PLL and clock multiplier and low-speed modes

- Watchdog timer

The VS1000A has 76 KiB of program ROM and 8 KiB of program RAM. While the latter might seem like a small amount, note that the ROM code contains many useful routines, interfaces and tables the RAM code can access. Many internal functions can be replaced or augmented by hooking a handler vector of a ROM routine.

The amount of data RAM available varies depending on the application. If Vorbis playing is not used, it can be over 50 KiB. For programs that do play Vorbis files, at least 2652 bytes can be used when Vorbis files are playing.

The complete peripheral documentation is in its own chapter.

1. INTRODUCING THE VS1000

## 1.3 VS1000 Register Map and Frequently Used Tables

| VS1000A Peripheral Register Map |                  |                                                |

|---------------------------------|------------------|------------------------------------------------|

| Address                         | Register         | Function                                       |

| 0xC000                          | SCI_SYSTEM       | System Controller control                      |

| 0xC001                          | SCI_STATUS       | System Controller control and status flags     |

| 0xC010                          | GPIO0_MODE       | GPIO(0)/Peripheral(1) function for port 0 pins |

| 0xC011                          | GPIO1_MODE       | GPIO(0)/Peripheral(1) function for port 1 pins |

| 0xC012                          | DAC_VOL          | Digital-to-Analog Converter Volume             |

| 0xC013                          | FREQCTLL         | Interpolator Frequency low part                |

| 0xC014                          | FREQCTLH         | Interpolator Frequency high part               |

| 0xC015                          | DAC_LEFT         | DAC Left Channel                               |

| 0xC016                          | DAC_RIGHT        | DAC Right Channel                              |

| 0xC020                          | WDOG_CONFIG      | Watchdog Config                                |

| 0xC021                          | WDOG_RESET       | Watchdog Reset                                 |

| 0xC022                          | WDOG_DUMMY       | Watchdog dummy register                        |

| 0xC028                          | UART_STATUS      | Serial Port Status                             |

| 0xC029                          | UART_DATA        | Serial Port Data byte                          |

| 0xC02A                          | UART_DATAH       | Serial Port Data byte shifted 8 bits left      |

| 0xC02B                          | UART_DIV         | Serial Port baudrate generator divider         |

| 0xC030                          | TIMER_CONFIG     | Timer 0 and 1 Configuration                    |

| 0xC031                          | TIMER_ENABLE     | Timer 0 and 1 Enable/Disable                   |

| 0xC034                          | TIMER_T0L        | Low 16 bits of Timer 0 reload value            |

| 0xC035                          | TIMER_T0H        | High 16 bits of Timer 0 reload value           |

| 0xC036                          | TIMER_T0CNTL     | Low 16 bits of Timer 0 current value           |

| 0xC037                          | TIMER_T0CNTH     | High 16 bits of Timer 0 current value          |

| 0xC038                          | TIMER_T1L        | Low 16 bits of Timer 1 reload value            |

| 0xC039                          | TIMER_T1H        | High 16 bits of Timer 1 reload value           |

| 0xC03A                          | TIMER_T1CNTL     | Low 16 bits of Timer 1 current value           |

| 0xC03B                          | TIMER_T1CNTH     | High 16 bits of Timer 1 current value          |

| 0xC040                          | GPIO0_DDR        | Port 0 Data Direction ("1"=output)             |

| 0xC041                          | GPIO0_ODATA      | Port 0 Output Data                             |

| 0xC042                          | GPIO0_IDATA      | Port 0 Input Data (pin state)                  |

| 0xC043                          | GPIO0_INT_FALL   | Falling Edge Interrupt Enable                  |

| 0xC044                          | GPIO0_INT_RISE   | Rising Edge Interrupt Enable                   |

| 0xC045                          | GPIO0_INT_PEND   | Interrupt Pending                              |

| 0xC046                          | GPIO0_SET_MASK   | Set output bits high                           |

| 0xC047                          | GPIO0_CLEAR_MASK | Set output bits low                            |

| 0xC048                          | GPIO0_BIT_CONF   | Bit router engine 0 and 1 configuration        |

| 0xC049                          | GPIO0_BIT_ENG0   | Bit router engine 0 data register              |

| 0xC04A                          | GPIO0_BIT_ENG1   | Bit router engine 1 data register              |

VSMPG

PKP

#### 1. INTRODUCING THE VS1000

| VS1000A Peripheral Register Map (continued) |                  |                                                   |  |

|---------------------------------------------|------------------|---------------------------------------------------|--|

| Address                                     | Register         | Function                                          |  |

| 0xC050                                      | GPIO1_DDR        | Port 1 Data Direction ("1"=output)                |  |

| 0xC051                                      | GPIO1_ODATA      | Port 1 Output Data                                |  |

| 0xC052                                      | GPIO1_IDATA      | Port 1 Input Data (pin state)                     |  |

| 0xC053                                      | GPIO1_INT_FALL   | Falling Edge Interrupt Enable                     |  |

| 0xC054                                      | GPIO1_INT_RISE   | Rising Edge Interrupt Enable                      |  |

| 0xC055                                      | GPIO1_INT_PEND   | Interrupt Pending                                 |  |

| 0xC056                                      | GPIO1_SET_MASK   | Set output bits high                              |  |

| 0xC057                                      | GPIO1_CLEAR_MASK | Set output bits low                               |  |

| 0xC058                                      | GPIO1_BIT_CONF   | Bit router engine 0 and 1 configuration           |  |

| 0xC059                                      | GPIO1_BIT_ENG0   | Bit router engine 0 data register                 |  |

| 0xC05A                                      | GPIO1_BIT_ENG1   | Bit router engine 1 data register                 |  |

| 0xC060                                      | NFLSH_CTRL       | Byte-wide Bus (Nand Flash) Controller Control     |  |

| 0xC061                                      | NFLSH_LPL        | Calculated Line Parity for 512-byte block         |  |

| 0xC062                                      | NFLSH_CP_LPH     | Calculated Column Parity for 512-byte block       |  |

| 0xC063                                      | NFLSH_DATA       | Buffer Data read/write register                   |  |

| 0xC064                                      | NFLSH_NFIF       | Buffer-to-Physical Interface Control              |  |

| 0xC065                                      | NFLSH_DSPIF      | Buffer-to-DSP Interface Control                   |  |

| 0xC066                                      | NFLSH_ECC_CNT    | Error Correction Code counter                     |  |

| 0xC068                                      | SPI0_CONFIG      | Serial Peripheral Interface Configuration         |  |

| 0xC069                                      | SPI0_CLKCONFIG   | SPI Clock Configuration                           |  |

| 0xC06A                                      | SPI0_STATUS      | SPI Status                                        |  |

| 0xC06B                                      | SPI0_DATA        | SPI Data read/write register                      |  |

| 0xC06C                                      | SPI0_FSYNC       | Frame Sync output bit image                       |  |

| 0xC070                                      | INT_ENABLEL      | Low Priority Interrupt Enable                     |  |

| 0xC072                                      | INT_ENABLEH      | High Priority Interrupt Enable                    |  |

| 0xC074                                      | INT_ORIGIN       | Interrupt Request Status                          |  |

| 0xC076                                      | INT_VECTOR       | Last generated vector                             |  |

| 0xC077                                      | INT_ENCOUNT      | Interrupt disable level counter                   |  |

| 0xC078                                      | INT_GLOB_DIS     | Disable interrupts (increase ENCOUNT)             |  |

| 0xC079                                      | INT_GLOB_EN      | Enable interrupts (decrease ENCOUNT)              |  |

| 0xC080                                      | USB_CONFIG       | USB Device Config                                 |  |

| 0xC081                                      | USB_CONTROL      | USB Device Control                                |  |

| 0xC081                                      | USB_STATUS       | USB Device Status                                 |  |

| 0xC082                                      | USB_RDPTR        | Receive buffer pointer (PC $\rightarrow$ Device)  |  |

| 0xC083                                      | USB_WRPTR        | Transmit buffer pointer (Device $\rightarrow$ PC) |  |

| 0xC088                                      | USB_EP_SEND0     | EP0IN Transmittable Packet Info                   |  |

| 0xC089                                      | USB_EP_SEND1     | EP1IN Transmittable Packet Info                   |  |

| 0xC08A                                      | USB_EP_SEND2     | EP2IN Transmittable Packet Info                   |  |

| 0xC08B                                      | USB_EP_SEND3     | EP3IN Transmittable Packet Info                   |  |

| 0xC090                                      | USB_EP_ST0       | Flags for endpoints EP0IN and EP0OUT              |  |

| 0xC091                                      | USB_EP_ST1       | Flags for endpoints EP1IN and EP1OUT              |  |

| 0xC092                                      | USB_EP_ST2       | Flags for endpoints EP2IN and EP2OUT              |  |

| 0xC093                                      | USB_EP_ST3       | Flags for endpoints EP3IN and EP3OUT              |  |

### 1. INTRODUCING THE VS1000

| VS1000A Interrupt Sources                              |           |      |                                                    |                                                   |  |

|--------------------------------------------------------|-----------|------|----------------------------------------------------|---------------------------------------------------|--|

| Name                                                   | Name Vect |      | tor                                                | Source                                            |  |

| INTV_DAC                                               | <u>,</u>  | 0    |                                                    | Digital to Analog Converter                       |  |

| INTV_SPI                                               |           | 1    | 1 Serial Peripheral Interface                      |                                                   |  |

| INTV_USB                                               |           | 2    |                                                    | Universal Serial Bus                              |  |

| INTV_NFL                                               | SH        | 3    |                                                    | Byte-wide Bus (Nand Flash) Controller             |  |

| INTV_TX                                                |           | 4    |                                                    | UART Transmit                                     |  |

| INTV_RX                                                |           | 5    |                                                    | UART Receive                                      |  |

| INTV_TIM                                               | 0         | 6    |                                                    | Timer 0 underflow                                 |  |

| INTV_TIM                                               | 1         | 7    |                                                    | Timer 1 underflow                                 |  |

| INTV_REG                                               | ťU        | 8    |                                                    | Input Voltage Monitor                             |  |

| INTV_GPI                                               | 00        | 9    |                                                    | I/O Pin Controller 0                              |  |

| INTV_GPI                                               | 01        | 10   |                                                    | I/O Pin Controller 1                              |  |

|                                                        | ~         | 10.0 |                                                    |                                                   |  |

|                                                        | · · ·     |      |                                                    | ler 0 pins and peripheral functions               |  |

| GPIO                                                   | Ident     | LQFP | Fu                                                 | nction                                            |  |

|                                                        |           | Pin  |                                                    |                                                   |  |

| GPIO0[0]                                               | NFDIO0    | 2    | Nand-flash IO0 / General-purpose IO Port 0, bit 0  |                                                   |  |

| GPIO0[1]                                               | NFDIO1    | 3    |                                                    | nd-flash IO1 / General-purpose IO Port 0, bit 1   |  |

| GPIO0[2]                                               | NFDIO2    | 4    | Nand-flash IO2 / General-purpose IO Port 0, bit 2  |                                                   |  |

| GPIO0[3]                                               | NFDIO3    | 5    | Nand-flash IO3 / General-purpose IO Port 0, bit 3  |                                                   |  |

| GPIO0[4]                                               | NFDIO4    | 9    | Nand-flash IO4 / General-purpose IO Port 0, bit 4  |                                                   |  |

| GPIO0[5]                                               | NFDIO5    | 10   |                                                    |                                                   |  |

| GPIO0[6]                                               | NFDIO6    | 11   |                                                    | nd-flash IO6 / General-purpose IO Port 0, bit 6   |  |

| GPIO0[7]                                               | NFDIO7    | 12   |                                                    | nd-flash IO7 / General-purpose IO Port 0, bit 7   |  |

| GPIO0[8]                                               | NFRDY     | 13   |                                                    | nd-flash READY / General-purpose IO Port $0,$ bit |  |

|                                                        |           |      | 8                                                  |                                                   |  |

| GPIO0[9]                                               | NFRD      | 14   | Nand-flash RD / General-purpose IO Port 0, bit 9   |                                                   |  |

| GPIO0[10]                                              | NFCE      | 15   | Nand-flash CE / General-purpose IO Port 0, bit 10  |                                                   |  |

| GPIO0[11]                                              | NFWR      | 20   | Nand-flash WR / General-purpose IO Port 0, bit 11  |                                                   |  |

| GPIO0[12]                                              | NFCLE     | 16   | Nand-flash CLE / General-purpose IO Port 0, bit 12 |                                                   |  |

| GPIO0[13]                                              | NFALE     | 17   | Nand-flash ALE / General-purpose IO Port 0, bit 13 |                                                   |  |

| GPIO0[14]                                              | CS2       | 21   | Ge                                                 | neral-purpose IO Port 0, bit 14                   |  |

| VS1000A I/O Controller 1 pins and peripheral functions |           |      |                                                    |                                                   |  |

| VS1000A I/O Controller 1 pins and peripheral functions |       |      |                                              |

|--------------------------------------------------------|-------|------|----------------------------------------------|

| GPIO                                                   | Ident | LQFP | Function                                     |

|                                                        |       | Pin  |                                              |

| GPIO1[0]                                               | XCS   | 22   | SPI XCS / General-Purpose I/O Port 1, bit 0  |

| GPIO1[1]                                               | SCLK  | 23   | SPI CLK / General-Purpose I/O Port 1, bit 1  |

| GPIO1[2]                                               | SI    | 24   | SPI MISO / General-Purpose I/O Port 1, bit 2 |

| GPIO1[3]                                               | SO    | 25   | SPI MOSI / General-Purpose I/O Port 1, bit 3 |

| GPIO1[4]                                               | ΤХ    | 26   | UART TX / General-Purpose I/O Port 1, bit 4  |

| GPIO1[5]                                               | RX    | 27   | UART RX / General-Purpose I/O Port 1, bit 5  |

### 1. INTRODUCING THE VS1000

|         | VS1000A Handler Vectors (Services) |                       |                    |  |  |

|---------|------------------------------------|-----------------------|--------------------|--|--|

| Address | Vector Name                        | Default Handler       | Remark             |  |  |

| 0x0000  | IdleHook                           | UserInterfaceIdleHook | CPU idle           |  |  |

| 0x0002  | InitFileSystem                     | FatInitFileSystem     | Init storage       |  |  |

| 0x0004  | OpenFile                           | FatOpenFile           | Open file          |  |  |

| 0x0006  | ReadFile                           | FatReadFile           | Read file          |  |  |

| 0x0008  | Seek                               | FatSeek               | Set file position  |  |  |

| 0x000a  | Tell                               | FatTell               | Get file position  |  |  |

| 0x000c  | ReadDiskSector                     | MapperReadDiskSector  | Read 512 bytes     |  |  |

| 0x000e  | StereoCopy                         | OldStereoCopy         | Output samples     |  |  |

| 0x0015  | Sine Test                          | SinTest               | Sine test          |  |  |

| 0x0016  | Memory Test                        | MemTest               | Memory test 1      |  |  |

| 0x0017  | Memory Test                        | MemTests              | Memory tests       |  |  |

| 0x0018  | SetRate                            | RealSetRate           | Set sample rate    |  |  |

| 0x001a  | PowerOff                           | RealPowerOff          | Close and shutdown |  |  |

| 0x001c  | PlayCurrentFile                    | RealPlayCurrentFile   | Start playing file |  |  |

| 0x001e  | USBHandler                         | RealUSBHandler        | USB Task           |  |  |

|         | VS1000A Handler Vectors (Interrupt Controller) |                             |               |  |  |

|---------|------------------------------------------------|-----------------------------|---------------|--|--|

| Address | Vector Name                                    | Default Handler             | Remark        |  |  |

| 0x0020  | DAC Interrupt                                  | dac_int                     | Update sample |  |  |

| 0x0021  | SPI Interrupt                                  | _int (Default Null Handler) |               |  |  |

| 0x0022  | USB Interrupt                                  | _int (Default Null Handler) |               |  |  |

| 0x0023  | Nand Flash Interrupt                           | _int (Default Null Handler) |               |  |  |

| 0x0024  | TX Interrupt                                   | _int (Default Null Handler) |               |  |  |

| 0x0025  | RX Interrupt                                   | rx_int                      | ROM Monitor   |  |  |

| 0x0026  | Timer 0 Interrupt                              | tim0_int                    | System timer  |  |  |

| 0x0027  | Timer 1 Interrupt                              | _int (Default Null Handler) |               |  |  |

| 0x0028  | Power Interrupt                                | _int (Default Null Handler) |               |  |  |

| 0x0029  | GPIO0 Interrupt                                | _int (Default Null Handler) |               |  |  |

| 0x002a  | GPIO1 Interrupt                                | _int (Default Null Handler) |               |  |  |

| VS1000A Handler Vectors (Services) |                   |                       |                  |  |

|------------------------------------|-------------------|-----------------------|------------------|--|

| Address                            | Vector Name       | Default               | Remark           |  |

| 0x002c                             | MSCPacketFromPC   | RealMSCPacketFromPC   | MSC cmd or data  |  |

| 0x002e                             | DecodeSetupPacket | RealDecodeSetupPacket | Control endpoint |  |

| 0x0030                             | ScsiTaskHandler   | RealScsiTaskHandler   | Disk task        |  |

| 0x0032                             | LoadCheck         | RealLoadCheck         | Clock adjust     |  |

| 0x0034                             | UnsupportedFile   | DefUnsupportedFile    | Unknown format   |  |

# 2 Software Tools

Here is a list of the software tools that are necessary to compile and run the examples of this programming guide. A more complete documentation of the software tools can be found in the "Tools Manual", available from VLSI. These command line tools are available for UNIX and Windows. In addition to these files we recommend using GNU Make to automatize the compilation process, but you can also compile by typing the command lines separately in a shell or "MS-DOS Prompt", or with the help of a suitable batch file. Some GUI's can also be configured to run the compiler and linker as external applications.

The tools package can be requested by writing an email to VLSI Audio Solution Support at the e-mail address mp3@vlsi.fi . Please give basic information of your name, position and if you are working for a company (please give company name and department), or if you are a student (please give name of educational institution) or hobbyist etc.

#### vcc

The VLSI C Compiler. Creates a COFF object file from "C" language source file.

Example: vcc -P130 -O -fsmall-code -I include -o program.o program.c

#### $\mathbf{vslink}$

The linker. Creates a binary program file from multiple COFF object files.

Example: vslink -k -m mem\_user -L lib -lc -o program.bin lib/c-spi.o lib/rom1000a.o program.o

#### vs3emu

The ROM monitor interface. Loads and runs binary program files using RS-232 cable between PC and VS10xx. Also provides standard input/output and file system for debugging C code.

Example: vs3emu -chip vs1000 -s 115200 -l program.bin e.cmd

#### coff2spiboot

Creates bootable EEPROM image from a binary program file.

Example: coff2spiboot -x 0x50 program.bin eeprom.img

#### coff2nandboot

Creates a nand flash compatible boot record file from a binary program file.

Example: coff2nandboot -t 3 -b 8 -s 19 -w 50 -x 0x50 led.bin nand.rec

#### makenandimage

Creates a prommable binary nand flash image from a nand flash compatible boot record file.

Example: makenandimage nand.rec NANDFLSH.IMG

## 3 Examples

## 3.1 Hello, World!

The first example of writing code for the VS1000A is the traditional "Hello, World!" example, which is compiled and linked. Then the RS-232 ROM monitor interface (vs3emu) is used to load and execute the code.

The contents of the file hello.c is:

```

/* hello.c : A Hello World example. */

#include <stdio.h>

// main() is the program entry point. It is entered via a vector,

// which is statically linked to address 0x0050 in module c.o

void main(void) {

puts("Hello, World!");

}

```

### Compiling

The "hello.c" file is compiled using vcc with a command line such as:

vcc -P130 -O -fsmall-code -I include -o hello.o hello.c

This creates a coff object file hello.o. The parameteres that were passed to vcc are:

| -P130        | Treats warning 130 ("can't find prototype") as an error. |

|--------------|----------------------------------------------------------|

| -0           | Optimize                                                 |

| -fsmall-code | Use 16-bit code model (uses libc16 libraries)            |

| -o hello.o   | Output file is hello.o                                   |

| -I include   | subdirectory "include" contains include files            |

| hello.c      | input file                                               |

### Linking

Next the hello.o object is linked using the VS1000 memory map, VS1000A ROM content addresses and the relevant VSDSP run-time libraries using a command such as:

vslink -k -m mem\_user -o hello.bin -L lib -lc lib/c-spi.o lib/rom1000a.o hello.o

This produces a loadable object file hello.bin using the parameters:

| -k             | keep relocation information                                         |

|----------------|---------------------------------------------------------------------|

| -m mem_user    | use memory areas specified in file mem_user                         |

| -o hello.bin   | output file is hello.bin                                            |

| -L lib         | libraries can be found in subdirectory "lib"                        |

| -lc            | use library libc.a (in the -L directory)                            |

| lib/c-spi.o    | the vsemu and SPI boot compatible C startup module (in subdirectory |

|                | lib). It calls main() and returns to ROM code to a point after      |

|                | initializations and SPI boot but before Nand Flash init+boot.       |

| lib/rom1000a.o | address information of the ROM code (in subdirectory lib)           |

| hello.o        | user compiled module                                                |

#### Loading

There are many ways to load runnable code to VS1000A chips. Code can be loaded automatically during boot-up time from an SPI EEPROM or a NAND flash.

During program development it's usually easiest to load the code using an RS-232 ("COM port") emulator interface, which connects to the RX and TX pins of the VS1000.  $^1$

The PC side interface is invoked with:

vs3emu -chip vs1000 -s 115200 -l hello.bin

which instructs the vs3emu interface to use the "vs1000" communication method and default (COM1) port with line speed 115200 bit/s.

The emulator contacts the VS1000 by sending a special character to the COM port. This is handled by the UART receive interrupt on the VS1000. If the VS1000 is running with a 12 MHz crystal, interrupts are enabled and the core is running, it responds with:

```

VSEMU 2.1 (c)1995-2006 VLSI Solution Oy

Clock 11999 kHz

Using serial port 1, Serial input speed seems to be 115200

COM speed 115200

Waiting for a connection to the board...

Caused interrupt

Chip version "1000"

Stack pointer 0x19e0, bpTable 0x7c0f

User program entry address 0x7398

hello.bin: includes optional header, 4 sections, 441 symbols

Section 1: code

page:0 start:80 size:1 relocs:1 fixed

Section 2: const_x

page:1 start:8096 size:14 relocs:0

Section 3: main

page:0 start:81 size:14 relocs:2

Section 4:

VS_stdiolib page:0 start:95 size:50 relocs:13

>

```

<sup>&</sup>lt;sup>1</sup>This is easiest with a VS1000 Developer Board, but even the VS1000 Demonstration Board could be used in this fashion by building a suitable RS-232 interface board. It would require connecting a MAX3232 or equivalent buffer chip to the "RX" and "TX" pads on the Demonstration Board PCB. Power for the MAX3232 could be taken from the JP1 expansion header.

Next the executing address is set to be 0x0050 (statically linked loading vector for main()) by command g 0x50 and executed by command e. On the screen it should look like:

> g 0x50 > e Hello, World!

This final stage can be automated by writing the commands g~0x50 and e to file e.cmd and calling the emulator with the command line

```

vs3emu -chip vs1000 -s 115200 -l hello.bin e.cmd

```

The emulator can be exited by pressing Ctrl-C.

#### Note

If your board has boot code in the Nand Flash, the Nand Flash boot code runs after main() exits.

### Input and Output

This example uses the vs3emu interface to handle C standard I/O (stdin, stdout). With it it's possible to write messages to the user and read input from the PC keyboard. Also it's possible to open, read and write files in the PC. The library contains the elementary functions necessary for input and output. In this example, the library function puts(), which outputs a line of text and a linefeed to stdout, was used.

Since the memory capacity of the chip is limited, the more advanced and memory consuming input/output functions such as printf should not be used. When you need to print out values of variables, it's recommended to use a smaller special function for it. As an example, here is a small function that outputs the value of a 16-bit unsigned integer as a hexadecimal value:

```

#include <stdio.h>

#include <stdio.h>

#include <vstypes.h>

-_y const char hex[] = "0123456789abcdef";

void puthex(u_int16 a) {

char tmp[8];

tmp[0] = hex[(a>>12) & 15]; tmp[1] = hex[(a>>8) & 15];

tmp[2] = hex[(a>>4) & 15]; tmp[3] = hex[(a>>0) & 15];

tmp[4] = ' '; tmp[5] = '\0';

fputs(tmp, stdout);

}

```

Also note that if you use <code>puts</code> (or any file input/output) in your code, a connection with vs3emu is required. You should carefully remove any such code before porting the code to be loaded via another method than vs3emu such as a boot flash or eeprom. This could be done by surrounding the I/O code with <code>#ifdef DEBUG</code> and <code>#endif</code> pre-processor directives.

## 3.2 Making the LEDs blink

The example code below will blink the two LEDs that are connected to VS1000A's SI and SO pins on the Developer Board and the Demonstration Board. Controlling the pins directly requires switching the pin modes from Peripheral control to General Purpose IO control and setting their Output Enable bits to "1".

```

#include <vs1000.h>

/// Busy wait i hundreths of second at 12 MHz clock

auto void BusyWaitHundreths(u_int16 i) {

while(i--){

BusyWait10(); // Rom function, busy loop 10ms at 12MHz

}

}

void main(void) {

PERIP(GPI01_MODE) = 0x30; /* UART=peripheral(1) , SPI=GPI0(0) */

PERIP(GPI01_DDR) = 0x0c; /* SI and SO pins (GPI01[3:2]) are output(1) */

while(1){

PERIP(GPI01_ODATA) = 0x04; /* GPI01[2] (LQFP pin 24) = 1 */

BusyWaitHundreths(50);

PERIP(GPI01_ODATA) = 0x08; /* GPI01[3] (LQFP pin 25) = 1 */

BusyWaitHundreths(50);

}

}

```

The SPI port pins and UART port pins are controlled by the same I/O controller, I/O controller 1. When disabling peripheral control of the SPI pins, the UART pins (RX, TX) must remain under peripheral control. Otherwise, the connection with vs3emu is lost.

| VS1000A I/O Controller 1 pins and peripheral functions |       |      |                                              |  |

|--------------------------------------------------------|-------|------|----------------------------------------------|--|

| GPIO                                                   | Ident | LQFP | Function                                     |  |

|                                                        |       | Pin  |                                              |  |

| GPIO1[0]                                               | XCS   | 22   | SPI XCS / General-Purpose I/O Port 1, bit 0  |  |

| GPIO1[1]                                               | SCLK  | 23   | SPI CLK / General-Purpose I/O Port 1, bit 1  |  |

| GPIO1[2]                                               | SI    | 24   | SPI MISO / General-Purpose I/O Port 1, bit 2 |  |

| GPIO1[3]                                               | SO    | 25   | SPI MOSI / General-Purpose I/O Port 1, bit 3 |  |

| GPIO1[4]                                               | ТХ    | 26   | UART TX / General-Purpose I/O Port 1, bit 4  |  |

| GPIO1[5]                                               | RX    | 27   | UART RX / General-Purpose I/O Port 1, bit 5  |  |

For reference, here are the GPIO1 pin mappings of VS1000A:

PKP

## 3.3 Adjusting the Player User Interface

The ROM code implements a Vorbis player with a default user interface that has 6 buttons:

VS1000 Programmer's Guide

- Power/Play/Pause

- Previous/Rewind

- Next/Fast Forward

- Volume -

- Volume +

- EarSpeaker (spatial processing) setting change

In addition to the 6-button interface the ROM contains alternative default key mappings for a 5-button and 4-button user interfaces.

If these are not sufficient, there are two alternatives:

- Create a custom key  $\rightarrow$  event mapping

- Take full control of the player

The ROM function void KeyEventHandler(enum keyEvent event) can handle 12 predefined player control events:

| VS1000A Pre-defined Player Control Events |                        |                                           |  |  |

|-------------------------------------------|------------------------|-------------------------------------------|--|--|

| Value                                     | Event                  | Function                                  |  |  |

| 0                                         | ke_null                | Do nothing                                |  |  |

| 1                                         | ke_previous            | Play Previous song                        |  |  |

| 2                                         | ke_next                | Play Next song                            |  |  |

| 3                                         | ke_rewind              | Rewind                                    |  |  |

| 4                                         | ke_forward             | Fast Forward                              |  |  |

| 5                                         | ke_volumeUp            | Volume Up                                 |  |  |

| 6                                         | ke_volumeDown          | Volume Down                               |  |  |

| 7                                         | ke_earSpeaker          | Switch EarSpeaker processing (4 settings) |  |  |

| 8                                         | ke_earSpeakerToggle    | Toggle EarSpeaker processing (2 settings) |  |  |

| 9                                         | ke_randomToggle        | Random Play on/off                        |  |  |

| 10                                        | ke_randomToggleNewSong | Play random song                          |  |  |

| 11                                        | ke_pauseToggle         | Pause on/off                              |  |  |

| 12                                        | ke_powerOff,           | Close and power down                      |  |  |

A KeyMapping structure controls the relationship between key-presses, long key-presses and events. The structure is an array of pairs

```

struct KeyMapping {

u_int16 key; // Key Mask

enum keyEvent event; // Event

};

```

The following program demonstrates changing the key mapping:

3. EXAMPLES

```

// Example on how to change the key mapping of the user interface

#include <vs1000.h>

#include <player.h>

// Define key masks for the buttons on the PCB. This order is

// of the Demonstration Board, leftmost button is "KEY_A"

#define KEY_A 0x0004

#define KEY_B 0x0008

#define KEY_C 0x0001

#define KEY_D 0x0002

#define KEY_E 0x0010

// Define custom key mapping

const struct KeyMapping myKeyMap[] = {

ke_volumeUp }, // Key A: Volume step up

\{KEY_A,

{KEY_A | KEY_LONG_PRESS,

ke_volumeUp }, // Key A: Volume up continuous

\{KEY_B,

ke_volumeDown}, // Key B: Volume step dn

{KEY_B | KEY_LONG_PRESS,

ke_volumeDown}, // Key B: Volume dn continuous

\{KEY_C,

ke_previous }, // Key C: Previous song

}, // Key D: Next song

{KEY_D,

ke_next

{KEY_E | KEY_A | KEY_LONG_PRESS,

ke_rewind

}, // Key E with Key A: rewind

ke_forward

{KEY_E | KEY_B | KEY_LONG_PRESS,

}, // Key E with Key B: fast forward

KEY_C | KEY_D | KEY_LONG_ONESHOT, ke_powerOff }, // Only one event after long press

{0, ke_null} // End of key mappings

};

// Load own key mapping

void main(){

currentKeyMap = myKeyMap; // Use own key mapping

// Note that if there is boot record in NAND, it's run after

// this point, if this code is run from the emulator

}

```

VS1000 Programmer's Guide

The KeyEventHandler can also be called directly. For instance if you wish to advance to the next song, you can call

```

KeyEventHandler(ke_next);

```

from your source code. In most cases it takes less code space than changing the **struct player** directly.

The tools package contains further examples on how to adjust the user interface, use the embedded LCD font etc.

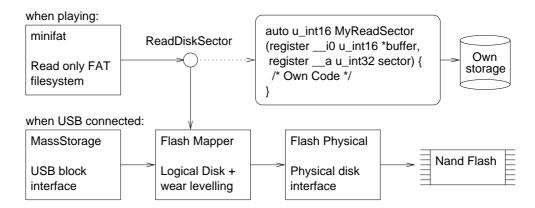

## 3.4 Hooking custom storage controller

Hooks are software jump vectors, that are linked into fixed positions in the VS1000A RAM. Their function is essentially the same as for instance the interrupt vector of a 80x86 processor. For instance, when the player is playing music, it reads a disk sector (512 bytes) of data by calling a function ReadDiskSector(u\_int16 \*buffer, u\_int32 sector). For this call, the linker generates a call to a fixed address 0x000c. In that address (which is in RAM) is a jump instruction to the start address of the ROM function RealReadDiskSector(), which retrieves the data from a logical NAND Flash mapper interface.

By replacing the jump location of the ReadDiskSector() hook vector, it is easy to replace the storage device, which contains the files the player plays. Only the service that delivers a sectorful of data from a storage device is changed while rest of the ROM functionality remains the same.

The image below demonstrates the disk data flow of VS1000:

Figure 3.1: Disk Data Flow

Below is an example of hookable disk read function that uses a previously declared EEReadBlock() function to read 512 bytes to **\*buffer** and returns 0 signifying no error:

This can then be hooked to the ReadDiskSector hook by calling SetHookFunction((u\_int16)ReadDiskSector, MyReadDiskSector); in main() or some other convenient function.

The above method is most convenient for preprogrammed storage devices. If you need write access to your own storage device, you need to write control code for it yourself, e.g. for downloading a disk image over a serial port etc.

#### ReadDiskSector is for reading only

As the name suggests, the ReadDiskSector() hook is meant only for reading data. This limits its usage to the "player" mode only (when the VS1000A is in player mode, it does not write to the logical disk).

If you want to attach your own device to the USB bus as a mass storage device, you need to write a mapper interface that has functions for reading and writing+erasing 512-byte sectors. Then you need to write a function that publishes the interface with name map, initializes the USB handler (probably by calling InitUSB(USB\_MASS\_STORAGE)) and then calls UsbHandler() in a busy loop until the USB is detached.

The complete example code is below. It uses 253 words of program RAM out of the 1968 words available for plugins.

VS1000 Programmer's Guide

PKP

```

// storage.c : Plug-in for playing from intel "S33" serial flash eeprom.

// For this example, a QH25F640S33B8 chip is connected to SI, SO, SCLK, XCS.

#include <stdlib.h>

#include <vs1000.h>

#define SPI_EEPROM_COMMAND_READ_STATUS_REGISTER 0x05

#define SPI_EEPROM_COMMAND_READ 0x03

//macro to set SPI to MASTER; 8BIT; FSYNC Idle => xCS high

#define SPI_MASTER_8BIT_CSHI

PERIP(SPIO_CONFIG) = \setminus

SPI_CF_MASTER | SPI_CF_DLEN8 | SPI_CF_FSIDLE1

//macro to set SPI to MASTER; 8BIT; FSYNC not Idle => xCS low

#define SPI_MASTER_8BIT_CSL0 PERIP(SPI0_CONFIG) = \

SPI_CF_MASTER | SPI_CF_DLEN8 | SPI_CF_FSIDLE0

//macro to set SPI to MASTER; 16BIT; FSYNC not Idle => xCS low

#define SPI_MASTER_16BIT_CSL0 PERIP(SPI0_CONFIG) = \

SPI_CF_MASTER | SPI_CF_DLEN16 | SPI_CF_FSIDLE0

void InitSpi() {

SPI_MASTER_8BIT_CSHI;

PERIP(SPI0_FSYNC) = 0; // Frame Sync is used as an active low xCS

PERIP(SPI0_CLKCONFIG) = SPI_CC_CLKDIV * (1-1); // Spi clock divider = 1

PERIP(GPI01_MODE) |= 0x1f; // Set SPI pins to be peripheral controlled

}

void EESingleCycleCommand(u_int16 cmd){

SPI_MASTER_8BIT_CSHI;

SPI_MASTER_8BIT_CSLO;

SpiSendReceive(cmd);

SPI_MASTER_8BIT_CSHI;

}

/// Wait for not_busy (status[0] = 0) and return status

u_int16 EEWaitGetStatus(void) {

u_int16 status;

SPI_MASTER_8BIT_CSHI;

SPI_MASTER_8BIT_CSLO;

SpiSendReceive(SPI_EEPROM_COMMAND_READ_STATUS_REGISTER);

while ((status = SpiSendReceive(0)) & 0x01)

; //Wait until ready

SPI_MASTER_8BIT_CSHI;

return status;

}

```

3. EXAMPLES

```

/// Read a block from EEPROM

/// \param blockn number of 512-byte sector 0..32767

/// \param dptr pointer to data block

u_int16 EEReadBlock(u_int16 blockn, u_int16 *dptr) {

EEWaitGetStatus();

// Wait until EEPROM is not busy

SPI_MASTER_8BIT_CSLO;

// Bring xCS low

SpiSendReceive(SPI_EEPROM_COMMAND_READ);

SpiSendReceive(blockn>>7);

// Address[23:16] = blockn[14:7]

SpiSendReceive((blockn<<1)&0xff);</td>

// Address[15:8] = blockn[6:0]0

SpiSendReceive(0);

// Address[7:0] = 00000000

SPI_MASTER_16BIT_CSLO;

// Switch to 16-bit mode

{ int n;

for (n=0; n<256; n++){

*dptr++ = SpiSendReceive(0); // Receive Data

}

SPI_MASTER_8BIT_CSHI;

// Bring xCS back to high

return 0;

}

// Disk image is prommed to EEPROM at sector 0x80 onwards, leaving

// the first 64 kilobytes (1 erasable block) free for boot code

#define FAT_START_SECTOR 0x80

// This function will replace ReadDiskSector() functionality

auto u_int16 MyReadDiskSector(register __i0 u_int16 *buffer,

register __a u_int32 sector) {

PERIP(GPI01_MODE) |= 0x1f;

// Set SPI pins to be peripheral controlled

EEReadBlock(sector+FAT_START_SECTOR, buffer);

return 0;

}

// Initialize SPI and hook in own disk read function.

// This example plays ogg files from a FAT image that has been

// previously written to a serial EEPROM.

void main(void) {

InitSpi();

// Hook in own disk sector read function

SetHookFunction((u_int16)ReadDiskSector, MyReadDiskSector);

} // Return to ROM code. Player will now play from EEPROM

```

VS1000 Programmer's Guide

## 3.5 Setting your own USB descriptors

Each USB device has a Vendor ID and a Product ID, which are 16-bit numbers that the operating system uses for determining which device driver to load for the device. Additionally most USB devices have a vendor name and model name strings that the operating system can display to the user. All USB string descriptors are 16-bit Unicode strings (UTF-16).

VS1000 Programmer's Guide

VS1000A's ROM code holds VLSI's Vendor ID and Product ID. For prototyping you can use an unused Vendor ID and Product ID, but when you ship products to customers, you must use your own Vendor ID and Product ID. A Vendor ID can be obtained from the USB Implementers Forum, Inc.'s web site, http://www.usb.org.

To comply with USB Mass Storage Specification, each device that is shipped out to customers should have a unique serial number in the USB descriptors. Windows uses this serial number e.g. for storing device parameters in the system registry.

VS1000A's ROM is written so that it's easy to change these descriptors without having to touch the rest of the USB code. This example shows how you can change the Device Descriptor, which holds the Vendor ID and Product ID, and the Vendor/Model/SerialNumber string descriptors.

USB.descriptorTable[6] holds pointers to the descriptors. They are overwritten by the ROM code in various locations, but a system hook vector called DecodeSetupPacket can be used to set pointers to your own descriptors each time a SETUP packet is received from the PC. This way you can be sure that VS1000A always responds with the updated descriptors.

### Descriptor data format

Mostly because the USB has its roots in the 8-bit oriented PC (80x86) architecture, all USB traffic is transmitted byte by byte. When values that have more than 8 bits, such as 16-bit integers or 32-bit integers, are transmitted, they are transmitted in the little-endian ("Little End First") format, where the least significant (last) byte of a multi-byte value is sent first.

VS\_DSP, however, is a natively 16-bit architecture that only handles 16-bit values. Thus all data in VS\_DSP must be stored as signed or unsigned 16 (or 32) bit values. To maintain USB compatibility, care must be taken to transmit descriptors in the correct byte order. In practice this means that descriptors should be stored in tables of byte-swapped 16-bit unsigned integers as in the example below.

The serial number is a string of (at least) 12 characters from set {"0123456789ABCDEF"}. All strings are stored in 16-bit Unicode format. The example code creates a new serial number string descriptor mySerialNumberStr. The last 8 characters are generated in the main() function from u\_int32 mySerialNumber, which should be unique for each device. You could generate it from e.g. the serial number of the storage memory your product has. The first 4 characters ("1234" in the descriptor) could be fixed for a specific program version etc.

```

// usbdesc.c : Example for changing USB descriptors

// We will hook DecodeSetupPacket so that it sets our string descriptors

// each time a Setup packet (USB device/class request) is sent.

#include <vs1000.h>

#include <usb.h>

#define VENDOR_NAME_LENGTH 6

const u_int16 myVendorNameStr[] = {

((VENDOR_NAME_LENGTH * 2 + 2) << 8) | 0x03,

'M' << 8,

'y' << 8,

,C, << 8,

'o' << 8,

'r' << 8,

'p' << 8

};

#define MODEL_NAME_LENGTH 6

const u_int16 myModelNameStr[] = {

((MODEL_NAME_LENGTH * 2 + 2) << 8) | 0x03,

'G' << 8,

'a' << 8,

'd' << 8,

'g' << 8,

'e' << 8,

't' << 8

};

#define SERIAL_NUMBER_LENGTH 12

u_int16 mySerialNumberStr[] = {

((SERIAL_NUMBER_LENGTH * 2 + 2) << 8) | 0x03,

'1' << 8, // You can

'2' << 8, // put any

'3' << 8, // numbers you

'4' << 8, // like here (over the '1' '2' '3' and '4')

0x3000, 0x3000, 0x3000, 0x3000, // Last 8 digits of serial

0x3000, 0x3000, 0x3000, 0x3000 // number will be calculated here

};

// This is the new Device Descriptor. See the USB specification!

// Note that since VS_DSP is 16-bit Big-Endian processor,

// tables MUST be given as byte-swapped 16-bit tables for USB compatibility!

// This device descriptor template is ok for mass storage devices.

const u_int16 myDeviceDescriptor [] = {

0x1201, 0x1001, 0x0000, 0x0040,

0x3412, // byte-swapped Vendor ID (0x1234) Get own from usb.org!

// byte-swapped Product ID (0x2345)

0x4523,

0x5634,

// byte-swapped Device ID (0x3456)

0x0102, 0x0301

};

```

VS1000 Programmer's Guide

```

// When a USB setup packet is received, install our descriptors

// and then proceed to the ROM function \ensuremath{\mathsf{RealDecodeSetupPacket}}.

void MyDecodeSetupPacket(void){

USB.descriptorTable[DT_VENDOR] = myVendorNameStr;

USB.descriptorTable[DT_MODEL] = myModelNameStr;

USB.descriptorTable[DT_SERIAL] = mySerialNumberStr;

USB.descriptorTable[DT_DEVICE] = myDeviceDescriptor;

RealDecodeSetupPacket();

}

const u_int16 bHexChar16[] = { // swapped Unicode hex characters

0x3000, 0x3100, 0x3200, 0x3300, 0x3400, 0x3500, 0x3600, 0x3700,

0x3800, 0x3900, 0x4100, 0x4200, 0x4300, 0x4400, 0x4400, 0x4500

};

void main(void) {

u_int16 i;

u_int32 mySerialNumber = 0x1234abcd; // Unique serial number

// Put unique serial number to serial number descriptor

for (i=5; i<13; i++){

mySerialNumberStr[i]=bHexChar16[mySerialNumber>>28];

mySerialNumber <<= 4;</pre>

}

// Hook in function that will load new descriptors to USB struct

```

VS1000 Programmer's Guide

```

SetHookFunction((u_int16)DecodeSetupPacket, MyDecodeSetupPacket);

```

```

} // Return to ROM code.

```

## 3.6 Booting from SPI EEPROM

VS1000A supports loading boot-up code from an SPI EEPROM such as the 25LC640. The ROM code checks the state of XCS pin during boot-up. If XCS is high, the code attempts to read a boot record from the EEPROM using the SI, SO, SCLK and XCS pins. In addition to the 16-bit addressing of SPI eeproms such as the 25LC640, the ROM also supports 24-bit addressing of some larger EEPROMS (possibly up to 16 megabytes).

A program that is to be loaded using the SPI EEPROM must be linked with c-spi.o object module. The c-spi.o module can also be used with running the code from vs3emu, but not from the nand flash.

The **coff2spiboot** tool can be used to create a bootable EEPROM image from the linker output file with a command such as:

coff2spiboot -x 0x50 led.bin eeprom.img

This reads the previously compiled program led.bin and creates a binary eeprom image eeprom.img, which can be programmed to an SPI EEPROM with an EEPROM programmer.

A valid boot record starts with identifier 0x564C5349 ('V','L','S','I') and contains blocks of binary data that are to be stored at specified addresses. A boot record that is loaded via the SPI bus must have an execution command as the last block. Description of the block format is in the datasheet, if it should be needed for some special purpose.

#### Using a VS1000 Developer Board as an eeprommer

Also a VS1000 Developer Board can be used to program the SPI EEPROM, using the vs3emu file interface. The next pages contain an example program that reads the **eeprom.img** file and writes it to a 25LC640 EEPROM. The promming routine is compiled normally to a binary program **prommer.bin**. It can be run with vs3emu with a command such as:

vs3emu -chip vs1000 -s 115200 -l prommer.bin e.cmd

If the file eeprom.img is found on the local directory, the contents is programmed to the EEPROM and you should see output such as

```

25LC640 EEPROM promming routine for VS1000A

Trying to open eeprom.img

Programming...

Sector 0000 ...

Reading first 2 words of EEPROM: 564c 5349 ("VLSI"), which is a valid VLSI boot

id.

Done.

```

```

// VS1000A EEPROM Writer Program

// Reads eeprom.img file from PC via vs3emu cable and programs it to EEPROM.

#define MY_IDENT "25LC640 EEPROM promming routine for VS1000A"

#include <stdio.h>

#include <stdlib.h>

#include <vs1000.h>

#include <minifat.h>

__y const char hex[] = "0123456789abcdef";

void puthex(u_int16 a) {

char tmp[8];

tmp[0] = hex[(a>>12)&15]; tmp[1] = hex[(a>>8)&15];

tmp[2] = hex[(a>>4)&15]; tmp[3] = hex[(a>>0)&15];

tmp[4] = ' ';

tmp[5] = ' \ 0';

fputs(tmp, stdout);

}

#define SPI_EEPROM_COMMAND_WRITE_ENABLE 0x06

#define SPI_EEPROM_COMMAND_WRITE_DISABLE 0x04

#define SPI_EEPROM_COMMAND_READ_STATUS_REGISTER 0x05

#define SPI_EEPROM_COMMAND_WRITE_STATUS_REGISTER 0x01

#define SPI_EEPROM_COMMAND_READ 0x03

#define SPI_EEPROM_COMMAND_WRITE 0x02

//macro to set SPI to MASTER; 8BIT; FSYNC Idle => xCS high

#define SPI_MASTER_8BIT_CSHI PERIP(SPI0_CONFIG) = \

SPI_CF_MASTER | SPI_CF_DLEN8 | SPI_CF_FSIDLE1

//macro to set SPI to MASTER; 8BIT; FSYNC not Idle => xCS low

#define SPI_MASTER_8BIT_CSL0 PERIP(SPI0_CONFIG) = \

SPI_CF_MASTER | SPI_CF_DLEN8 | SPI_CF_FSIDLE0

//macro to set SPI to MASTER; 16BIT; FSYNC not Idle => xCS low

#define SPI_MASTER_16BIT_CSL0 PERIP(SPI0_CONFIG) = \

SPI_CF_MASTER | SPI_CF_DLEN16 | SPI_CF_FSIDLE0

void SingleCycleCommand(u_int16 cmd){

SPI_MASTER_8BIT_CSHI;

SpiDelay(0);

SPI_MASTER_8BIT_CSLO;

SpiSendReceive(cmd);

SPI_MASTER_8BIT_CSHI;

SpiDelay(0);

}

/// Wait for not_busy (status[0] = 0) and return status

u_int16 SpiWaitStatus(void) {

u_int16 status;

SPI_MASTER_8BIT_CSHI;

SpiDelay(0);

SPI_MASTER_8BIT_CSLO;

```

VS1000 Programmer's Guide

VS1000 Programmer's Guide

3. EXAMPLES

```

SpiSendReceive(SPI_EEPROM_COMMAND_READ_STATUS_REGISTER);

while ((status = SpiSendReceive(0xff)) & 0x01){

SpiDelay(0);

SPI_MASTER_8BIT_CSHI;

return status;

}

void SpiWriteBlock(u_int16 blockn, u_int16 *dptr) {

u_int16 i;

u_int16 addr = blockn*512;

for (i=0; i<32; i++){

SingleCycleCommand(SPI_EEPROM_COMMAND_WRITE_ENABLE);

SPI_MASTER_8BIT_CSLO;

SpiSendReceive(SPI_EEPROM_COMMAND_WRITE);

SPI_MASTER_16BIT_CSLO;

SpiSendReceive(addr);

{

u_int16 j;

for (j=0; j<16; j++){ //Write 16 words (32 bytes)

SpiSendReceive(*dptr++);

}

SPI_MASTER_8BIT_CSHI;

SpiWaitStatus();

addr+=32;

}

}

u_int16 SpiReadBlock(u_int16 blockn, u_int16 *dptr) {

SpiWaitStatus();

SPI_MASTER_8BIT_CSLO;

SpiSendReceive(SPI_EEPROM_COMMAND_READ);

SpiSendReceive((blockn<<1)&0xff); // Address[15:8] = blockn[6:0]0</pre>

SpiSendReceive(0);

// Address[7:0]

= 00000000

SPI_MASTER_16BIT_CSLO;

ł

u_int16 i;

for (i=0; i<256; i++){

*dptr++ = SpiSendReceive(0);

}

}

SPI_MASTER_8BIT_CSHI;

return 0;

}

// This routine programs the EEPROM.

// The minifat module has a memory buffer of 512 bytes (minifatBuffer)

// that is used here as temporary memory.

/\!/ The routine does not verify the data that is written, but after

// programming, the eeprom start is checked for a VLSI boot id.

```

```

PKP

```

3. EXAMPLES

```

void main(void) {

FILE *fp;

SPI_MASTER_8BIT_CSHI;

PERIP(SPIO_FSYNC) = 0;

PERIP(SPI0_CLKCONFIG) = SPI_CC_CLKDIV * (12-1);

PERIP(GPI01_MODE) |= 0x1f; /* enable SPI pins */

PERIP(INT_ENABLEL) &= ~INTF_RX; //Disable UART RX interrupt

puts("");

puts(MY_IDENT);

puts("Trying to open eeprom.img");

if (fp = fopen ("eeprom.img", "rb")){ // Open a file in the PC

u_int16 len;

u_int16 sectorNumber=0;

puts("Programming...");

while ((len=fread(minifatBuffer,1,256,fp))){

fputs("Sector ",stdout); puthex(sectorNumber); puts("...");

SpiWriteBlock(sectorNumber, minifatBuffer);

sectorNumber++;

fclose(fp); // Programming complete.

minifatBuffer[0]=0;

fputs("Reading first 2 words of EEPROM: ",stdout);

SpiReadBlock(0,minifatBuffer);

puthex(minifatBuffer[0]);

puthex(minifatBuffer[1]);

fputs(" (\"",stdout);

putchar(minifatBuffer[0]>>8); putchar(minifatBuffer[0]&0xff);

putchar(minifatBuffer[1]>>8); putchar(minifatBuffer[1]&0xff);

if ((minifatBuffer[0]==0x564c) && (minifatBuffer[1]==0x5349)){

puts("\"), which is a valid VLSI boot id.");

} else {

puts("\"), which is NOT a valid VLSI boot id!");

puts("Done.");

}else{

puts("File not found\n");

}

PERIP(INT_ENABLEL) |= INTF_RX; //Re-enable UART RX interrupt

while(1)

; //Stop here

J

```

VS1000 Programmer's Guide

## 3.7 Booting from NAND FLASH

If a nand flash chip is connected to the byte-wide bus interface of VS1000, it can also be used for booting the VS1000. VS1000A supports natively most single-level cell, single-chip-select NAND flashes such as the NAND128W3A2 from ST (small page) or K9F2G08U0M from Samsung (large page).

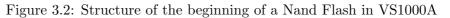

### 3.7.1 Nand Flash startup sequence and structure

The nand flash boot is attempted after EEPROM boot. First the I/O voltages are set according to the input state of GPIO0[7] pin. Then VS1000A attempts to read the first block of 512 bytes of the nand flash with 8 different access methods, using the nand flash interface with only CS1 chip select. The access methods cover small and large page flashes with 4, 5 or 6 address bytes.

Because different types of nand flash chips differ in the access methodology, using a nand flash is somewhat more complicated than using an eeprom. To ensure proper operation, a nand flash chip must be programmed with a valid VLSI ID record in the beginning of block 0. VS1000A looks for the ID record and adjusts the nand access parameters according to the ID record information.

If the VLSI boot id 'V"L"S"I' (0x564C5349) is successfully read in the beginning of block 0, the ID record is considered valid. The next words of the ID record specify the overall size, erasable block size, number of address bytes, block size and speed grade of the nand flash chip in question in the format specified in the VS1000 datasheet.

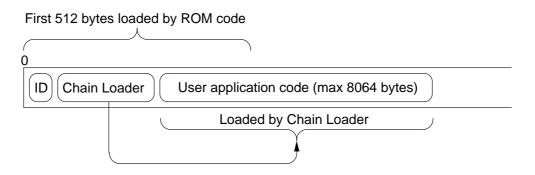

The rest of the 512-byte block can be programmed with additional boot code. It can contain a small patch code that fits in the sector itself, or a chain loader for loading a larger user program.

The first erasable area of a nand flash chip is reserved for boot data. The filesystem that contains the songs to be played and is visible to the PC as a USB disk starts at a further offset after the boot area and for security reasons is separate from the boot area.

### 3.7.2 Preparing a nand flash image

A program that is to be loaded using the nand flash must be linked with c-nand.o with a command line such as:

```

vslink -k -m mem_user -o led.bin -L lib -lc lib/c-nand.o lib/rom1000a.o led.o

```

The binary program led.bin must then be converted into a nand boot record using the coff2nandboot program with a command line such as:

coff2nandboot -t 3 -b 8 -s 19 -w 50 -x 0x50 led.bin nand.rec

The program coff2nandboot creates a nand boot record starting with a VLSI ID record. The parameters -t 3 -b 8 -s 19 -w 50 specify that the target nand flash chip used

- is of Type 3 (Large Page, 5-byte address)

- has an erasable block size of  $2^8 \times 512$  bytes (128 KiB)

- has an overall size of  $2^{19} \times 512$  bytes (256 MiB)

- needs 50 ns wait states

The parameters -x 0x50 led.bin nand.rec instruct that

- executable code starts at address 0x0050

- linked program image is in led.bin

- boot record should be written to nand.rec

```

Output such as the following can be expected from coff2nandboot:

NandType: 3 Large-Page 5-byte addr, 128kB blocks, 256MB flash

I: 0x0050-0x0086 In: 222, out: 222

In: 222, out: 228

```

The above parameters are ok for the K9F2G08, which is installed in some of the Demonstration Boards shipped by VLSI. Others have NAND128W and for those a suitable command line is coff2nandboot  $-t \ 0 \ -b \ 5 \ -s \ 15 \ -x \ 0x50 \ led.bin nand.rec$

There is one final step before a programmable nand flash image is obtained: the tool makenandimage inserts a VS1000A compatible chain loader to nand.rec and outputs a binary boot image nand.img.

makenandimage nand.rec NANDFLSH.IMG

makenandimage: inserting chain loader for 'nand.rec'.

The resulting binary file NANDFLSH. IMG can be prommed to the beginning of a nand flash with a nand flash programmer.

# 3.7.3 Using the VS1000 Demostration/Developer Board as a nand flash writer

VS1000 Programmer's Guide

Because it would be troublesome to remove a nand flash chip that is soldered to a PCB for programming, the VS1000 contains a number of ways to update the flash contents. The nand flash contents can be updated by

- programming the nand flash off-pcb using a prommer

- running a flasher program via the vs3emu emulator interface (requires RS-232)

- running a flasher program via an SPI EEPROM

- running a flasher program via the VS1000 USB mass storage backdoor

The last option is most convenient for players that don't have RS-232 port, such as the VS1000 Demonstration Board. When the VS1000 is switched to USB Mass Storage mode by attaching the USB cable when GPIO0[6] is low, it creates a logical drive that is presented to the USB host as a removable disk.

A special thing happens when the ROM software can't detect a nand flash chip (by reading the VLSI boot ID as explained earlier). In that case, the software creates a RAM disk of a few kilobytes. This can be detected by the disk being empty and having a size of only about 16 kilobytes. (The RAM disk also has the identifier signature "VLSIFATDISK" but that is normally not shown by Windows.)

This feature can be used for initial programming of the nand flash since at the first bootup of a new VS1000 device with an empty nand flash, the VLSI ID is not yet programmed into the nand flash and thus the RAM disk appears. Later on, when the nand flash is programmed and its contents need to be updated, the nand flash detection can be prevented by pulling CS1 low when powering up the VS1000. In the Demonstration Board this can be done by shorting TP2 and CS1 pads on the Developer Board PCB. When connected to the PC, the RAM disk appears and the short should be removed. The user can now copy files to the RAM disk using Windows/Unix etc.

A special file named VS1000\_A.RUN can now be copied to the RAM disk. When the USB cable is removed, without turning off power, the VS1000A loads and runs a boot record from that file. The maximum length of the boot record is 512 bytes.

For updating the flash contents, VS1000\_A.RUN should contain a flasher program, that reads another file named NANDFLSH.IMG from the RAM disk and writes its contents to the beginning of the nand flash. When the VS1000 boots up the next time, with CS1 pulled high, it uses and boots up from the nand flash with the updated software.