### **Video Electronics Standards Association**

2150 North First Street, Suite 440 San Jose, CA 95131-2029 Phone: (408) 435-0333 FAX: (408) 435-8225

# VESA BIOS EXTENSION (VBE) Core Functions Standard

Version: 3.0

Date: September 16, 1998

### Purpose

To standardize a modular, software interface to display and audio devices. The VBE interface is intended to simplify and encourage the development of applications that wish to use graphics, video, and audio devices without specific knowledge of the internal operation of the evolving target hardware.

### Summary

The VBE standard defines a set of extensions to the VGA ROM BIOS services. These functions can be accessed under DOS through interrupt 10h, or be called directly by high performance 32-bit applications and operating systems other than DOS.

These extensions also provide a hardware-independent mechanism to obtain vendor information, and serve as an extensible foundation for OEMs and VESA to facilitate rapid software support of emerging hardware technology without sacrificing backwards compatibility.

This page is intentionally blank.

# **Intellectual Property**

Copyright © 1993-1998 - Video Electronics Standards Association. All rights reserved.

While every precaution has been taken in the preparation of this standard, the Video Electronics Standards Association and its contributors assume no responsibility for errors or omissions, and make no warranties, expressed or implied, of functionality or suitability for any purpose.

The sample code contained within this standard may be used without restriction.

#### Trademarks

All trademarks used in this document are property of their respective owners.

- VESA, VBE, VESA DDC, VBE/AI, VBE/PM, and VBE/DDC are trademarks of Video Electronics Standards Association.

- MS-DOS and Windows are trademarks of Microsoft, Inc.

- IBM, VGA, EGA, CGA, and MDA are trademarks of International Business Machines

- RAMDAC is a trademark of Brooktree Corp.

- Hercules is a trademark of Hercules Computer Technology, Inc.

#### Patents

VESA proposal and standards documents are adopted by the Video Electronics Standards Association without regard to whether their adoption may involve patents on articles, materials, or processes. Such adoption does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the proposal or standards document.

## Support for this Specification

Clarifications and application notes to support this standard will be published as the need arises. To obtain the latest standard and support documentation, contact VESA.

If you have a product which incorporates VBE, you should ask the company that manufactured your product for assistance. If you are a display or controller manufacturer, VESA can assist you with any clarification you may require. All comments or reported errors should be submitted in writing to VESA, to the attention of Technical Support, using one of the following mechanisms:

| World Wide Web: | www.vesa.org     | Mail to:                                |

|-----------------|------------------|-----------------------------------------|

| E-mail:         | support@vesa.org | Video Electronics Standards Association |

| Fax:            | 408-435-8225     | 2150 North First Street, Suite 440      |

| Voice:          | 408-435-0333     | San Jose, California 95131-2029         |

# SSC VBE/Core Workgroup Members

Any industry standard requires input from many sources. The people listed below were members of the VBE/Core Workgroup of the Software Standards Committee (SSC) which was responsible for combining all of the industry input into this standard:

#### **CHAIRMAN**

Charimain, David Penley, Cirrus Logic, Inc. past chairnam, Kevin Gillett, S-MOS Systems, Inc., past chairman, Rod Dewell, Excalibur Solutions

#### **MEMBERS**

Jatinder Pancar, Alliance Seminconductor Armond Bruno, BrookTree Corporation Rebecca Nolan, Chips and Technologies, Inc. Andy Sobczyk, Cirrus Logic, Inc. Brad Haakenson, Cirrus Logic, Inc. Adrian Luff, Forte Technologies, Inc. Steven McGowen, Intel Corporation Jake Richter, Jon Peddie and Associates Matt Russo, Matrox Graphics, Inc. Todd Laney, Microsoft Corporation Thomas Block, Number Nine Visual Technology Corporation Mark Krueger, NVidia Corporation Dwight Diericks, NVidia Corporation Rex Wolfe, Phillips Semiconductor Raluca Iovan, Phoenix Technologies Ltd. Tim Crawford, Rendition, Inc. Kendall Bennett, SciTech Software, Inc Tom Ryan, SciTech Software, Inc Don Pannell, Sierra Semiconductor George Bystricky, S-MOS Systems, Inc. David Milici, StereoGraphics Corporation Tony Lin, Trident Microsystems, Inc. Mitch Paris, Tseng Labs, Inc. Joe Israel, Tseng Labs, Inc. Chris Tsang, ULSI Systems Danny Halamish, VideoLogic, Inc.. Gregory Hamlin, VRex, Inc. Thomas Roell, X Inside Inc.

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| SCOPE OF THE VBE STANDARD<br>Backgrounder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| VBE OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                                                                          |

| VBE Features<br>VBE Affected Devices<br>Providing Vendor Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                          |

| PROGRAMMING WITH VBE/CORE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                                          |

| ACCESSING LINEAR FRAMEBUFFER MEMORY.<br>USING REFRESH RATE CONTROL.<br>Using VBE/DDC to obtain monitor operational limits.<br>Using VM/GTF to compute CRTC values.<br>Computing the normalized pixel clock.<br>Setting double scan modes.<br>Setting Interlaced Modes.<br>USING HARDWARE TRIPLE BUFFERING.<br>USING STEREOSCOPIC LIQUID CRYSTAL SHUTTER GLASSES.<br>Automatic hardware display start address swapping (Method 1).<br>Automatic hardware display start address swapping (Method 2).<br>Software driven display start address swapping .<br>Refresh rates and stereoscopic imaging.<br>Left/right image synchronization<br>DEVELOPING FOR MAXIMUM COMPATIBILITY<br>Be prepared for different Window Granularity's.<br>Be prepared for both single and dual read/write Windows.<br>Be prepared to support both 15 and 16 bits per pixel high color modes.<br>Be prepared to support both 24 and 32 bits per pixel true color modes.<br>Some controllers can't do double scanned modes. | 6<br>7<br>8<br>8<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>9<br>10<br>11<br>12<br>12<br>12<br>13<br>13<br>13<br>14<br>14<br>14 |

| Check if VGA Compatible Before Touching Any VGA Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                                                         |

| Check if VGA Compatible Before Directly Programming the DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| VBE RETURN STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |

| VBE Mode Numbers<br>VBE Far Pointers<br>Obtaining the Protected Mode Entry Point<br>Calling the Protected Mode Entry Point<br>Protected Mode Entry Point Functional Restrictions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18<br>20<br>21<br>23<br>24                                                                                                 |

| Function 00h - Return VBE Controller Information<br>Function 01h - Return VBE Mode Information<br>Function 02h - Set VBE Mode<br>Function 03h - Return Current VBE Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30<br>40                                                                                                                   |

| Function 04h - Save/Restore State<br>Function 05h - Display Window Control<br>Function 06h - Set/Get Logical Scan Line Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46                                                                                                                         |

| Function 07h - Set/Get Display Start                                    |    |

|-------------------------------------------------------------------------|----|

| FUNCTION 08H - SET/GET DAC PALETTE FORMAT                               |    |

| Function 09h - Set/Get Palette Data                                     |    |

| FUNCTION 0AH - RETURN VBE PROTECTED MODE INTERFACE                      |    |

| FUNCTION 0BH - GET/SET PIXEL CLOCK                                      | 59 |

| VBE SUPPLEMENTAL SPECIFICATIONS                                         | 60 |

| PURPOSE OF SUPPLEMENTAL SPECIFICATIONS                                  |    |

| OBTAINING SUPPLEMENTAL VBE FUNCTION NUMBERS                             | 60 |

| REQUIRED VBE SUPPLEMENTAL SPECIFICATION COMPONENTS                      | 61 |

| VBE Supplemental Specification Functions                                | 61 |

| Return Status                                                           |    |

| Subfunction 00h - Return VBE Supplemental Specification Information     |    |

| LOADING SUPPLEMENTAL DRIVERS                                            |    |

| IMPLEMENTATION QUESTIONS                                                |    |

| KNOWN SUPPLEMENTAL SPECIFICATIONS                                       |    |

| Function 10h - Power Management Extensions (PM)                         |    |

| Function 11h - Flat Panel Interface Extensions (FP)                     |    |

| Function 13h - Audio Interface Extensions (AI)                          |    |

| Function 14h - OEM Extensions                                           |    |

| Function 15h - Display Data Channel (DDC)                               |    |

| APPENDIX 1 - VBE IMPLEMENTATION CONSIDERATIONS                          | 65 |

| MINIMUM FUNCTIONALITY REQUIREMENTS                                      |    |

| Required VBE Services                                                   |    |

| Minimum ROM Implementation                                              |    |

| TSR Implementations                                                     |    |

| VGA BIOS IMPLICATIONS                                                   |    |

| REAL MODE ROM SPACE LIMITATIONS                                         |    |

| Data Storage                                                            |    |

| Removal of Unused VGA Fonts                                             |    |

| Deleting VGA Parameter Tables                                           |    |

| Increasing ROM Space                                                    |    |

| Support of VGA TTY Functions Developing Dual-Mode BIOS code             |    |

|                                                                         |    |

| Determining when in Protected Mode<br>Things to avoid in Protected Mode |    |

| Returning pointers in info blocks                                       |    |

| Supporting Multiple Controllers                                         |    |

| Dual-Controller Designs                                                 |    |

| Provision for Multiple Independent Controllers                          |    |

| OEM EXTENSIONS TO VBE                                                   |    |

| APPENDIX 2 - SAMPLE SOURCE CODE                                         |    |

|                                                                         |    |

| C Language Module                                                       |    |

| Assembly Language Module                                                | 80 |

| APPENDIX 3 - DIFFERENCES BETWEEN VBE REVISIONS                          |    |

| VBE 1.0                                                                 |    |

| VBE 1.1                                                                 | 82 |

| VBE 1.2                                                                 | 82 |

| VBE 2.0                                                                 |    |

| VBE 2.0, Rev. 1.1                                                       |    |

| VBE 3.0                                                                 | 85 |

| APPENDIX 4 - RELATED DOCUMENTS | 1 |

|--------------------------------|---|

|--------------------------------|---|

# Introduction

This document contains the VESA BIOS Extension (VBE) specification for standard software access to graphics display controllers which support resolutions, color depths, and frame buffer organizations beyond the VGA hardware standard. It is intended for use by both applications programmers and system software developers. It is also intended to provide an extended interface to support enhanced refresh rate control for operating system utilities and drivers.

System software developers may use this document to supplement the System and INT 10h ROM BIOS functions to provide the VBE services. Application developers can use this document as a guide to programming all VBE compatible devices.

To understand the VBE specification, some knowledge of 80x86 assembly language and the VGA hardware registers may be required. However, the services described in this specification may be called from any high-level programming language that provides a mechanism for generating software interrupts with the 80x86 registers set to user-specified values.

In this specification, 'VBE' and 'VBE 3.0' are synonymous with 'VBE Core Functions version 3.0'.

## Scope of the VBE Standard

The primary purpose of the VESA VBE is to provide standard software support for the many unique implementations of Super VGA (SVGA) graphics controllers on the PC platform that provide features beyond the original VGA hardware standard. This is to provide a feasible mechanism by which application developers can take advantage of this nonstandard hardware in graphics applications.

The VBE specification offers an extensible software foundation which allows it to evolve as display and audio devices evolve over time, without sacrificing backward software compatibility with older implementations. New application software should be able to work with older hardware, and application software that has already shipped should work correctly on new hardware devices.

VBE services provide standard access to all resolutions and color depths provided on the display controller, and report the availability and details of all supported configurations to the application as necessary.

VBE implementations facilitate the field support of audio and display hardware by providing the application software with the manufacturer's name and the product identification of the display hardware.

Since graphics controller services on the PC are typically implemented in ROM, the VBE services are defined so that they should be implemented within the standard VGA ROM. When ROM

implementations of VBE are not possible, or when field software upgrades to the onboard ROM are necessary, the VBE implementation may be also offered as a device driver or DOS Terminate and Stay Resident (TSR) program.

The standard VBE functions may be supplemented by OEM's as necessary to support custom or proprietary functions unique to the manufacturer. This mechanism enables the OEM to establish functions that may be standard to the product line, or provide access to special hardware enhancements.

Although previous VBE standards assumed that the underlying graphics architecture was a VGA device, the display services described by VBE 3.0 can be implemented on any frame buffer oriented graphics device.

The majority of VBE services facilitate the setup and configuration of the hardware, allowing applications high performance, direct access to the configured device at runtime. To further improve the performance of flat frame buffer display devices in extended resolutions, VBE 3.0 provides new memory models that do not require the traditional frame buffer "banking" mechanisms.

VBE is expected to work on all 80x86 platforms, in real and protected modes. Starting with VBE 3.0, all the VBE/Core BIOS functions can be 'dual-mode', allowing them to optionally be called as 16-bit protected mode code via a direct call to a new protected mode interface entry point. 'Dual-mode' code means that the BIOS code adheres to certain restrictions when called via the protected mode entry point, to ensure full compatibility with fully protected mode operating systems such as Windows NT, OS/2 and the many versions of UNIX. Note that although the 'dual-mode' code must be called as 16-bit protected mode code, this does not preclude it from being called by 32-bit pure operating systems such as Windows NT and OS/2. Since some modern display devices are designed without any VGA support, two or more display controllers may be present in the system. One display controller could be used for VGA compatibility, and the other used for graphic extensions to the basic VGA modes, resolutions, and frame buffer models. Since it is not possible to support multiple controllers easily via the INT 10h software interface, only the primary controller will be supported via this interface and its BIOS will be located at C0000h. If multiple controllers are present in the system, the second controller can only be controlled via the VBE/AF Accelerator Functions specification (contact VESA for more information).

Note that the VBE/Core specification does not include any support for hardware acceleration functions such as 2D and 3D graphics primitives or video acceleration. If you wish to use such features please refer to the VBE/AF Accelerator Functions specification (contact VESA for more information).

### Backgrounder

The IBM VGA<sup>1</sup> has become a de facto standard in the PC graphics world. A multitude of different VGA offerings exist in the marketplace, each one providing BIOS or register compatibility with the IBM VGA. More and more of these VGA compatible products implement various supersets of the VGA standard. These extensions range from higher resolutions and more colors to improved performance and even some graphics processing capabilities. Intense competition has dramatically improved the price/performance ratio, to the benefit of the end user.

However, several serious problems face a software developer who intends to take advantage of these "Super VGA"<sup>2</sup> environments. Because there is no standard hardware implementation, the developer is faced with widely different Super VGA hardware architecture. Lacking a common software interface, designing applications for these environments is costly and technically difficult. Except for applications supported by OEM-specific display drivers, very few software packages can take advantage of the power and capabilities of Super VGA products.

The VBE standard was originally conceived to enable the development of applications that wished to take advantage of display resolutions and color depths beyond the VGA definition. The need for an application or software standard was recognized by the developers of graphic hardware to encourage the use and acceptance of their rapidly advancing product families. It became obvious that the majority of software application developers did not have the resources to develop and support custom device level software for the hundreds of display boards on the market. Therefore the rich new features of these display devices were not being used outside of the relatively small CAD market, and only then after considerable effort.

Indeed, the need for a standard for SVGA display adapters became so important that the VESA organization was formed to seek out a solution. The original VBE standard was devised and agreed upon by each of the active display controller manufacturers, and has since been adopted by DOS application developers to enable use of non-VGA extended display modes.

As time went along VBE 1.1 was created to add more video modes and increased logical line length/double buffering support. VBE 1.2 was created to add modes and also added high color RAMDAC support.

In the three years since VBE 1.2 was approved we have seen the standard become widely accepted and many successful programs have embraced VBE. However, it has become obvious that the need for a more robust and extensible standard exists. Early extensions to the VGA standard continued using all of the original VGA I/O ports and frame buffer address to

<sup>&</sup>lt;sup>1</sup> IBM and VGA are trademarks of International Business Machines Corporation.

<sup>&</sup>lt;sup>2</sup> The term "Super VGA" is used in this document for a graphics display controller implementing any superset of the standard IBM VGA display adapter.

communicate with the controller hardware. As we've seen, the supported resolutions and color depths have grown, intelligent controllers with BITBLT and LineDraw Functions have become common, and new flat frame buffer memory models have appeared along with display controllers that are not based on VGA in any way. VBE 2.0 and future extensions will support non-VGA based controllers with new functions for reading and writing the palette and for access to the flat frame buffer models.

VBE 3.0, as designed, offers the extensibility and the robustness that was lacking in the previous specifications, while at the same time offering backwards compatibility.

This chapter outlines the various features and limitations of the VBE 3.0 standard.

### **VBE Features**

- Standard application interface to Graphics Controllers (SVGA Devices).

- Optional protected mode interface for OS's such as Windows NT, OS/2 and UNIX.

- Standard method of overriding the refresh rate for supported modes.

- Stereoscopic display support for liquid crystal (LC) shutter glasses.

- Standard method of identifying products and manufacturers.

- Provision for OEM extensions through Subfunction 14h.

- Extensible interface through supplemental specifications.

#### **VBE Affected Devices**

All frame buffer-based devices in the PC platform (with the exception of Hercules, Monochrome (MDA), CGA and EGA devices) are suitable for use within the VBE standard to enable access to the device by VBE-compliant applications.

### **Providing Vendor Information**

The VGA specification does not provide a standard mechanism to determine what graphic device it is running on. Only by knowing OEM-specific features can an application determine the presence of a particular graphics controller or display board. This often involves reading and testing registers located at I/O addresses unique to each OEM. By not knowing what hardware an application is running on, few, if any, of the extended features of this hardware can be used.

The VESA BIOS Extension provides several functions to return information about the graphics environment. These functions return system level information as well as graphics mode specific details. Function 00h returns general system level information, including an OEM identification string. The function also returns a pointer to the supported VBE and OEM modes. Function 01h may be used by an application to obtain additional information about each supported mode. Function 03h returns the current VBE mode.

This section contains application and systems programming information for some of the more advanced functions that VBE 3.0 provides.

### Accessing Linear Framebuffer Memory

Once you have initialized the graphics hardware into a mode that supports a hardware linear framebuffer, you need to create a pointer that your application can use to write to the linear framebuffer memory. The first thing you should realize is that the linear framebuffer location reported in the ModeInfoBlock for the mode you are using is a *physical* memory address, and cannot be used directly from protected mode applications. Before you can use the memory you must use the services your operating system provides to map the physical memory to a linear memory address, and then map this linear address into your applications memory space. Under DPMI mapping the linear memory is done with DPMI function 0x800, and equivalent functions exist under other operating systems.

The steps involved in mapping in a linear framebuffer region are as follows (32-bit protected mode only):

- 1. Map the physical memory address to a linear memory address (using DPMI function 0x800 for example).

- 2. Find the base address of the default DS selector for your operating environment.

- 3. Subtract the base address from the linear address computed in step 1 to give you a near pointer (relative to DS) that you can use from within your code.

### **Using Refresh Rate Control**

VBE 3.0 provides support for refresh rate control by allowing the calling application to pass a set of custom CRTC timing values to the BIOS when a mode set is being performed. This provides for maximum versatility and allows the application to program specific CRTC timing values if this is necessary (for instance specialized display hardware such as head mounted displays or fixed frequency monitors).

When the calling application wishes to control the refresh rate for the mode being initialized, it must compute a set of CRTC values and a normalized pixel clock that can be passed to function 4F02h when the mode is initialized. The VBE 3.0 interface does not provide any means to compute these values, and the values can either be taken from discrete VESA DMT timings, or by using the new VM/GTF Generalized Timing Formula to compute the CRTC values to be used. Once you have these values, you must search for an available pixel clock that is the closest to

what you want by calling VBE function 4F0Bh (if you are using GTF to compute the CRTC values, you should re-run the GTF calculations routines based on the pixel clock returned by 4F0Bh to get the final CRTC values).

The steps involved in initializing a mode with a specific refresh rate are as follows:

- 1. Use VBE/DDC to obtain the operational limits of the monitor if VBE/DDC is available and the monitor is DDC compliant. Use these values to restrict the calculated values or modes that you can make available.

- 2. Use either the DMT timings or GTF formulas to compute a set of CRTC timings and normalized pixel clock for the mode and refresh rate that you want to initialize. If the mode is a double scanned mode (200, 240 or 300 lines) double the vertical resolution used to drive the GTF CRTC calculations (i.e.: use 400 lines for the vertical number of lines).

- 3. Call VBE function 4F0Bh to find the actual pixel clock that will be programmed for the normalized pixel clock that you have requested.

- 4. If you are using GTF, re-run the GTF formulas using the resulting normalized pixel clock returned by function 4F0Bh to compute the proper CRTC timings given the exact pixel clock that will be used for the resulting mode. This is an important step to ensure that the GTF timings will be exact for the resulting mode given the available pixel clocks the hardware supports (and PLL resolution for programmable pixel clocks).

- 5. If you are setting a double scanned mode (200, 240 or 300 lines vertical) set the double scan flag in the CRTCInfoBlock.

- 6. If you are enabling an interlaced mode, set the interlace flag in the CRTCInfoBlock.

- 7. Call function 4F02h with bit D11 set in the mode number and pass in the CRTC timings and pixel clock in the CRTCInfoBlock.

### Using VBE/DDC to obtain monitor operational limits

The VBE/DDC interface can be used to obtain the operational limits of the attached monitor, such as the minimum and maximum horizontal and vertical frequencies as well as supported resolutions. If the monitor and graphics card both support DDC, this information should be obtained and used to restrict the refresh rate computation routines to ensure that the resulting CRTC values do not produce a mode that lies outside the operational limits of the attached monitor.

Please refer to the VBE/DDC and EDID specifications for more information on how to obtain the operational limits of the monitor.

### Using VM/GTF to compute CRTC values

The VESA Monitor Committee's GTF (Generalized Timing Formula) standard defines a set of formulas that can be used to compute GTF compatible CRTC timings given a couple of input parameters. GTF can be used to generate CRTC timings given the resolution and one of either the vertical frequency, horizontal frequency or pixel clock. For more information please refer to the GTF specification for the formulas and sample code for calculating GTF compliant CRTC values.

Note that GTF can be used to generate timings that will display properly on both new GTF compatible monitors and for existing non-GTF compliant monitors.

### Computing the normalized pixel clock

Once you have generated a set of CRTC timings from the DMT timings or using the GTF formula, the pixel clock will be an arbitrary pixel clock which may not be directly programmable in the hardware. Once you have the normalized pixel clock, you must then call VBE function 4F0Bh to find the exact value of the closest pixel clock that the hardware can program. Note that when you call function 4F0Bh, you *must* pass it the correct value of the graphics mode that you will be using the pixel clock for. This allows the underlying VBE implementation to make any necessary adjustments before running the clock through the PLL calculation routines so that you will be returned the exact pixel clock that will be programmed by the hardware.

### Setting double scan modes

If double scanning is supported by the hardware, it is possible to support modes like 320x200, 320x240 and 400x300 that scan each line twice in the vertical direction. These modes cannot be implemented without double scanning support, and if the application is attempting to perform refresh rate control on these modes, setting the double scan bit is required.

When setting a double scan mode, the actual CRTC parameters calculated and passed in will be equal to double the number of vertical lines. Hence for a 200 line mode you would actually set the vertical CRTC parameters and pixel clock for a 400 line mode, and set the double scan bit to convert the mode to a 200 line addressable mode. Note that if you are using double scanned modes, you cannot enable interlaced operation.

### Setting Interlaced Modes

If interlaced mode is supported by the hardware, bit D9 will be set in the ModeAttributes field of the ModeInfoBlock for the graphics mode in question. If this bit is set, you can enable interlaced operation by setting bit D1 of the Flags field of the CRTCInfoBlock passed in to function 4F02h. The CRTC timings for the interlaced mode will be identical to the non-interlaced mode.

Note that some new hardware may not support interlaced operation, so make sure you check the ModeInfoBlock attributes field to ensure interlaced is supported before attempting to initialize an interlaced mode. Note that if you are using double scanned modes, you cannot enable interlaced operation. Generally interlaced operation is only available for modes with resolutions of 640x480 and higher, and most hardware will have a hard time enabling interlaced operation for lower resolution modes.

### **Using Hardware Triple Buffering**

Hardware triple buffering is supported in the VBE/Core specification by allowing the application to schedule a display start address change, and then providing a function that can be called to determine the status of the last scheduled display start address change. VBE Function 4F07h is used for this, along with subfunctions 02h and 04h. To implement hardware triple buffering you would use the following steps:

- 1. Display from the first visible buffer, and render to the second hidden buffer.

- 2. Schedule a display start address change for the second hidden buffer that you just finished rendering (4F07h, 02h), and start rendering immediately to the third hidden buffer. CRT controller is currently displaying from the first buffer.

- 3. Before scheduling the display start address change for the third hidden buffer, wait until the last scheduled change has occurred (4F07h, 04h returns not 0). Schedule display start address change for the third hidden buffer and immediately begin rendering to the first hidden buffer. CRT controller is currently displaying from the second buffer.

- 4. Repeat step 3 over and over cycling though each of the buffers.

Although the above method does require a spin loop polling on Function 4F07h/04h, in most cases when this function is called the display start address change will already have occurred and the spin loop will time out immediately. The only time that this cannot occur is if the application is rendering at a frame rate in excess of the current hardware refresh rate (i.e.: in excess of 60-70 frames per second), and the resulting frame rate for the application will be pegged at the hardware refresh rate.

## Using Stereoscopic Liquid Crystal Shutter Glasses

Stereoscopic liquid crystal (LC) shutter glasses are a cheap, easy solution for getting real 3D stereoscopic imaging out of a standard PC with any standard monitor. LC shutter glasses work by constantly blanking out video information for each eye in a sequential fashion, allowing the user to see the left image for a fraction of a second followed by the right image, followed by the left image again etc. In order to make LC shutter glasses work effectively on PC based graphics controllers, some mechanism for changing the displayed video information at every vertical retrace is necessary. New hardware is available that will do this automatically, and VBE 3.0 defines the software interface necessary to allow applications to use these new hardware features.

There are two methods of performing hardware stereoscopic page flipping with VBE 3.0, depending on the available underlying hardware capabilities. All VBE implementations that have stereoscopic should support the first method, while the second method requires that the hardware implement dual display start addresses. Please check the mode information ModeAttributes field bit D12 to see if dual display start addressing is supported.

The steps involved in enabling free running stereoscopic support are as follows (Method 1 - consecutive left right images):

- 1. Set the mode via function 4F02h (using a high refresh rate if possible)

- 2. Enable free running stereoscopic mode with function 4F07h subfunction 05h.

- 3. Perform standard double buffered or triple buffered graphics using function 4F07h subfunctions 02h/04h/82h, but draw both the left and right images consecutively in memory rather than just a single image. Once both left and right eye images are rendered, the display can be swapped as would be done for normal double/triple buffered graphics.

- 4. Disable free running stereoscopic mode with function 4F07h subfunction 06h when you are done with stereoscopic viewing.

The steps involved in enabling free running stereoscopic support are as follows (Method 2 - dual display start addresses):

- 1. Set the mode via function 4F02h (using a high refresh rate if possible)

- 2. Draw the left and right images in video memory any way you wish (see below for some possible scenarios), and use subfunctions 03h or 83h to set the display start addresses for the left and right images in memory. Calling subfunction 03h or 83h will automatically enable free running stereoscopic mode for the controller. You can then render your next frame in memory and use 03h/04h/83h to perform standard double buffered or triple buffered graphics with both a left and right image for each buffer.

- 3. Disable free running stereoscopic mode with function 4F07h subfunction 06h when you are done with stereoscopic viewing.

### Automatic hardware display start address swapping (Method 1)

VBE 3.0 supports hardware implementations that can be programmed to automatically swap between the left and right images of the stereoscopic display automatically every vertical retrace. Normally when a mode is set, stereoscopic mode will be disabled and can be enabled by the application by calling function 4F07h, subfunction 05h (and disabled with subfunction 06h). Once stereoscopic mode has been enabled, the hardware will display the left image from the data in video memory defined by the current display start address, followed by the right image in the following frame from the video memory immediately following the left image. After the right image has been displayed the hardware will begin displaying the left image again in a continuous cycle.

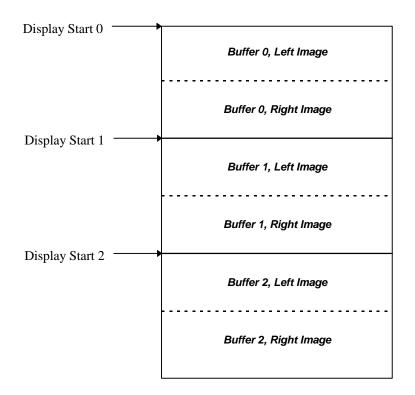

The diagram below shows how the pages would be laid out in video memory for a triple buffered, stereoscopic enabled graphics mode:

While the hardware has been programmed to display from buffer 0, it will continuously cycle between the left and right images in buffer 0. When the application request to change to buffer 1, it will change to continuously cycle between the left and right images for buffer 1. Note that if display start 1 is programmed while the hardware is displaying the left image in buffer 0, the hardware may switch to the right image in buffer 1 at the next vertical retrace or it may continue on and display the right image buffer 0, switching to buffer 1 after the buffer 0 right image has been displayed.

### Automatic hardware display start address swapping (Method 2)

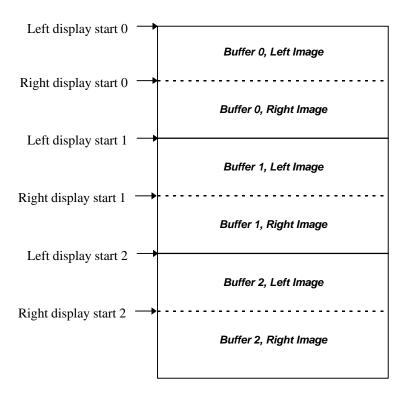

VBE 3.0 supports hardware implementations that can be programmed to automatically swap between the left and right images of the stereoscopic display automatically every vertical retrace. Normally when a mode is set, stereoscopic mode will be disabled and can be enabled by the application by calling function 4F07h, subfunctions 03h or 82h (and disabled with subfunction 06h). Once stereoscopic mode has been enabled, the hardware will display the left image from the data in video memory defined by the current left display start address, followed by the right image from the data in video memory defined by the current right display start address. After the right image has been displayed the hardware will begin displaying the left image again in a continuous cycle.

The diagram below shows how the pages could be laid out in video memory for a triple buffered, stereoscopic enabled graphics mode using a above/below approach:

While the hardware has been programmed to display from buffer 0, it will continuously cycle between the left and right images in buffer 0. When the application request to change to buffer 1, it will change to continuously cycle between the left and right images for buffer 1. Note that if display start 1 is programmed while the hardware is displaying the left image in buffer 0, the hardware may switch to the right image in buffer 1 at the next vertical retrace or it may continue on and display the right image buffer 0, switching to buffer 1 after the buffer 0 right image has been displayed.

### Software driven display start address swapping

If the hardware does not support a free running stereoscopic display mode, the application must implement the free running display start address changes in software using a timer interrupt handler. The application should set the timer interrupt handler to run at a rate very close to the vertical refresh rate of the graphics mode being used, and use function 4F07h to swap the display start address during the vertical retrace interval.

### Refresh rates and stereoscopic imaging

When the hardware is running in free running stereoscopic mode and an image or 3D scene is being viewed through LC shutter glasses, the user will see the resulting image at half the original refresh rate through the shutter glasses. Hence a normally acceptable display running at 60Hz becomes a hard to view display running at 30Hz stereoscopic. For this reason when running in stereoscopic modes it is desirable to significantly increase the refresh rate of the graphics mode to values as high as 120Hz or 140Hz (depending on the monitors capabilities), which provides for 60Hz or 70Hz refresh per eye in stereoscopic modes.

VBE 3.0 has full support for refresh rate control when setting a display mode via function 4F02h. Stereoscopic applications can use this functionality in combination with the GTF standard to increase the refresh rate of the stereoscopic application to acceptable levels (see the above section on refresh rate control for more information).

#### Left/right image synchronization

Signaling to the stereoscopic LC shutter glasses which image is currently being displayed is out of the scope of this specification, however the VBE/Core specification does include capabilities bits to let the application software know when a hardware stereoscopic synchronization signal is available. VESA is currently working on a new hardware standard for both the standard VGA and the new EVC connector's for signaling this synchronization information, and VBE function 4F00h will let the application know if stereoscopic signaling is available via the EVC connector or via the VESA stereoscopic signaling connector. Please contact VESA for more information on this new hardware signaling standard.

### **Developing for Maximum Compatibility**

This section contains information relating to developing application software with maximum compatibility in mind, without sacrificing performance or features. Although the VBE standard defines how the specification should work, there are many different flavors of hardware out in the field. It is very important that you design your application with the following special cases in mind so that your application will run on the widest variety of hardware possible.

One of the common mistakes that many developers make when they first start developing graphics code with VBE devices is to assume the graphics card they have in their system is a representative sample of what exists in the field. Although the VBE interface will be identical on another graphics card, the capabilities and attributes that card reports may be different. This section also deals with explaining the most common pitfalls that plague developers first starting to develop VBE code.

This section is also very useful for the hardware vendor implementing a VBE BIOS for their graphics hardware, as it allows the hardware vendor to understand some of the more common pitfalls that developers will fall into, and to try and develop their BIOS code (and future hardware) to provide for the best compatibility in the field.

### Be prepared for different Window Granularity's

One area that is of vital importance is the Windows Granularity, or the smallest increment that you can move the bank switching window. Many controllers simply provide a 64Kb granularity, which means that bank 0 starts at 0, bank 1 at 64Kb and bank 2 at 128Kb etc. However some controllers may provide either a 4Kb or a 16Kb granularity. For a 4Kb granularity controller, bank 0 starts at 0 while bank 1 starts at 4Kb not 64Kb. On a 4Kb system to move the window to the next 64Kb location you would need to program bank number 8 rather than bank number 1.

One method of adjusting the bank numbers in your bank switching code is outlined in the sample code in Appendix 2. This code basically finds a *shift factor* when the mode is initialized that indicates how many bits to shift the bank value left to adjust from a 64Kb window to the granularity of the hardware. In your bank switch code you simply shift the bank value left by the specified number of bits before calling the VBE bank switch function.

### Be prepared for both single and dual read/write Windows

Another area of importance is if the controller has a single read/write window or separate read and write window's. On a controller with a single read/write window (the most common scenario), setting the first window will change the offset in the framebuffer where both reads and writes occur to the same location. On a controller with dual read/write window's, you can individually change the location in the framebuffer where read operations will occur and the location where write operations will occur.

To provide for maximum performance you should make sure you check the modeInfoBlock attributes for the graphics mode you are programming. If separate read/write windows are provided you must ensure that you set both windows to the same location with two calls to the bank switch function.

### Be prepared to support both 15 and 16 bits per pixel high color modes

Many new games and applications have support for 15 and 16 bits per pixel high color modes. If you wish to support these modes, don't make the mistake of assuming that all devices will support 16 bit high color modes, or that all devices will support 15 bit high color modes. There are devices in the field that support only 15 bit modes, and there are also devices in the field that support only 16 bit modes. Hence it is of vital importance that your application code support both of these color depths to ensure maximum compatibility.

### Be prepared to support both 24 and 32 bits per pixel true color modes

If you are developing code to support 24 bit true color rendering, be prepared to find controllers in the field that have the true color modes support as either 24 bits per pixel (3 bytes per pixel) or 32 bits per pixel (4 bytes per pixel). Generally the 32 bits per pixel modes are faster because the pixels can be written with a single CPU double word access, however 32 bits per pixel modes require a controller that has at least 2Mb of memory.

Hence with controllers that have 2Mb or more of memory, be prepared to find support for only 32 bits per pixel modes and no 24 bits modes.

### Some controllers can't do double scanned modes

If you are developing a game or application that wishes to support 320x200 or 320x240 modes (in any color depth), be prepared for situations where these modes do not exist. To be able to initialize these modes on today's hardware requires support for double scanning, and there are some controllers in the field that do not support this. On these controllers these modes can never

be supported, so you application or game must be able to deal with the situation if these modes do not exist.

In lieu of these modes not being available, the controller may provide support for 320x400 and 320x480 modes which do not require double scanning (this is recommended for hardware vendors who don't have double scanning support). One neat solution is to support these modes by rendering your frames to a system memory buffer with a resolution 320x200 or 320x240, and then do a copy to the graphics screen with a 2x vertical stretch (just duplicate every scanline twice in software). The end result will look identical to a real 320x200 or 320x240 mode, and you will only lose a small amount in overall performance (and it will be much faster than rendering directly to a 320x400 or 320x480 screen for graphics intensive games).

## Check if VGA Compatible Before Touching Any VGA Registers

Many developers find that there is an irresistible urge to push the boundaries of performance, and they will try anything and everything they can do attain these goals. One of the things that is commonly done is to perform weird and wonderful feats of magic using some of the standard VGA registers. This does work, and work well on VGA compatible graphics cards, but not on all cards!

If the graphics controller is based on a NonVGA graphics hardware technology (and many popular ones and many newer ones are), in the SuperVGA graphics modes the VGA registers simply do not exist anymore, and attempting to synch to these registers will put your code into an infinite loop. So be forewarned that doing any fiddling with the standard VGA registers is asking for trouble on certain graphics card that use NonVGA controllers to program the SuperVGA graphics modes (and lots more of these are coming out).

There is however a solution for VBE 2.0 and above controllers. There is a bit in the VBE modeInfoBlock for every graphics mode that indicates whether that mode is a NonVGA mode or VGA compatible mode. If this bit is set indicating that a NonVGA controller is being used to program the desired graphics mode, you must not do anything related to re-programming any of the standard VGA registers. In these cases you must fallback onto generic code that will perform all its graphics card interaction through the standard VBE 2.0 and above services.

## Check if VGA Compatible Before Directly Programming the DAC

Another area of concern is programming the color palette in 256 color modes. Once again the same problem occurs when programming the palette for NonVGA controllers; the VGA palette registers no longer exist and attempting to program the palette via these registers will simply do nothing. Even worse attempting to synch to the vertical or horizontal retrace will also cause the system to get into an infinite loop.

Hence if you need to program the color palette on a NonVGA controller, you must use the supplied VBE 2.0 and above palette programming routines rather than programming the palette directly. Make sure you check the NonVGA attribute bit as discussed above, and if a NonVGA

mode is detected you will have to program the palette via the standard VBE 2.0 and above services.

# **VBE Function Reference**

This chapter describes in detail each of the functions defined by the VBE standard. VBE functions are called from real mode using the INT 10h software interrupt vector, passing arguments in the 80X86 registers. The INT 10h interrupt handler first determines if a VBE function has been requested, and if so, processes that request. Otherwise control is passed to the standard VGA BIOS for completion. Starting with VBE 3.0, VBE functions can also be called directly from protected mode via the protected mode entry point. When called via the protected mode entry point, the VBE functions execute as 16-bit protected mode code which can be called directly from any 16-bit or 32-bit protected mode operating system or application.

All VBE functions are called with the AH register set to 4Fh to distinguish them from the standard VGA BIOS functions. The AL register is used to indicate which VBE function is to be performed. For supplemental or extended functionality the BL register is used when appropriate to indicate a specific subfunction.

Functions 00h-0Fh have been reserved for Standard VBE function numbers; Functions 10h-FFh are reserved for VBE Supplemental Specifications.

In addition to the INT 10h interface and protected mode entry point, a simple 32-bit Protected Mode Interface is available and is described below. In cases where there is both a standard interface and a 32-bit protected mode interface, the register parameters for both interfaces will be defined one after another for the function specification.

## **VBE Return Status**

The AX register is used to indicate the completion status upon return from VBE functions (except for 32 bit protected mode functions; 32 bit versions of the functions do not return any status information or return codes). If VBE support for the specified function is available, the 4Fh value passed in the AH register on entry is returned in the AL register. If the VBE function completed successfully, 00h is returned in the AH register. Otherwise the AH register is set to indicate the nature of the failure.

### VBE RETURN STATUS

| AL == 4Fh:    | Function is supported                                           |

|---------------|-----------------------------------------------------------------|

| AL $!= 4$ Fh: | Function is not supported                                       |

| AH == 00h:    | Function call successful                                        |

| AH == 01h:    | Function call failed                                            |

| AH == 02h:    | Function is not supported in the current hardware configuration |

| AH == 03h:    | Function call invalid in current video mode                     |

**Note:** Applications should treat any non-zero value in the AH register as a general failure condition as later versions of the VBE may define additional error codes.

#### **VBE Mode Numbers**

Standard VGA mode numbers are 7 bits wide and presently range from 00h to 13h. OEMs have defined extended display modes in the range 14h to 7Fh. Values from 80h to FFh cannot be used, since VGA BIOS Function 00h (Set video mode) interprets bit 7 as a flag to clear or preserve display memory.

Due to the limitations of 7-bit mode numbers, the optional VBE mode numbers are 14 bits wide. To initialize a VBE mode, the mode number is passed in the BX register to VBE Function 02h (Set VBE mode).

The format of VBE mode numbers is as follows:

| D0-D8  | = | Mode number                                                     |

|--------|---|-----------------------------------------------------------------|

|        |   | If $D8 == 0$ , this is not a VESA defined VBE mode              |

|        |   | If $D8 == 1$ , this is a VESA defined VBE mode                  |

| D9-D12 | = | Reserved by VESA for future expansion $(= 0)$                   |

| D11    | = | Refresh Rate Control Select                                     |

|        |   | If $D11 == 0$ , Use current BIOS default refresh rate           |

|        |   | If $D11 == 1$ , Use user specified CRTC values for refresh rate |

| D12-13 | = | Reserved for VBE/AF (must be 0)                                 |

| D14    | = | Linear/Flat Frame Buffer Select                                 |

|        |   | If $D14 == 0$ , Use Banked/Windowed Frame Buffer                |

|        |   | If D14 == 1, Use Linear/Flat Frame Buffer                       |

| D15    | = | Preserve Display Memory Select                                  |

|        |   | If $D15 == 0$ , Clear display memory                            |

|        |   | If $D15 == 1$ , Preserve display memory                         |

Thus, VBE mode numbers begin at 100h. This mode numbering scheme implements standard 7-bit mode numbers for OEM-defined modes (OEM defined modes are those that can be set via the Standard VGA BIOS). Standard VGA modes may be initialized through VBE Function 02h (Set VBE mode) simply by placing the mode number in BL and clearing the upper byte (BH). 7-bit OEM-defined display modes may be initialized in the same way. Note that VBE modes may only be set if the mode exists in the VideoModeList pointed to by the VideoModePTR returned in Function 00h, while Standard VGA modes and OEM defined 7 bit modes may be initialized without a corresponding entry in the VideoModeList and a mode info block. The exception to this requirement is the VBE mode number 81FFh.

To date, VESA has defined one special 7-bit mode number, 6Ah, for the 800x600, 16-color, 4-plane graphics mode. The corresponding 15-bit mode number for this mode is 102h. The following VBE mode numbers have been previously defined by VESA:

| GRAPH  | ICS   |             |                  | TEXT        |        |         |      |

|--------|-------|-------------|------------------|-------------|--------|---------|------|

| 15-bit | 7-bit | Resolution  | Colors           | 15-bit      | 7-bit  | Columns | Rows |

| mode   | mode  |             |                  | mode        | mode   |         |      |

| number | numbe | er          |                  | number      | number |         |      |

| 100h   | -     | 640x400     | 256              | 108h        | -      | 80      | 60   |

| 101h   | -     | 640x480     | 256              | 109h        | -      | 132     | 25   |

| 102h   | 6Ah   | 800x600     | 16               | 10Ah        | -      | 132     | 43   |

| 103h   | -     | 800x600     | 256              | 10Bh        | -      | 132     | 50   |

| 104h   | -     | 1024x768    | 16               | 10Ch        | -      | 132     | 60   |

| 105h   | -     | 1024x768    | 256              |             |        |         |      |

| 106h   | -     | 1280x1024   | 16               |             |        |         |      |

| 107h   | -     | 1280x1024   | 256              |             |        |         |      |

| 10Dh   | -     | 320x200     | 32K (1:5:5:5)    |             |        |         |      |

| 10Eh   | -     | 320x200     | 64K (5:6:5)      |             |        |         |      |

| 10Fh   | -     | 320x200     | 16.8M (8:8:8)    |             |        |         |      |

| 110h   | -     | 640x480     | 32K (1:5:5:5)    |             |        |         |      |

| 111h   | -     | 640x480     | 64K (5:6:5)      |             |        |         |      |

| 112h   | -     | 640x480     | 16.8M (8:8:8)    |             |        |         |      |

| 113h   | -     | 800x600     | 32K (1:5:5:5)    |             |        |         |      |

| 114h   | -     | 800x600     | 64K (5:6:5)      |             |        |         |      |

| 115h   | -     | 800x600     | 16.8M (8:8:8)    |             |        |         |      |

| 116h   | -     | 1024x768    | 32K (1:5:5:5)    |             |        |         |      |

| 117h   | -     | 1024x768    | 64K (5:6:5)      |             |        |         |      |

| 118h   | -     | 1024x768    | 16.8M (8:8:8)    |             |        |         |      |

| 119h   | -     | 1280x1024   | 32K (1:5:5:5)    |             |        |         |      |

| 11Ah   | -     | 1280x1024   | 64K (5:6:5)      |             |        |         |      |

| 11Bh   | -     | 1280x1024   | 16.8M (8:8:8)    |             |        |         |      |

| 81FFh  |       | Special Mod | le (see below fo | or details) |        |         |      |

**Note:** Starting with VBE version 2.0, VESA will no longer define new VESA mode numbers and it will no longer be mandatory to support these old mode numbers. OEM's who wish to add new VBE mode numbers to their implementations, must make sure that all new modes are defined with mode numbers above 0x100, However, it is highly recommended that BIOS implementations continue to support these mode numbers for compatibility with older software and add new mode numbers after the last VESA defined mode number). VBE 2.0-aware applications should follow the guidelines in Appendix 5 -Application Programming Considerations - for setting a desired mode.

**Note:** Mode 81FFh is a special mode designed to preserve the current memory contents and give access to the entire video memory. This mode is especially useful for saving the entire video memory contents before going into a state that could lose the contents (e.g., set this mode to gain access to all video memory to save it before going into a volatile power down state). This mode is required because the entire video memory contents are not always accessible in every mode. It is recommended that this mode be packed pixel in format, and a ModeInfoBlock must be defined for it. However, it should not appear in the

VideoModeList. Look in the ModeInfoBlock to determine if paging is required and how paging is supported if it is. Also note that there are no implied resolutions or timings associated with this mode.

**Note:** Future display resolutions will be defined by VESA display vendors. The color depths will not be specified and new mode numbers will *not* be assigned for these resolutions. For example, if the VESA display vendors define 1600x1200 as a VESA resolution, application developers should target their display resolution for 1600x1200 rather than choosing an arbitrary resolution like 1550x1190. The VBE implementation should be queried to get the available resolutions and color depths and the application should be flexible enough to work with this list. Appendix 5 gives a detailed summary of the way an application should go about selecting and setting modes.

### **VBE Far Pointers**

Throughout this specification references will be made to a pointer of the type 'vbeFarPtr'. This is a DWORD pointer that can have two different interpretations depending on whether the BIOS is being called via the real mode INT 10h software interrupt, or via the protected mode entry point. When functions are called via the real mode INT 10h software interrupt, a 'vbeFarPtr' will be a real mode segment:offset style pointer to a memory location below the 1Mb system memory boundary. When functions are called via the protected mode entry point, a 'vbeFarPtr' will be a valid 16-bit protected mode selector:offset style pointer, the selector of which may point to the base of the protected mode BIOS image loaded in memory, user data passed in to the protected mode BIOS or to the information blocks passed in to the protected mode BIOS. In any case the calling application and BIOS can simply reference the pointer as a 32-bit far pointer to access the data, but should avoid doing any real mode specific pointer arithmetic on the selector:offset values.

### **Obtaining the Protected Mode Entry Point**

Starting with VBE/Core 3.0, all the VBE functions are optionally accessible from 16-bit and 32bit protected mode applications and operating systems via a new 'Protected Mode Entry Point'. The protected mode entry point defines a special location that can be used to directly call the VBE functions as 16-bit protected mode code. The application or OS does not call the BIOS code directly from protected mode, but first makes a copy of the BIOS image in a writeable section of memory and then calls the code within this relocated memory block. The entry point is located within a special 'Protected Mode Information Block', which will be located somewhere within the first 32Kb of the BIOS image (if this information block is not found, then the BIOS does not support this new interface). The PM Info Block structure is defined as follows:

| PMInfoBlock struc |    |        |                                              |

|-------------------|----|--------|----------------------------------------------|

| Signature         | db | 'PMID' | ; PM Info Block Signature                    |

| EntryPoint        | dw | ?      | ; Offset of PM entry point within BIOS       |

| PMInitialize      | dw | ?      | ; Offset of PM initialization entry point    |

| BIOSDataSel       | dw | 0      | ; Selector to BIOS data area emulation block |

| A0000Sel          | dw | A000h  | ; Selector to access A0000h physical mem     |

| B0000Sel          | dw | B000h  | ; Selector to access B0000h physical mem     |

| B8000Sel          | dw | B800h  | ; Selector to access B8000h physical mem     |

| CodeSegSel        | dw | C000h  | ; Selector to access code segment as data    |

| InProtectMode     | db | 0      | ; Set to 1 when in protected mode            |

| Checksum          | db | ?      | ; Checksum byte for structure                |

| PMInfoBlock ends  |    |        |                                              |

To find the PMInfoBlock the application must scan the BIOS image looking for the appropriate signature. When a potential info block has been found, the application must then perform a checksum on the PMInfoBlock by adding the byte values of all entries in the block. If the block is valid, the sum of all bytes should be zero (the Checksum byte is used to force the result of the sum to zero).

**Note:** The protected mode entry point is optional, and may not be implemented in some VBE 3.0 BIOS'es. Also note that the VESA VBE/AF Accelerator Functions specifications provide an alternative protected mode environment, so application programmers looking for protected mode support may want to take a look at the VBE/AF specification.

Description of the **PMInfoBlock** structure fields:

The **Signature** field contains the special signature that is used to identify the PMInfoBlock located within the BIOS image.

The **EntryPoint** field contains the offset of the Protected Mode Entry Point from the start of the BIOS image. This offset is used to create a pointer for directly calling the protected mode entry point from both 16-bit and 32-bit protected mode code.

The **PMInitialize** field contains the offset of a function for initializing the protected mode BIOS code. The calling application must fill in the PMInfo block with valid selectors for protected mode operation, and then call the PMInitialize function before calling any functions via the protected mode entry point. The PMInitialize function is responsible for initializing any internal variables in the BIOS that may be different in protected mode such as internal pointers to font tables or other data (using the CodeSegSel selector to address variables within the code segment).

The **BIOSDataSel** field contains a protected mode selector that references a memory block of at least 600h bytes in length that will be cleared to all zeroes. This data block is used to provide a memory region that the BIOS can use for caching information across calls to the BIOS functions, and essentially will be used to emulate the first 600h bytes of low DOS memory which will no longer be present when running in protected mode. The real mode BIOS will always set this field to 0 so that real mode code can directly access the real BIOS data area. If the BIOS relies on certain values being present in this data block, the PMInitialize function should be used to fill in this block with default values for protected mode operation. This selector should be a 16-bit data selector with a minimum limit of 600h bytes with read/write permissions.

The **A0000Sel**, **B0000Sel** and **B8000Sel** field's contain selectors that point to the A0000h, B0000h and B8000h physical memory areas. These selectors are used by the protected mode BIOS code when it needs to access these physical memory areas (for clearing the screen, or accessing memory mapped registers etc.). The real mode BIOS will always set these fields to the real mode segment values initially so that real mode BIOS code can directly access these memory areas. These selectors should be 16-bit data selectors with a limit of 64Kb with read/write permissions (32Kb for B800Sel).

The **CodeSegSel** field contains a protected mode data selector that provides read/write access to the BIOS image loaded in memory. This selector can be used by the protected mode code during the PMInitialize function to self-modify portions of the code or internal pointers used during protected mode operation. The real mode BIOS will always set this field to a value of C000h so that real mode BIOS code can directly access the code segment. This selector should be a 16-bit data selector with a limit of 64Kb with read/write permissions (it is not executable).

The **InProtectMode** field is used to indicate to the BIOS code that it is running in protected mode. By default the real mode BIOS will set this value to 0 to indicate that it is running in real mode, and when the BIOS image has been relocated by the application, it will set this field to a '1'. The BIOS code can then use this field to determine if it is running in real mode or protected mode to fail functions that are not supported by the protected mode entry point.